Процессор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЙТВЛЬСТВУ

Союз Соаетскин

Социалистических

Республик (11) 6{ 2949 (61) Дополнительное к авт. сеид-ву(22) Заавлеио17.08.76 (21)2398707/18-24 с присоединением заявки ¹â€” (23) Приоритет— (43) Опубляковаио15.04.77.Бюллетень ph 14 (46) Дата опубликовании описании 2д И. т8.

2 (5l) М, Кл. т» 06 F 15/00

Гасударственный квинтет

Сеаате Мнннетрее СССР ее делам нэобретвннй н еткрытнй (53) УЛК 681 З2Л (088.8) (72) Авторы язобретеиия

Е. М. Зверев, В. С. Кокорин, А. Е. Костин н Б. В. Шевкопляс (71) Заявитель (54) ПРОЦЕССОР

Изобретение относится к вычислительной технике.

Одной нз задач, возникающих при построении вычислительных систем, является задача группового преобразования информации. Эта задача, в частности, возникает при проектировании многоканальных коммутационных систем.

Известно устройство (! ), представляющее собой блок-схему памяти для приема и передачи информации через совокупность линий связи. Оно содержит ряд кольцевых блоков памя10 ти, число которых равно числу блоков в знаке.

Каждый блок представляет собой, по существу, сдвиговый регистр с разрядностью, равной числу обслуживаемых каналов, например равной

l6. Каждый такой сдвиговый регистр замыкается в «кольцо» через соответствующий три - !5 гер буферного регистра, который, в свою очередь, также является сдвиговым регистром. ,Устройство управления осуществляет динамическое хранение информации, представленной параллельным кодом, а также последовательный ввод (или вывод) «очередного» бита в слово (иэ слова) на этапе его прохождения через буферный регистр. Таким образом, имеются два «взаимно перпендикулярных» и независимых направления сдвига: по <вертикали» вЂ” сдвиги в блоках памяти и по «горизон-д

2 тали» вЂ” сдвиги в буферном регистре. В таком устройстве наличие цепей сдвига приводит к усложнению схем.

Наиболее близким по технической сущности к данному изобретению является процесспр, содержащий блок управления, арифметическо-логическое устройство, регистр данных оперативной памяти, блок регистров общего назначения, блок регистров специального назначения, соединенные между собой двухсторонними связями, адресные и информационные входы и выходы блока управления, блока регистров специального назначения, регистра даннык опвративнод памяти соединены соответственно с адресными и информационными нходами и выходами процессора, выходы блока регистров специального назначения подключены к соответствующим входам арнфметическо. логического устройства (2t.

В этом процессоре обработка и н форм а ции производится в параллельном коде, а передача данных в телеграфные каналы связи осушествляется групповым способом в последовательном коде. Передача битов информации (знаковых посылок) в телеграфные каналы i вязи в прямом и обратном направлении осуществляется группами,. т.е. обслуживаемые телеграфные каналы связи объединнютсн н односкорост602949 ные группы с одинаковыми кодовыми характеристиками. Передача ведется по всем каналам связи данной группы в одном коде или разными кодами, у которых количество и длина стартовой, знаковых и стоповых посылок одинаковы; группа объединяет 16 каналов связи. Передача последовательных посылок знаков во все каналы связи данной группы ведется синфазно, т.е. все одноименные посылки передаются одновременно. Формирование группы посылок осуществляется центральным процессором программным способом. Выполняется это следующим образом.

Из оперативного запоминающего устройства (ОЗУ) выбирается слово, состояшее из двух байтов информации, подлежаших выдаче в два разных канала связи. Из этих байтов выделя- 15 ются соответствуюшие одноименные биты и посредством последовательных сдвигов передаются в один из регистров процессора в разряды, соетветствуюшие номерам тех каналов связи, в которые требуется передать выбран20 ные из ОЗУ байты.

Далее процедура повторяется для новых двух байтов информации и так до тех пор, пока не будет сформирована полная группа (16 разрядов) одноименных битов для передачи их в данную группу каналов связи. После выдачи сформированной группы битов в каналы процедура повторяется для последующих битов тех же передаваемых знаков, пока знаки не будут выданы полностью. Таким образом, осушествляется групповое преобразование кода знаков.

Недостатком такого процессора является невысокая производительность, связанная с необходимостью выполнения большого количества логических операций и обращений в ОЗУ.

Целью изобретения является повышение производительности процессора при работе с телеграфными каналами связи.

Поставленная цель достигается тем, что в предлагаемом процессоре выходы одноименных разрядов регистров блока регистров общего назначения соединены со входами соответствуюШих разрядов регистра данных оперативной 4g памяти, управляющий вход которого соединен с выходом блока управления.

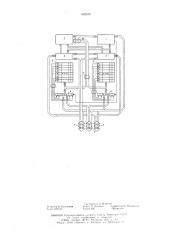

На чертеже представлена блок-схема процессора, где 1 — блок управления, 2 — двухсторонние связи с подключенными к ним арифметическо-логическим устройством 3, регист- 4 ром 4 данных оперативной памяти, блоком 5 регистров общего назначения, блоком 6 регистров специального назначения, 7 — цепи связи для обмена с внешними устройствами, подключенные к блоку 6 регистров специального назначения и к блоку 1 управления, 8 — цепи связи данных оперативной памяти, подключенные к регистру 4 и к блоку 1 управления, 9 — цепи связи адреса оперативной памяти, подключенные к блокам 6, l.

Процессор работает следующим образом.

Команда, поступающая из ОЗУ по связям 8, запоминается на регистре 4 и анализируется блоком 1 управления, который вырабатывает необходимую последовательность микрокоманд, управляющих пересылками информации по связям 2, 7, 8, 9 и работой арифметическо-логического устройства 3. В процессе выполнения команды блок 1 формирует исполнительный адрес операнда, хранящегося в ОЗУ, и пересылает этот адрес в блок 6. Блок 6 содержит регистр сигналов для связи с ОЗУ, на котором фиксируется текущее состояние процедуры обмена информацией между процессором и ОЗУ.

После пересылки адреса из блока 1 в блок 6 управление связями 8 и 9 осуществляется по асинхронному принципу «запрос-ответ». Операнд, выбранный из ОЗУ по исполнительному адресу, поступает по связям 8 в регистр 4 и далее в устройство 3, где осуществляется необходимая операция, соответствующая одной или нескольким микрооперациям устройства 3.

Результат операции по связям 2 передается из устройства 3 в один из регистров блока 5 или 6, или, если это определено кодом операции,— в ячейку памяти ОЗУ через регистр 4 и связь 8.

Обмен информацией с устройствами ввода/вывода происходит по связям 7, по которым передаются данные адреса и управляющие сигналы, l соответствующие определенному интерфеису.

Формула изобретения

Процессор, содержащий блок управления, арифматическо-логическое устройство, регистр данных оперативной памяти, блок регистров общего назначения, блок регистров специального назначения, соединенные между собой двухсторонними связями, адресные и информационные входы и выходы блока управления, блока регистров специального назначения, регистра данных оперативной памяти соединены соответственно с адресными и информационными входами и выходами процессора, выходы блока регистров специального назначения подключены к соответствующим входам арифметическо.-логического устройства, отличающийся тем, что, с целью повышения производительности при работе с телеграфными каналами связи, выходы одноименных разрядов регистров блока регистров общего назначения соединены со входами соответствуюших разрядов регистра данных оперативной памяти, управляюший вход которого соединен с выходом блока управления.

Источники информации, принятые во внимание при экспертизе:

1. Патент США № 3742466, кл. 340 — 173RC, 1973.

2. DS — 6 «Electronical Message Switching

System», 1974.

602949 (оставитеи Л. Жеренов

Текрел 0..1угован Корректор I I. Чала!к вии

Тираж 826 Поди и с июс

Рслактор H. Каменская

Заказ I85II45

ПНИИПИ Государственного комитета С.овета .Чинистроi (.е <.Р по делан изобретеallll и открьи ий

113035, Чосква. Ж-Зо, Рл гнскал аао. л. 4 о

Филиа.i 11! III «! !атент». г. Ужгорол, x.!. Iроектиаи. !