Запоминающее устройство

Иллюстрации

Показать всеРеферат

1,).„

О П И С А Й И- ЕИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (t l) 6О289в

Союз Советских

Социалистимеских

Республик (61 Дополнительное к авт. саид-ву (22) Заявлено 09.04.7 5. (21) 2123797/18-2 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.04.78. Бюллетень №1 (51) М. Кл.

Q 11 С 29/00

Государственный камитвт

Совета ввииистраа СССР

as данам ивееретвиий я аткрвпий (53) УДК 681.327. .66 (088.8), (45) Дата опубликования описания 25.03.78 (72} Авторы изобретения

В. К. Конопелько и В. В, Лосев (7l) Заявитель

Минский радиотехнический институт (54 ) ЗАПОМИНАЮЩЕЕ УСТРОИСТВО

Изобоетение относится к вычислительной технике, в частности к запоминающим уст ройствам.

Известно надежное полупроводниковое за, поминающее устройство со словарной организацией, содержащее накопитель, числовые шины которого соединены с выходами дешифратора строк, разрядные шины - с входами блоков считывания и контроля строк, выходы которых подключены соответственно к первййм 10 входам корректирующих сумматоров по модулю два и ко входам блэка «оррекции, выходами подключенного к вторым входам корректирующих сумматоров по модулю два, выходы которых являются выходами устройства, блок )5 о

«одирования, элементы И, шины записи, разрешения записи и управления 1 . Это устройство- характеризуется сложностью и невозможностью обращении к одному элементу памяти накопителя. Наиболее близким к изобретению 20 является запоминающее устройство, содержащее накопитель, первые разрядные шины котц . торого подключены к выходам дешифратора; столбцов, вторые разрядные шины - к первым входам блрка контроля строк и к первым вхо З5 дам блока считывания, первые числовые шины накопителя подключены к блоку контроля столбцов, вторые числовые шины — r. вьтходав4 дешифратора строк, выходы блоков контроля строк и столбцов подключены к входам первого блока коррекции, третьи числовые и раз рядные шины накопителя — ко: второму блоку коррекции, элементы И, сумматор по модулю два и управляющие шины (2). Однако это известное устройство недостаточно надежно.

Мелью изобретения является. повышение надежности. В описываемом устройстве это достигается тем, что в нем вторые paapspные шины накопителя подключены через

В первые элементы И к управляющим шинам и дешифратору столбцов, первые числовые шины накопители подключены через вторые элементы И к управляющим шинам и дешко. ратору строк, первые разрядные шины накопителя соединены с блоком считывания, выход которого подключен «о входу суммато-. ра по модулю два, другой вход которого соединен с выходом первого блока «оррекции, а выход — со вторым блоком коррек ция, входы которого подключены. к управляю3

602995 цшм шинам, а выходы — к блокам контроля строк и столбцов и к третьим разрядным и числовым шинам накопителя.

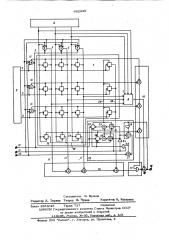

На чертеже приведена схема описываемого устройства. 5

Оно содержит накопитель 1, вторые числовые шины 2 которого соединены с выходами дешифратора 3 строк и входами вторых элементов И 4. Первые разрядные шины 5 накопителя соединены с выходами де- 10 шифратора 6 столбцов, управляющими входами 7 блока 8 считывания и входами первых эщэментов И 9. Входы апементов И соединены с шинами 10, 11 и 12 записи, разрешения записи и управлении, соответственно. 15

Выходы первых элементов И соединены со вторыми разрядными шинами 13 накопителя, входами блока 8 считывания и блока

14 контроля строк. Выходы вторых элементов И соединены с первыми числовыми шина-2О ми 15 накопителя и входами блока 16 конт троля столбцов. Выходы блоков контроля строк и столбцов соединены с входами первого блока 17 коррекции. Выход первого блока Коррекции соединен со входом сумматора 18 по модулю два, другой вход которого соединен с выходом блока 8 считывания. Выход 19 сумматора 18 по модулю два соединен непосредственно и через первый инвертор 20 с сигнальными входами вспомогательного триггера 21 второго блока 22 коррекции. Управляющий вход вспомогательного триггера 21 соединен непосредственно с управляющими входами триггеров

23 и через второй инвертор 24 — с первы35 ми входами двух сумматоров 25 по модулю два, первым входож элемента И 26 и шиной разрешения записи. Второй вход элемента И 26 соединен с выходом вспомогатель

40 ного сумматора 27 по модулю два. 1 1ервый вход вспомогательного сумматора соединен с шиной записи, а второй вход — с выходом вспомогательного триггера. Выход элеме та И 26 соединен с первыми входами двух

45 апементов И 28, Вторые входы элементов

И 28 соединены с шиной управления. Вторые входы сумматоров по модулю два соео динены с выходами триггеров. Сигнальные гходы триггеров и алементов И соединены

50 с третьими числовыми -шинами 29 накошмтеля (контрольных строк и столбца); третьи разрядные шины 30 соединены со вторым блоком коррекции.

В режиме записи информации на устройст . во подаются сигналы по шинам 10 и 12.

При этом происходит возбуждение вторых числовых шин 2 и первых разрядных шин

5 в соответствии с кодами адресов, поступивших на входы дешифраторов 3 и 6. Вторые разрядные шины 13 опрашиваемой строки накопителя 1 передают информацию в блок

14 контроля строк. Первые числовые шины

15 опрашиваемого столбца накопителя 1 передают информацию к блоку контроля столбцов 16. На выходе блока 8 считывания выделяется сигнал о состоянии опрашиваемого алемента памяти накопителя 1, который поступает на первый вход корректируюпиго сумматора 18, а на второй его вход поступает сигнал с выхода блока 17 коррекции.

Если информация, хранимая в опрашиваемом элементе памяти, искажена, на выходе блока 17 появляется единичный сигнал,т. е. выполняемая блоками 14 и 16 проверка на четность не соблюдается. Поэтому на кор-, ректирующем сумматоре 18 производится инвертирование сигнала с выхода блока 8 счиФ тывания, и он записывается во вспомогательный триггер 21 второго блока 22 коррекции. Сигнал с выхода вспомогательного триггера 21, поступая на вспомогательный сумматор 27 по модулю два, сравнивается с сигналом; записи. Если опрашиваемый элемент памяти должен изменить свое состояние, то на выходе вспомогательного суььматора 27 появляется единичный сигнал; в противном случае — нулевой сигнал. Однов ременно по третьим числовым 29 и разрядным 30 шинам происходит перезапись хранимой информации в элементах памяти контрольной строки и столбца в триггеры 23.

При поступлении сигнала разрешения записи и изменении на обратное состояние опрашиваемого элемента памяти накопителя

1 на выходе элемента И 26 появляется единичный сигнал, который открывает элементы И 28 контрольных строки и столбца.

При этом на выход элементов И 28 поступают инвертированные на сумматорах 25 сиг папы с выходов триггеров 23.

Таким образом, вместе с изменением состояния опрашиваемого элемента памяти накопителя 1 происходит изменение состояний Hs противоположное элементов памяти контрольных строки и столбца. Это позволяет сохранять контрольные условия четнос>тн числа единиц как в строке, так и в столбце.

Если опрашиваемый элемент памяти накопителя 1 не меняет своего состояния под воздействием сигнала записи, то на выходе элемента И 26 появляется нулевой сигнал, который закрывает элементы И 28; изменения состояния элементов памяти контрольных строки и. столбца не происходят, следовательно, сохраняется четность числа единиц в строке и столбце, В режиме считывания информации работа устройства происходит аналогично, однако сигналы записи и разрешения записи от602995 сутотзуют. При этом элементы И 4. 9 и 28— закрыты, а исправленный сигнал с выхода корректирующего сумматора 18 поступает на выход 19 устройства.

Формула изобретения

Запоминающее устройство, содержащее накопитель, первые разрядные шины которого1О подключены к выходам дешифратора столбцов, вторые разрядные шины — к первым входам бяока контроля строк и к первым входам блока считывания, первые числовые шины накопителя подключены к блоку контроля стол- 15 бцов, вторые числовые шины — к выходам дешифратора строк, выходы блоков контроля строк и столбцов подключены к входам первого блока коррекции, третьи числовые и разрядные шины накопителя — ко второму 20 блоку коррекции, элементы И, сумматор по модулю два, и управляющие шины, о т л и— ч а ю щ е е с я тем, что, с целью повынкния надежности устройства, вторые разрядные шины накопитеял подключены через вторые элементы И к управляющим шинам и дешифратору строк, первые разрядные шины накопителя соединены с блоком считывания, выход которого подключен ко входу сумматора по модулю два, другой вход которого связан с выходом первого блока коррекции, а выход — со вторым блоком коррекции, входы которого подключены к управляющим ши нам, а выходы — к олокам контроля строк и столбцов и к третьим разрядным и числовым шинам накопителя.

Источники информации, принятые во внимание при экспертизе:

1. "Микроэлектроника", Сб.ст. под ред.

Ф. И. Лукина, выл. 5. М., "Советское радио", 1972, с. 128-150.

2. Патент США % 3768071, кл. 340

146, 1973.

602996

Составитель В. Фроков

Редактор Л. Тюрина Техред Э. Чужик Корректор Н, Ковалева

Заказ 1863/48 Тираж 717 П одпис ное

UHHHIlH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра шская наб. д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4