Анализатор сигнала тактовый синхронизации

Иллюстрации

Показать всеРеферат

О П

Союз Советских

Социалистических

Республик (») 6ОЗ1ЗЗ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. Свил-ву (22!Заявлено 04.06.ig (21) 2368142 iF-09 с присоединением заявки N (23) Приоритет (43) Опубликовано15.04.78. Бюллетен- ХО14 (45) Дата опубликован(!я описания 7. М -,-г(и (51) M. Кл

Н 041 /О"

Гасударственный комитет

Совете Министров СССР па делам изааретений и открытий (53) УД1). 8- i.894. ,660. О (088,8) (72) Авторы изобретения

E. Г(. Папочкин, В. Jx. ЕВ )ок((х:ов и А..). Грпшуков (71) Заявитель (54) ЛНА,(1ИЗАТОР С11ГНА.Г1А T.c)ÊÒC ÂÑ6(СИНХРОН! !ЗА: 1!111

Изобретение относится к технике передачи дискретной информации и может использоваться в моделях систем с однократной и многократной фазовой модуляцией.

Известен анализатор сигнала тактовой с)!1хронизации, содержаший объединенные по Bxo(v основных и два дополнительных измерителя переходных помех, Выходы которых подключены к соответствуюшим входам коммутатора, ы выходы двух основных измерителей переходных помех через блок вычитания подключен к входу интегратора-сумматора (lj.

Однако известный анализатор обладае, большим временем вхождения B синхронизм.

Цель изобретения — сокрашение времени вхождения в синхронизм.

Для этого в предлагаемый анализатор сигнала тактовой синхронизации введены делитель частоты, два элемента И, элемент И;111 и формирователь коротких импульсов. при этом выходы коммутатора подключены соответственно к одному из входов двух элементов И и к входам элемента ИЛИ, выход которого через формирователь коротких импульсов подключен к другим входам двух элементов И, между выходами которых и выходом интеграторы-сумматора включен делитель частоты.

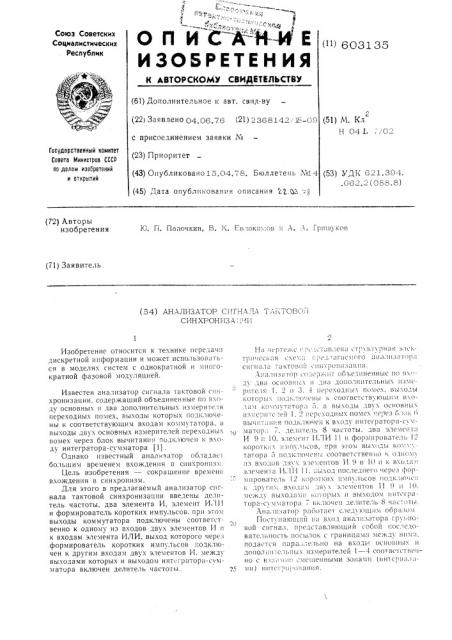

На |(ерте/кс го ставлены ст1>укл рная эле!. 1 i)!IЧСС!ic!я |. ХС)IЫ i:, ).,, )c! Гc!C)IГГО (!НЫ, IIIЗ;-)Т )! :>1

CII! Н<1,1 а TЫ КТОВ()й |. I !i Õ ()Oi(iiBc111!!I!.

Ана,(1(з|. .I !)p 00 c., 1;- !!т Ооъ! д!!ненныс (j()»х||ДУ,>Bc! ÎCI(ÎBH»! 1! ДВЫ ДОПОЛНИТЕЛЬНЫХ 1(ЗМЕр(!Гег!я 1, 2 ii 3. -1 переходи»(х помех, Выходы

КОТОРЫХ (!ОДКЛ:-ОЧ|>Hi>! b СОО ГВЕТСТВ (ОШН |1 В,0! c! 11 Ко I х! | ТВТОР Ы О, а ВЫ." ОДЫ .1ВХ".Х ОС НОВ НЬ(Х

1(змc )1! Олен 1. (IсpcхО" нь!х помех чс>!тез ii, lc)(x ()

Bb!c!!i; (iBi;ÿ подключеri к вх()д1 интегратора-сумматор,: 7, делитель 8 частоты. два элемеl! Гп

И 9 ". 1О, элемент И, 1И 11 и формирователь 2

КОРОТК(! Х 111! ПУ,) »СОВ> 11P!i Э ГОМ В»1 Х()ДЬ(! 0 |. |.", TBTOPci 5 ПОДКЛК)ЧЕНЫ СООтВЕтстВЕН О !. ОДНОМ) !

l3 вхо!oB двух элементов И 9 и !1! и к Вхо (ам элемеHT(j И,! И 1!..ыход последнег!) через фор)!1(рОВатсль ) коротк!Iх Ilчп | i»co !10.(h, 1!0 icii к другl!1; Вхс)дых! лв : элементов !1 .) 11 1(), ЕХК (| В>ЫХОД(!. >!! . О 0!>ЫХ !! ВЫХОДОХ(1! НТ|>! 1) Bтора-сумматора, Включе дегштель 8 ч()с): т(!.

Ан(1, f!(з()тО() раоотае с. 1(>д | ю(ц!DI Образо)l

Г1!)сг цаюший !|ы Вход анализатора грм! Новой с((гнал, предста вл я юши и собой i,îcëc:jîвательность посылок с границам. I между il!Iì:i. подается пара,,-елыю на входы оснкянь!х и допол н!тельных измерителей 1 — -1 соответстг>еi!но с Взы;.)!но смсшснными зонамп (iivjcp(i;!л;(>с М!1) Ин(СГ.М,! Оиап!!Я

603!35

Составитель В. Велякович

Техред О. Луговая Корректор Л. Грин нко

Тираж 805 Подписное (>сдактор Т. Янова

Заказ (878/56!

11((!ИП(! осударственного ко>яитега Соуп !янис>ров CC(P

11о делая изобретений и откр ья ий! !3035, Москва, Ж-35. Раушская иаб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Величина выходного напряжения л1обого из основных и дополнительнь!х измерителей 1-4 про»орциональна величине переходной помехи, которая минимальна у тех основных и дополн»тельных измерителей — 4, чьи зоны интегрирования попадают внутрь посылок. В случае точного синхронизма минимум переходной помехи обеспечивается на выходе основного измерителя 1 (2), осугцествляющего интегрирование сигнала в пределах своей зоны (минимум напряжения на выходах основных измерителей 1 или 2). Если же границы посылок попадают внутрь одной из зон, то выходное напряжение соответствующего основного измерителя

1 (2) окажется большим. Коммутатор 5 определяет номер зоны, интегрирование сигнала внутри которой обеспечивает минимум перехол- 15 ной ггомехи.

Если минимум находится в пределах первой или второй зо», то коммутатор 5 совместно с элементами И 9 и 10, элементами ИЛИ 11 и формирователем !2 не вырабатывает команду об изменении (перенумерации) зоч. 11роин20 тегрированная разность напряжений на выходах основных измерителей 1 или 2 является сигналом расс»»хронизаци» на выходе анализатора, B результате чего обеспеч»вастся основ»ой реж!1м с1ацио»арной подстройки границ

l1 O C bl, l O li, Пр» Ilo»l!:ган!»! гра»иц посылок в третью

»ли четверту>о зону (м»г»1мум напряжения на выхо 1е Ло»ол I»тельного измерителя 3 (4) на ол»ом нз выхоъов коммутатора 5 появляется полож»тс,.»>ное»апряженис, которос открывает олин»з эг!сментов И 9 (10), на другой вход которого в это же время !юступает короткий

I1o, Ioi!4IITE.,IьныЙ ID!!1> lbc, выраоотанный форм»рователсм 12 р» 1нздаче на него через элемс»1 !ЛИ 11 lol0 же по,1ож(пельного H ïðÿжсния. 1!м»ули>с a выходе элемента И 9 (10) ула»авл»виет триггер делителя 8, при котором

i! III»uI;;; »ерехолных пох1ех обеспечивается на основном измерителе 1 (2) . 1!роцесс перенумерации зон заканчивается после подачи импу.1ьса с элемента И 9 (!О) на управляюшие входы триггеров делителя 8, и время отработки сигнала коррекции определяется только быстродействием логических элементов.

Время вхождения в синхронизм в этом анализаторе в два раза меньше по сравнению с известным, так как определяется временем выработки сигнала на выходах основных и дополнительных измерителей 1 — 4 и временем выработки команды перенумерации зон коммутатором 5, элементами И 9 и 10, элементами

ИЛИ 11 и формирователем 12, чем достигается практически безынерционная отработка сигнала коррекции.

Формула изобретения

Анализатор сигнала тактовой синхронизации, содержащий объединенные по входу два основных и два дополнительных измерителя переходных помех, выходы которых подключены к соответствующим входам коммутатора, а выходы двух основных измерителей переходных помех через блок вычитания подключен ко входу интегратора-сумматора, отличающийся тем, что, с целью сокращения времени вхождения в

c è»>;ðoíèçì, введены делитель частоты, два элемента И, элемент ИЛИ и формирователь коротких импульсов, при этом выходы коммутатора подключены соответственно к одному из входов двух элементов И и ко входам элемента ИЛИ, выход которого через формирователь коротких импульсов подключен к другим входам двух элементов И, между выходами которых и выходом интегратора-сумматора включен делитель частоты.

Источники информации, принятые во внимание при экспертизе:

l. Авторское свидетельство ГССР ЛЪ 496688, кл. Н 04 L 7/02, 1974.