Импульсный стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИНА

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (и) 603970 (61) Дополнительное к авт. свид-ву (22) Заявлено1 5.1 1.76 (21) 2420274/24-07 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.04,78Бюллетень № 15 (45) Дата опубликования описания iQ. 04.78

2 (51) М. Кл.

С 05 F 1/58

Государственны и комитет

Совета Министров СССР оо делам изооретений н открытий (53) УДК621.316. .72 2.1 (088.8) (72) Авторы изобретения

А. Й. Гудков и А. Е. Ольсевич (71) Заявитель (54) ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

Изобретение относится к технике стабилизации питающих напряжений радиоэлектронной аппаратуры и может быть использовано в источниках питания, к которым предъявляются требования повышенной надежности.

Известен ключевой стабилизатор постоянного напряжения, содержащий регулирующий транзистор, индуктивно-емкостный фильтр с демпфирующим диодом, схему сравнения, усилитель сигнала ошибки и блок защиты (1).

Однако в таких стабилизаторах отсутствует защита регулирующего транзистора при включении. Поэтому для обеспечения надежной работы стабилизаторов при их включении необходимо выбирать регулирующий транзистор и дроссель фильтра с большим запасом по коллекторному току регулирующего транзистора и току нагрузки. Это, в свою очередь, приводит к увеличению габаритов и массы стабилизаторов.

Наиболее близким техническим решением является импульсный стабилизатор постоянного напряжения, содержащий включенные последовательно между первыми входным и выходным выводами регулирующий транзистор и дроссель индуктивно-емкостного фильтра с демпфирующим диодом, блок для управления, входом соединенный с выходными выводами, а выходом подключенный к базе регулирующего транзистора, и блок для защиты, состоящий из первого датчика тока, включенного между анодом демпфирующего диода и вторым входным выводом, второго датчика тока, включенного между вторым входным выводом и вторым выходным выводом, соединенным с конденсатором индуктивно-емкостного фильтра, и усилительного транзистора, база которого подключена к второму выходному выводу, кол 0 лектор соединен с входом блока для управления, а эмиттер — со средним выводом резистивного делителя напряжения, одно плечо которого подключено к первому выходному выводу (2).

Такой стабилизатор отличается низкой на? ? дежностью его работы как в нормальных, так и в аварийных режимах, а также при включении.

Это обусловлено тем, что при открывании регулирующего транзистора вследствие инерционности демпфирующего диода, к базо-эмиттерному переходу транзистора блока для защиты прикладывается обратное напряжение, практически равное входному, в течение времени рассасывания зарядов в базе демпфирующего диода. Так как допустимое обратное нап25 ряжение базо-эмиттерного перехода кремние603970

3 вых транзисторов не превышает единиц вольт, то последнее приводит к выходу из строя транзистора блока для защиты.

Цель изобретения — повысить надежность работы стабилизатора как в нормальных, так и в аварийных режимах (перегрузка, короткое замыкание в нагрузке), а также при включении.

Эта цель достигается подключением в схеме импульсного стабилизатора постоянного напряжения другого плеча резистивного делителя напряжения через дополнительно введенный диод к аноду демпфирующего диода и через дополнительно введенный резистор — к базе усилительного транзистора.

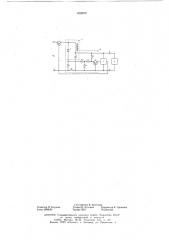

На чертеже представлена принципиальная электрическая схема стабилизатора.

Стабилизатор содержит последовательно соединенные регулирующий транзистор 1 и дроссель выходного индуктивно-емкостного фильтра 2 с демпфирующим диодом 3; к выходу стабилизатора подключена нагрузка 4 и вход блока 5 управления, выход которого соединен 20 с базой регулирующего транзистора 1. Кроме того, стаби |изатор содержит блок 6 защиты, первый датчик 7 тока, резистор которого включен в цепь демпфирующего диода 3, а второй датчик 8 тока на резисторе между входным и ,:25 выходным зажимами, резистивныи делитель напряжения на резисторах 9, 10 своей средней точкой подключен к эмиттеру усилительного транзистора 11, а одним из плеч через дополнительно введенные диод 12 и резистор

13 соединен соответственно с анодом демпфирующего диода 3 и одним из выходных выво дов.

Стабилизатор работает следующим образом.

При включении источника питания с напряжением U открывается регулирующий транзистор 1 и происходит накопление электромаг- 35 нитной энергии в дросселе выходного индуктивно-емкостного фильтра 2. Увеличение коллекторного тока регулирующего транзистора

1 вызывает возрастание падения напряжения на втором датчике 8 тока и отпирание уси40 лительного транзистора 11. Последний, воздеиствуя на блок 5 управления, обеспечивает запирание регулирующего транзистора 1. В дальнейшем насьпценное состояние усилительного транзистора 11 поддерживается суммарным падением напряжения на первом и втором датчи- 45 ках тока 7 и 8 до тех пор, пока ток разряда дросселя выходного индуктивно-емкостного фильтра 2 не снизится до минимального значения, при котором выполняется равенство

1- У7 + UR8 U 5.+ 1-1р + UR ( где U a — напряжение база-эмиттер открыто50 го усилительного транзистора 11;

1.1,

U R,, URs — падения напряжения на первом и втором датчиках тока 7 и 8;

Г, — падение напряжения на резисторе 10.

После запирания усилительного транзистора 11 снова включается регулирующий транзистор 1. Вследствие инерционных свойств демпфирующего диода 3 в течение времени рас- 60

4 сасывания зарядов в его базе к демпфирующему диоду 12 прикладывается обратное напряжение, запирающее его. При этом к базоэмиттерному переходу усилительного транзистора 11 прикладывается обратное напряжение, определяемое суммарным падением напряжения на резисторах 10 и 13. loc ie запирания демпфирующего диода 3 импульс коллекторного тока регулирующего транзистора 1 снижается до значения, определяемого запасом электромагнитной энергии дросселя выходного индуктивно-емкостного фильтра 2 в момент запирания усилительного транзистора 11, и начинается вновь накопление электромагнитной энергии в дросселе выходного индуктивно-емкостного фильтра 2. Далее импульсный режим включения стабилизатора продолжается аналогично описанному по достижению квазиустановившегося режима. С этого момента блок

6 защиты не оказывает влияния на блок 5 управления. Аналогично происходит работа стабилизатора при перегрузках и коротких замыканиях в нагрузке 4.

Благодаря наличию диода 12 и резистора

13 обратное напряжение на базо-эмиттерном переходе усилительного транзистора 11 не превышает допустимых значений во всех режимах работы импульсного стабилизатора, что повышает его надежность.

Формула изобретения

Импульсный стабилизатор постоянного напряжения, содержащий включенные последовательно между первыми входным и выходным выводами регулирующий транзистор и дроссель выходного индуктивно-емкостного фильтра с демпфирующим диодом, блок для управления, входом соединенный с выходными вы— водами, а выходом подключенный к базе регулирующего транзистора, и блок для защиты, состоящий из первого датчика тока, включенного между анодом демпфирующего диода и вторым входным выводом, второго датчика тока, включенного между вторым входным выводом и вторым выходным выводом, соединенным с конденсатором выходного индуктивно-емкостного фильтра, и усилительного транзистора, база которого подключена к второму выходному выводу, коллектор соединен с входом блока для управления, а эмиттер — со средним выводом резистивного делителя напряжения, одно плечо которого подключено к первому выходному выводу, отличающийся тем, что, с целью повышения надежности, другое плечо резистивного делителя напряжения через дополнительно введенный диод подключено к аноду демпфирующего диода и через дополнительно введенный резистор — к базе усилительного транзистора.

Источники информации, принятые во внимание при экспертизе:

1: Авторское свидетельство СССР № 418842, кл. G 05 F 1/56, 1972. б

2. «Полупроводниковая электроника в технике связи». Связь, подписано к печати в марте 1976, вып. 717, с. 106.