Устройство для сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

рте)н (ро ) лкотенет а,,л)е "

Ът

Союз Советских

Социалистических

Республик

ОП ИСА

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву „yе444180 (22) Заявлено 04.11.75(21)2187369/18 24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.04.78, Бюллетень № 15 (45) Дата опубликования описания 10 04, ) 8

2 (51) М. Кл.

Я 06 F 7/04

Государственный комитет

Совета Министров СССР

)lo делам изоаретений н открытий (53) УДК 681.825.66 (088.8) (72) Авторы изобретения

K. Д. Пописский и В. X. .!ингауз (71) Заявитель

Научно-исспедоватепьский и опытно-конструкторский институт автоматизации черной металлургии (54) УСТРОЙСТВО ДЛЯ CPA BHEHI ДВОИЧНЫХ ЧИСЕ.)>!

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах дискретного управлен ия.

Известно устройство для сравнения двоичных чисел по основному авт. св. ¹ 444180.

Этому устройству свойственно невысокое быстродействие, так как в нем формируются одновременно четыре результата сравнения путем вычитания единичныx импульсоB из всеx чисел.

1О

Целью изобретения является повышение быстродействия устройства.

Достигается это тем, что устройство по авт. св. № 444180 снабжено поразрядны>ми узлами управления стиранием и записью, каждый из которых состоит из пяти элементов И, четырех элементов ИЛИ и элемента НЕ., при чем в каждом узле управления стиранием и записью выход элемента HE подключен к одному из входов первого элемента И, соединенного выходом с одним из входов первого и второго элементов ИЛИ, к одному из входов второго элемента И, выход которого подкл)очен к одному из входов третьего и второго элементов ИЛИ, и к одному из входов третьего и четвертого элементов И, а вход элемента 25 чьь, ц „ )

Н И Е (11) возввв

HE coe,zI))I(.)) с выходом «exB(.plo) o э,>еменT I

ИЛИ, вх(>д) I )(oTopo) )0K:))o )BH) ) к и»)ходам пятых элементов И всех поразрядных узлов управления c11)ранием и записью. при )см )срвый вход каждого пятого элемента И соединен с инверсным выходом триггера .1(lillloi o разряда, а второй вход — с выходом первого элемента ИЛИ соответствующе)о счетч«ка, дру гие входы первого, второго и третьего элемсllТоВ И подключены к инверсному выходу и:(>рого управляю)пего триггера, прямой выxo;1 (()торого соединен с други)(1 входом ч(тв(ртогo элемента И, третий вход первого эдеме)п;1 1!"

СОЕДИНЕН С ПряМЫМ, а трЕтИй BX();1, ВтОрОГО -э,н— мента И вЂ” с HHB(">сными выходами иервог( управляющего триг" à, выходы сед»мых элементов И соединены с другими входам): 11(-;.вого и третьего элементов ИЛИ, выходы ко1:— рых подключены к входам сброса трн)герои данного разряда соответственно первого и второго реверсивных счетчиков, а входы упраилеHHH триггерами данного разряда первого и BT()рого реверсивных счетчиков, первого, второго, третьего и четвертого суммирующих счетч))кои соединены с выходами соответственно втор(>го и первого элементов И, второго элемента ИЛИ, третьего и четвертого элементов И и элем Hò(I

НВ, и )vog которого подключе)) к входам сбро603986 са триггеров данного разряда счетчиков сравниваемых чисел.

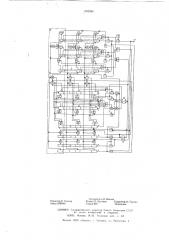

На чертеже представлена функциональная схема устройства.

Устройство содержит вычитающие счетчики

1, 2 и 3 сравниваемых чисел с вычитающим счетным входом, первый 4 и второй 5 реверсивные счетчики; первый 6 и второй 7 суммирующие счетчики (минимальной и максимальной разности) с суммирующим счетным входом; третий 8 и четвертый 9 суммирующие счетчики (наименьшего и наибольшего чисел) с суммирующим счетным входом; первый элемент ИЛИ

10: дифференцирующие цепи 11; первый элемент И 12, генератор счетных импульсов 13; второй элемент И 14; второй элемент ИЛИ 15, шестой элемент ИЛИ 16; восьмой элемент И

17; четвертый элемент ИЛИ 18; пятый элемент ИЛИ 19; третий элемент И 20; седьмые элементы И 21, 22; четвертый элемент И 23; первый управляющий триггер со счетным входом 24; второй управляющий триггер 25 с раздельными входами; третий элемснг ИЛИ 26, пятый и шестой элементы И 27 и 28, девятый десятый и одиннадцатый элементы И 29, 30 и

31, поразрядные узлы управления стиранием и записью информации 32, состоящие из четвертого элемента ИЛИ ЗЗ, элемента НЕ 34, первого и второго элементов И 35, 36, первого, третьего н второго элементов ИЛИ 37, 38, 39, третьего и четвертого элементов И 40, 41 и пятых элементов И 42, 43, 44; входную клемму 45 устройства.

Устройство работает следующим образом.

В исхо.3ном состоянии сравниваемые числа записаны Е3 счетчики 1, 2, 3. Прп этом есть сип;алы на выходах каждого из элементов

ИЛИ 10. следовательно, есть cvE EEaлы на вторых входах каждого из элементов И !2, 42 и на выходе элемента ИЛИ 15, а также есть сигналы на вторых входах элементов И 17 и 31.

Первый и второй управляющие триггеры установлены в «О». В каждом из разрядов счетчиков 4 и 5 записаны «1».

После поступления на клемму 45 разрешающего сигнала, который сохраняется в течение всего времени сравнения, импульсы от генератора 13 через элемент И 14 и элементы

И 12 поступают на информационные входы счетчиков 1,2 и 3, уменьшая их содержимое.

Одновременно импульсы чер.з элементы И 14 и 31 поступают в счетчик 9 наибольшего числа и подсчитываются в пем, С выхода элемента И 31 импульсы поступают на второй вход

30. Поскольку при подаче на клемму 45 разрешающий сигнал устанавливает триггер 25 в «1» т. е. появляются сигналы на вторых входах элементов И 41 и на первом входе элементов

И 30, импульсы через элемент И 30 проходят в счетчик 8 наименьшего числа и подсчитываются в нем.

В том случае, если в процессе вычитания единиц из счетчиков 1, 2, 3 в их одноименных разрядах одновременно окажутся записанными единицы, исчезнут сигналы на первых входах, следовательно, на выходах всех элементов И

42 данного разряда. В результате на выходе элемента НЕ 34 появляется сигнал, который стирает содержимое этого разряда во всех счетчиках 1, 2, 3 и подает единицу в этот разряд счетчиков 8.

После некоторого количества чередований стирания равных разрядов с вычитанием единиц содержимое одного (или нескольких) счетчиков 1, 2, 3 становится равным нулю. Исчезает сигнал с выхода соответствующего элемента

ИЛИ 10 и, следовательно, сигналы на вторых щ входах элементов И !2 и 42. Прохождение импульсов в эти счетчики прекратится, а инверсные выходы триггеров этих счетчиков отключатся от элементов ИЛИ 33.

Исчезновение сигнала на выходе элемента

И 0 фиксируется элементом ИЛИ 26, импульс с выхода которого перебрасывает триггер 25 в исходное состояние, в результате чего появляется сигнал на первом входе элемента И 29, вторых входах элементов И 35, 36 и 40, снимается сигнал с первого входа элемента И 30, 2В и подсчет импульсов в счетчике 8 наименьшего числа прекращается. Импульс с выхода элемента ИЛИ 26 перебрасывает триггер 24. Появляется сигнал на его прямом выходе, следовательно, на третьих входах элементов И 35, втором входе элемента И 27 и первом входе элемента И 22. Импульс с выхода элемента

ИЛИ 26 подается на вторые входы элементов

И 21 и 22, проходит через элемент И 22, очищая счетчик 5, в результате чего закрывается элемент И 23.

Поскольку появился сигнал на первом входе элемента И 29, счетные импульсы с выхода элемента И 31 через элемент И 29 начинают поступать на информационный вход счетчика 7 максимальной разности и подсчитываются в нем.

Одновременно счетные импульсы с выхода эле35 мента И 29 поступают на первые входы элементов И 27 и 28. Ввиду того, что есть сигнал на втором входе элемента И 27 и с выхода элемента ИЛИ !8 на первом входе элемента

И 20, импульсы через элементы И 27 и 20

4О проходят на суммирующий вход счетчика 5 I подсчитываясь в нем. При этом элемент И 23 открывается и импульсы поступают на вычитающий вход счетчика 4, уменьшая его содержимое, а также через элемент ИЛИ 16 подсчитываются в счетчике 6 минимальной разнос45 ти.

В том случае, если в одноименных разрядах оставшихся ненулевых счетчиков 1, 2, 3 оказываются записанными единицы, сигналы с выхода соответствующих элементов НЕ 34 стирают содержимое этих разрядов во всех вычитающих счетчиках 1, 2, 3, в первом реверсивном счетчике 4 и подают единицы в эти разряды счетчиков 5, 6, 7 и 9.

После того, как число, следующее за наименьшим из сравниваемых чисел, обращается в нуль, исчезает сигнал с выхода одного из элементов ИЛИ 1О и закрывается соответствующий элемент И 12, прекращая поступление вычитающих импульсов в данный счетчик.

Исчезновение сигнала на выходе ИЛИ 10 фиксируется элементом ИЛИ 26, импульс с вы60 хо 3,а которого подтверждает состояние тригге603986 ра 25 и перебрасывает триггер 24. В результате появляются сигналы на первом входе элемента И 21, втором входе элемента И 28 и третьих входах элементов И 36. Импульс с выхода элемента ИЛИ 26 поступает на второй вход элемента И 21, очищая счетчик 4, благодаря чему закрывается элемент И 20, и, проходя через элемент И 17, очищает счетчик 6 минимальной разности.

Импульсы с выхода элементов И 28 и 23 подсчитываются в первом реверсивном счетчике

4 и через элемент ИЛИ 16 — в первом суммирующем счетчике 6 и вычитаются из содержимого второго реверсивного счетчика 5. При одновременном появлении единиц в одноименных разрядах ненулевых вычитающих счетчиков 1, 2, 3 происходит, как описано выше, стирание содержимого этих разрядов во всех этих счетчиках, в счетчике 5 и подача единиц в эти разряды счетчиков 4, 6, 7 и 9.

Если текущее значение разности сравниваемых чисел меньше или равно уменьшаемому, записанному в одном из реверсивных счетчиков 4 и 5 (в данном случае в счетчике 5), то в схеме в отрезок времени от момента обращения в нуль одного (наименьшего) из сравниваемых чисел, зафиксированного элементом

ИЛИ 26, до момента обращения в нуль следующего из сравниваемых чисел, также зафиксированного элементом ИЛИ 26, никаких переключений не происходит. Эта разность, как наименьшая из всех предыдущих, окажется записанной в суммирующем счетчике 6. Если же очередная текушая разность больше уменьшаемого, то в момент их равенства содержимое счетчика уменьшаемого (в данном случае счетчика 5) станет равным нулю, элемент И 23 закрывается и дальнейшее поступление импульсов в устройство прекратится. Предыдущее зна-, чение разности в качестве наименьшего из всех сравниваемых к этому моменту будет восстановлено в 6 и запомнено в 4 счетчиках.

После того, как обратится в нуль наибольшее из всех чисел, исчезнет сигнал с выхода элемента ИЛИ 15, т. е. сигнал на вторых входах элементов И 31 и 17, поступление импульсов в суммирующие счетчики 7 и 9 прекратится, а импульс с выхода элемента ИЛИ 26 не погасит счетчик 6. Таким образом, в счетчиках 8 и 9 записаны наименьшее и наибольшее из сравниваемых чисел, в счетчиках 6 и 7 — минимальная и максимальная разности чисел.

Оборудование устройства для сравнения поразрядными узлами управления стиранием и записью информации с соответствующими связями позволяет значительно сократить время сравнения. Процесс сравнения ускоряется примерно в 10 раз.

Форл ула изобретения

1в Устройство для сравнения двоичных чисел по авт. свид. № 444180, отличающееся тем, что, с целью повышения быстродействия, оно снабжено поразрядными узлами управления стиранием и записью, каждый из которых состоит из пяти элементов И, четырех элементов ИЛИ

15 и элемента НЕ, причем в каждом поразрядном узле управления стиранием и записью выход элемента НЕ подключен к одному из входов первого элемента И, соединенного выходом с одним из входов .первого и второго элементов

ИЛИ, к одному из входов второго элемента И, выход которого подключен к одному из входов третьего и второго элементов ИЛИ, и к одному из входов третьего и четвертого элементов И, а вход элемента HE соединен с выходом четвертого элемента ИЛИ, входы которого подключены к выходам пятых элементов И всех поразрядных узлов управления стиранием и записью, причем первый вход каждого пятого элемента И соединен с инверсным выходом триг гера данного разряда, а второй вход — с выходом первого элемента ИЛИ соответствуюшего счетчика, другие входы первого, второго и третьего элементов И подключены к инверсному выходу второго управляющего триггера, прямой выход которого соединен с другим входом четвертого элемента И, третий вход первого

З5 элемента И соединен с прямым, а третий вход второго элемента И вЂ” с инверсными выходами первого управляющего триггера, выходы седьмых элементов И соединены с другими входами первого и третьего элементов ИЛИ, выходы которых подключены ко входам сброса триггеров данного разряда соответственно первого и второго реверсивных счетчиков, а входы управления триггерами данного разряда первого и второго реверсивных счетчиков, первого, второго, третьего и четвертого суммируюших счетчиков соединены с выходами соответственно второго и первого элементов И, вто рого элемента ИЛИ; третьего и четвертого элементов И и элемента НЕ, выход которого подключен ко входам сброса триггеров данного разряда счетчиков сравниваемых чисел.

603986

ЦНИИПИ Государственного комитета Совета Минисгров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород. ул. Проектная, 4

Редактор Е. Гончар

Заказ 2089/40

Составитель В. Белкин

Техред О. Луговая Корректор И. Гоксич

Тираж 826 Подписное