Устройство для выбора среднего по величине двоичного числа

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Севоз Советскик

СО4иалисти ческиx

Республик (!1) 603994 (61) Дополнительное к авт. свид-ву (22) Заявлено 110775(2I) 2156071/18-24 с присоединением заявки,% (23) Приоритет (43) Опубликовано 2504.78. Бюллетень № 15 (51) М. Кл, G06 Р

11/00;

10/00

Н 05 К

Гвврдврвтввввый ввавтвт

6вввта твввввтрав 666р вв дввва ввйрвтвввр в втврытвд ()

681.325.61 {088,8) (45) Дата опубликования описания 200478 (72) / вторы изобретения

А.В. Бондарович, В.Н. Иакаренко и Ю.Е. Ромащенко (7!) Заявитель

{54) УСТРОИСТВО ДЛЯ ВЫБОРА СРЕДНЕГО ПО ВЕЛИЧИНЕ

ДВОИЧНОГО ЧИСЛА

Изобретение относится к области вычислительной техники и автоматики и может быть использовано при построении систем повышенной надежности.

Известно устройство для выбора сред- 5 него по величине двоичного числа из поступающих на входы последовательных кодов, содержащее мажоритарный элемент, входные триггеры, триггеры..выдачи единиц и триггеры выдачи нулей, управляемые элементами И анализа единицы, элементами И анализа нулей и шинами синхронизации, начальной установки и подготовки приема информации (1).

Недостатком его является невозможность представления на выходе в прямом коде среднего по величине числа, если входная информация представлена в прямом или обратном коде, Наиболее близким к предложенному по;Я(» технической сущности является устройство для выбора среднего по величйне числа, содержащее элемент ИЛИ, выход которого соединен со входом мажоритарного элемента, первый вход- с выходом 25 элемента И выдачи числа, ко входу которого подключен нулевой выход триггера анализа нулей,;второй вход элемента ИЛИ соединен с единичным выходом триггера анализа единиц, элемент И 30 анализа нулей, первый вход которого соединен с выходом мажоритарного элемента, второй — через инвертор входных сигналов с соответствующим информационным входом устройства, элемент И анализа единиц, первый вход которого через инвертор выходных сигналов соединен с выходом мажоритарного элемента, второй- с нулевым выходом триггера анализа нулей, третий- с соответствую щим информационным входом устройства, и общую шину начальной установки, подключенную к нулевым. входам триггеров (2).

Недостатком этого устройства является невозможность представления на выходе в прямом коде среднего по значению числа, если информация поступает одновременно. на одни входы в прямом, а на другие — в обратном коде.

Целью изобретения является расширение области применения устройства.

Это достигается тем, что в предложенное устройство введены элемент И прямого кода, элемент И обратного кода, элемент ИЛИ выдачи нулей, элемент .ИЛИ выдачи единиц, элемент И анализа нулей обратного кода, элемент И анализа единиц обратного кода, иннертор входных сигналов обратного кода, инЪертор,входных1 сигналов обратного йод " инвертор числа, шина прямого коДа, шина обратного кода, элемент

ИЛИ числа, выход которого соединен со вторым входом элемента И выдачи числа„ 5 пбрвЫЙ вход- с выходом элемента и обратного кода, второй- с выходом элемента И прямого кода, единичный вход триггера анализа нулей соединен с выходом элемента ИЛИ выдачи нулей, пер- 10 вый вход которого соединен сь выходом элемента И анализа нулей обратного кода, второй- с выходом элемента И анализа нулей, а единичный вход триггера анализа единиц соединен с выходом зле- д мента ИЛИ выдачи единиц, первый вход которого соединен с элементом И анализа единиц обратного кода, второйс элементом И анализа единиц. Шина прямого кода подключена ко второму эхо-20 ду элемента И прямого кода, к третьему входу элемента И анализа нулей и к четвертому входу элемента И анализа единиц, а шина обратного кода подключена ко второму входу элемента И обрат- ного кода, к третьему входу элемента

И анализа нулей обратного кода и к четвертому входу элемента И анализа единиц обратного кода. Выход мажоритарного элемента соединен с первым входом элемента И аналиэа нулей обратного кода и через инвертор выходных сигналов обратного кода — с первым входом элемента И анализа единиц обратного кода, а каждый информационный вход устройства соединен через инвертор чис-3 ла с первым входом элемента И обратного кода, с первым входом элемента И прямого кода, со вторым входом элемента И анализа нулей обратного кода и через инвертор входных сигналов об- 40 ратного кода — с третьим входом элемента И аиализа единиц обратного кода,. причем, нулевой выход триггера анализа нулей соединен со вторым входом эле.мента И анализа единиц обратного кода. 48

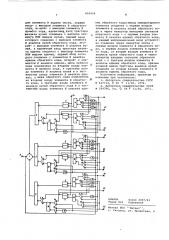

На чертеже представлена структурная схема устройства, например, на три входа (ийжний. средний и верхний) .

Предложенное устройство содержи . мажоритарный элемент Х, элемент ИЛИ ?, 6 элементы И 3 выдачи числа, триггеры 4 анализа нулей,. триггеры 5 анали- за единиц, элементы И б анализа нулей, элементы Й 7 анализа единиц, выход 8 устройства,-иинерторы 9 ныходных сиг 3« налов, информационные входы 10, инвер-" тори 11 входных сигналов, иннерторы

12 числа, элементы ИЛИ 13 числа, элементы И 14 прямого кода, элементы .И 15 обратного кода, элементы ИЛИ 16 выдачи нулей, элементы ИМИ 17 выдачи единиц, элементы И 18 анализа нулей обратного кода, элемент И 19 ана-, лиза единиц обратного кода, иннерторы

20 входных.сигналов обратного кода, кивер-..оры 21 выходных сигналов обрат» 65 ного кода, шины 22 обратного кода, шины 23 прямого кода, общую для всех триггеров шину 24 начальной установки.

Ус-..ройство для выбора среднего по величине .числа работает следующим об" разом.

На информационные ьходы 10 от оотвестнующих каналов, информация которых обрабатывается предложенным устройс ном, подаются сигналы н последовательном двоичном прямом или обратном коде, начиная со старших разрядон. Будем считать, что единице н разряде кода соответствует высокий потенциал, нулю" низкий.

В исходном состоянии после подачи сигнала по шине 24 начальной установки на нуленом выходе триггеров 4 ана-лиза нулей присутствует высокий потенциал, а на. единично«м выходе триггеров

5 анализа единиц- низкий. При этом разрешено прохождение старших разря-дон входных сигналон на входы мажоритарного элемента 1 при подаче сигнала по шине 23 прямого кода- для единичных сигналоз прямого кода, при подаче сигнала по шине 22 обратного кода- для нулевых сигналов обратного кода.

Дальнейшую работу устройства рассмотрим на примере подачи на его входы произвольных сигналов. Предположим, что на нижний информационный вход 10 устройства подается прямой код 110111, на средний- обратньй код 010106, а на верхний- обратный коц 160010, что соответствует значениям двоичных чисел н прямом коде 11011, 10101,1 и 011101 соответственно.

При подаче на информационные входы

10 устройства старших разрядон приведенных кодов единичный сигнал левого канала и,сигнал по левой шине 23 прямого кода приводят к срабатыванию левого элемента И 14 прямого кода. Выходной сигнал левого элемента И 14 прямого кода через .левый элемент ИЛИ 13 †.ясла и единичный сигнал нулевого выхода. левого триггера 4 анализа нулей приводит к срабатыванию левого элемента К 3 выдачи числа, выход которого через нижр-.ий элемент ИЛИ 2; ос";упае на нож °vèé вход мажоритарного элемента 1.

Нуль среднего канала =.врез средний инвертор 1? числа и си.нал |,.о среr,ê =й шине 22 обратного кода приводит к с абатынанию среднего злемента И 15 обратного кода. Выхоцной сигнал среднего элемента И 15 обратно!"о кода через средний элемент или 13 чч=ла и единичный сигнал нулезого нь.хода среднего триггера 4 приноцит к срабатыванию среднего элемент:;. И 3 и ньдачи числа„ выход которого через средний элемент

ИЛИ 2 поступает на срецний вход мажср".7àðíoão элемента 1.

В ре эул ьт ате Г(О".аления сигналoн на нижнем и среднем нхоцах мажоритар"

603994 дом элемента И выдачи числа, первый вход- с выходом элемента И обратного кода, второй- с .выходом элемента И прямого кода, единичныХ вход триггера анализа нулей соединен с выходом элемента ИЛИ выдачи нулей, первый вход которого соединен с выходом элемента

И анализа нулей обратного кода, второй- с выходом элемента И анализа нулей, а единичный вход триггера анализа единиц соединен с выходом элемента

HJIH выдачи единиц, первый вход которого соединен с элементом И анализа единиц обратного кода, второй- с элементом И анализа единиц, шина прямого кода подключена ко второму входу эле!

5 мента И прямого кода, к третьему входу элемента И анализа нулей и к четвертому входу элемента И анализа единиц, а шина обратного кода подключена ко второму входу элемента И о ратно- 20 го кода, к третьему входу элемента И анализа нулей обратного кода и к четвертому входу элемента И анализа единиц обратного кода;выход мажоритарного элемента соединен с первым входом элемента И анализа нулей обратного кода и через инвертор выходных сигналов обратного кода — с первым входом элемента И анализа единиц обратного кода, а каждый информационный вход устройства соединен через инвертор числа с первым входом элемента И обратного кода, с первым входом элемента И прямого кода, со вторым входом элемента И анализа нулей обратного кода и через инвертор входных сигналов обратного кода — с третьим входом элемента И анализа единиц обратного кода, причем нулевой выход триггера анализа нулей соединен со вторым входом элемента И анализа единиц обратного кода.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

9 447714, & 06 У 11/00, 1972.

2. Авторское свидетельство СССР

Р 394790, кл, G 06 7 11/00, 1971.

ЦНИИПИ Заказ 2097/41

Тираж 826 Подписное

Филиал ППП Патент, Г. ужгород ул. Проектная