Цифровой коррелятор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (1!) 603998

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Д,ополннтельное к авт. свид-ву (22) Заявлено 080775 (21) 2155612/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 2504.78Бюллетень № (5l) М. Кл.

06 15/34

Гоеудоретооннын ноантот

Совета еенонотроо 666Р но донам наобротев6 н отнрытно (53) УДК

681 323 (088 8) (45) Дата опубликования описания 19.0478

Г.Г. Хачиян, Ю.Г. Кожевников, М.И. Андреев и A.A. Ураэов (72) вторье изобретения (7l) ЗаяантЕЛЬ Южное морское научно-производственное геолого-геофизическое объединение Южморгео (54) 11ИФРОВОЙ КОРРЕЛЯТОР

Изобретение относится к области геофизики и вычислительной техники и предназначено для корреляционного анализа сейсмических и другого рода сигналов в реальном масштабе времени. 5

Известны цифровые корреляторы, осуществляющие корреляционную обработку сигналов в реальном масштабе времени

1). Они содержат блок буферной памяти, блок управления, блоки оператив- т0 ной памяти, коммутатор режима работы, блок умножения и интегратор.

Известные корреляторы часто производят корреляционную обработку цифровой информации, поступающей на блок »5 памяти со строго определенной стабильной скоростью.

Наиболее близким по технической сущности к предлагаемому является кор" релятор, содержащий блок управления, З» первый выход которого подключен к входам первого и второго блоков оперативной памяти, к управляющим входам блока умножения и интегратора, а второй выход соединен с управляющим входом блока буферной памяти, информационные входы которого являются входами коррелятора, а первый и второй выходы подключены соответственно н информационным входам первого и второго блоков

30 оперативной памяти, выходы которых соединены соответственно с первым и вторым входами блока умножения, выход которого подключен к входу интегратора, третий выход блока буферной памяти соединен с первым входом коммутатора режима работ, второй вход которого соединен с первым выходом генератора тактовых импульсов, а выход подключен к входу блока управления Д), Опорный и сейсмический сигналы с магнитного носителя поступают в блок буферной памяти и далее — на входы блоков оперативной памяти. После загрузки обоих блоков оперативной памяти в режиме обработки информации выборки сигналов перемножаются блоком умножения и усредняются интегратором.

Блок управления управляет режимами обработки сигналов и осуществляет временной сдвиг сейсмйческого сигнала относительно опорного. Записанный. на магнитном носителе вспомогательный сигнал определенной частоты через третий выход блока буферная памяти поступает на вход ко .мутатора режима работ, где он сравнивается с сигналом от кварцевого генератора. Сигнал рассогласования подстраивает частоту генератора тактовых импульсов, выход б03998 которого соединен со вторым входом коммутатора режима работ. Подстроенные таким образом тактовые импульсы поступают далее на вход блока управления, где формируются все вспомогательные сигналы, необходимые для нормальной работы коррелятора. Слежение и подстройка, необходимость которых обусловлена нестабильностью скорости движения магнитного носителя информации, осуществляются в пределах не болееЪ5%.

При большей нестабильности сигнал рассогласования достигает величины, при которой коммутатор далее не корректирует частоту тактовых импульсов и обработка сигналов осуществляется с постоянной скоростью, независимо от величины нестабильности скорости движения магнитного носителя.

Блоки оперативной памяти выполнены на динамических регистрах сдвига, на МОЛ-транзисторах, которые характеризуются большим быстродействием, но ограниченным временем хранения информации без разрушения при прекращении тактиронания. 25

Однако этот коррелятор обладает ограниченным диапазоном подстройки скорости обработки информации из-эа нестабильности скорости движения магнитного носителя. Этот диапазон определяет-, ся не пределами значений нестабильнос- ти скорости движения носителя,а возможностями самой следящей системы коррелятора. В случае аналоговой формы обрабатываемого сигнала переход на ре- 35 жим постоянной частоты тактовых импульсов приводит лишь к сдвигу момента взятия выборки, что при интегрировании не дает существенной погрешности в вычислении корреляционной функции и не 40 приводит к сбоям в работе коррелятора.

Целью-изобретения является повышение точности обработки.

Для достижения этой цели н коррелятор введены счетчик и делитель час- 45 тоты, вход которого соединен со вторым выходом генератора тактовых импульсов, вход счетчика соединен с первым выходом блока управления, а выходы дели.теля частоты и счетчика подключены соответственно к третьему и четвертому входам коммутатора режима работы.

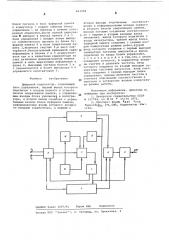

На чертеже представлена структурная схема описываемого циФрового коррелятора.

Коррелятор состоит иэ блока управ- ления 1, первый выход которого подключен к входам первого 2 и второго 3 бло ков оперативной памяти, к управляющим входам блока умножения 4 и интегратора

5, а второй выход соединен с управляю- 60 щим вхс4 ом блока буферной памяти 6, информационные входы которого являютя входами коррелятора, а первый и второй выходы подключены соответствен. но к информационным входам первого и 65 второго блоков оперативной памяти, выходы которых соединены соответственно с первым и вторым входами блока умножения, выход которого подключен к входу интегратора, и третий выход блока буферной памяти соединен с первым входом коммутатора режима работ 7, второй вход которого соединен с первым выходом генератора тактовых импульсов 8, а ныход подключен к входу блока управления, первый нход которого подключен к входу счетчика 9, выход которого соединен с третьим входом коммутатора, четвертый вход которого подключен к ныходу делителя частоты 10,вход которого соединен со вторым выходом генератора тактовых импульсов.

Коррелятор работает и ускоренном и замедленном режимах обработки цифровой информации. Определенную часть времени каждого цикла обработки между двумя соседними выборками сигналов блоки оперативной памяти 2 и 3 тактируются в ускоренном режиме. Частота тактовых импульсов задается генератором 8, сигнал с которого через коммутатор режима работы 7 и блок управления 1 подается на управляющие входы блоков оперативной памяти 2 и 3. Счетчик 9 заполняется после отсчета (N-n) импульсов, после чего коммутатор режи-ма работ 7 подключает генератор 8 к блоку управления 1 через делитель час. тоты 10. В эTQM режиме (замедленной обработки) блоки оперативной памяти тактируются низкой частотой с тем, чтобы за и оставшихся тактов (из общего числа N тактон в цикле обработки) дождаться поступления следующей выборки сигнала, задержка поступления которой определяется максимальным значением нестабильности скорости движения магнитного носителя информации.

Можно было бы вести обработку только н ускоренном режиме и после N тактов приостановить тактирование ОЗУ до прихода следующей выборки сигнала, если бы время хранения информации в динамических блоках оперативной памяти было бы достаточно большим.

Однако интервал времени между окончанием режима ускоренной обработки и приходом очередной выборки при большом диапазоне нестабильности скорости движения магнитного носителя может оказаться большим времени хранения информации в блоках оперативной памяти без разрушения. Период следования низкочастотных тактирующих импульсов выбирается меньшим или равным мак— симальному значению времени хранения информации динамическими блоками оперативной памяти, чем и обеспечивается регенерация информации в период дополнительного ожидания очередной выборки сигнала.С приходом очередной вы603998 второй выходы;подключены: соответственно к информационным входам первого и второго блоков оперативной, памяти, выходы которых соединены соответственно с первым и вторым входами блока умножения, выход которого подключен к входу интегратора, третий выход блока буферной памяти соединен с первым входом коммутатора режима работ, второй

10 вход которого соединен с первым выходом генератора тактовых импульсов,а выход подключен ко входу блока управления, отличающийся тем,что,с целью повышения точности, в коррелятор введены счетчик и делитель частоты, вход

} которого соединен со вторым выходом генератора тактовых импульсов, вход счетчика соединен с первым выходом блока управления, выходы делителя частоты и счетчика подключены соответственно к третьему и четвертому входам коммутатора режима работы. борки сигнала в блок буферной памяти

6 коммутатор 7 подает команду блоку управления 1 на переход к режиму ускоренной обработки. После полной циркуля ции г1 выборок в блоках памяти 2 и 3 блок управления 1 вводит новую выборку сейсмического сигнала из блока буферной памяти 6 в блок оперативной памяти З,включает счетчик 9,и цикл повторяется.Относительный временной сдвиг информации в блоках 2 и 3 осуществляется как и в известном корреляторе за счет включения дополнительной ячейки памяти в цепь циркуляции информации в блоке 2. Выходные сигналы блоков 2 и

3 перемножаются в блоке умножения. 4 и усредняются интегратором 5.

Формула изобретения цифровой коррелятор, содержащий блок управления, первый выход которого .подключен к входам первого и второго блоков оперативной памяти, к управляющим входам блока умножения и интегра- . тора, а второй выход соединен с управляющим входом блока буферной паМяти, информационные входы которого являютт ся входами коррелятора, а первый и

Источники информации, принятые в< внимание при экспертизе:

1. Авторское свидетельство СССР

Р 337784, кл. Cr 06 F 15/34 1972.

2. Проспект фирмы йеЫ Time

ТесЬпо (а ц, I

1102.

ЦНИИПИ Заказ 2097/41 Тираж 826

Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4