Устройство для возведения в степень

Иллюстрации

Показать всеРеферат

Союз Советскик

Соааиапистических

Республик (») so4oog

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l) Дополнительное к авт. свн)а-ву (22) Заявлено 26.0476(23) 2352726/24

РЦ М. КлР

G 06 Cr 7/20 с присоединениеаа заявки ¹ (23) Приоритет (43) Опубликоваио250478, Баоллетень № 15

1аа дщатааааыа наяатат

Сааата Мнннатраа СССР

as данаи наабратаанй а кнаытна (53) УДК

681.335(088.8) (45) Лата опублаакоааания описапаая 200478 (72) / вторьа изобретения

Т.Г. Галамай и В.Б. Дудыкевич

P3) Заявитель (54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ

Изобретение относится к области вычислительной техники и автоматики.

Известно устройство, в основе которого лежит метод, заключающийся в использовании сопряженной развертываю- 5 щей системы с параллельными so времени.развертками: линейной и степенной (11.

Подлежащее возведению в степень напряжение сравнивается с линейной разверткой, а результат возведения s степень считывается со степенной раэверт" ки в момент достижения равенства линейной разверткой напряжения, подлежащего возведению в степень, и фиксируется пиковым детектором. Однако при воз,ведении в степень с показателем и (и =,3„,) необходимо формировать степенную развертку с помощью и интеграторов, что усложняет устройство и снижает точность вычисления с увеличениЕм показателя степени иэ-за применения большого числа последовательно соединенных интеграторов.

Наиболее близким по своей техничес" кой сущности к изобретению является устройство для возведения в степень, содержащее инвертор, ключ, пиковый детектор,выход которого является выходом устройства, интеграторы, выход перво- 30 го интегратора соединен с первым входом нуль-органа, второй вход которого является входом устройства, а выход соединен с управляемым входом ключа, вход первого интегратора соединен с источником опорного сигнала, пересчетную схему (2).

В этом устройстве независимо от показателя степени используются только два интегратора, формирующие линейно подающие развертки, и пересчетная схема с коэффициентом пересчета равным показателю степени.

Однако в прототипе для возведения входного напряжения s n-юстепень затрачивается а. периодов формирования развертки на выходе интегратора, т.е. с увеличением и время преобразования тоже увеличивается, что существенно влияет на быстродействие устройства.Кроме того это устройство позволяет получать только целые степени входного напряжения У„ и непригодно для получения дробных и отрицательных степеней Ух, т.е. устройство обладает узкими, функциональными возможностями.

Цель изобретения -- повышение быстродействия и расширение функциональных воэможностей.

604009

Достигается это тем, что в устройство введены делители напряжения, блоки умножения, блок вычитания, блок сложения, переключатель, вход первого интегратора соединен с первым входом 5 первого блока умножения, выход которого через делитель напряжения соединен с первым входом блока сложения, второй вход которого соединен с выходом блока вычитания, а выход первого бло- 30 ка сложения соединен с первым входом блока вычитания и с входом ключа, выход ключа, через переключатель соединен с входом второго интегратора непосредственно и .через инвертор, а вы- 5 ход интегратора соединен с входом пикового детектора и с вторым входом первого блока умножения, выход первого интегратора соединен с первым входом второго блока умножения, второйg@ вход которого соединен с выходом ключа, а выход через второй делитель напряжения соединен с вторым входом блока вычитания.

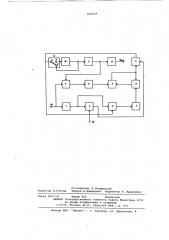

Иа чертеже представлена блок-схемае5 устройства.

Устройство состоит из интеграторов

1 и 2, нуль-органа 3, блоков умножения 4 и 5, делителей напряжения б и 7, блока 8 вычитания, блока 9 сложения, инвертора 10, ключа, 11, пиковогс детектора 12 и переключателя 13.

Опорное напряжение U подается на входы интегратора 1 и блока умножения 4. В течение одного периода выход-, у ное напряжение интегратора 1 описывается уравнением

0,(Ф) = Uot . (1)

4I)

Это напряжение подается на входы блока умножения 5 и нуль-органа 3. На второй вход нуль-органа 3 подается входное напряжение U». Нуль-орган 3 формирует сигнал длительностью

1„"- PU На это время ключ 11 отк.Рйт и на переключатель 13 подается напряжение () „ (t), Это то напряжение, которое подается через ключ 11 с выхода блока 9 на вход блока умножения 5.

В положении, когда контакты a H

Ь переключателя 13 замкнуты,.напряжение +g„(t) поступает на вход интегратора 2.

Напряжение U>(t) на выходе блока умножения 4 определяется выражением

Ug(t) кi1)о Ug (t) (2)

60 где, Ц „,„() — напряжение, подаваемое с выхода интегратора 2 на вход блока умножения 4; коэффициент пропорциональности.

Аналогично, напряжение U>(t) на выходе блока умножения 5 равно

Ug(t) K, U< (t) Ug„(t) (5)

Напряжение U (t) с выхода блока умножения 4 подается на вход делителя

6, ка выходе которого имеем напряжение ц ) 1 () где тт — коэффициент деления делителя 6.

Напряжение U (t) с выхода блока 5 подается на вход делителя 7; на выходе которого имеем напряжение

V,«) - "з" . (s) в где т — коэффициент деления дели теля 7.

Блок 9 сунв ирует напРяжение У (Ф), подаваемое на его вход с выхода блока

6, с напряжением Ug(t) подаваемым на его второй вход с выхода блока 8 вы-! читания, т.е. на выходе блока 9 .имеем

) ф» Ж ц Ж +

Напряжение 0е «) на выходе блока 8 равно разности напряжений Qdx(t) и Q,-(g) подаваемых íà его входы в() () (t)

С учетом уравнения (6) получим

U<„(t) U„(t) U<»(t) U (t) (8) т.е Ä U (t) 0 (Ь)

Из уравнений (1), (2), (3), (4), (5) и (8) следует

"1» o Ua < U«(t) (9)

Откуда (t) " " ° (i0) и U (4)

Ь» m н t

Напряжение на выходе интегратора 2 описывается уравнением с, 1

Va...b) f V,„ а),И-" f "4 ° к" at. (и)

to в

Продифференцировав последнее уравне ние и Разделив переменные, получим

d US„, к () ()Вы» (t) 604009 предложенном устройстве за один период работы интегРатора. С помощью прототипа можно получать только целые степени входного напряжения 17„, а

5 предложенное устройство позвсляет также получать дробные и отрицательные степени входного напряжения, что существенно расширило его функциональные возможности. (14) Устройство для возведения в степень, содержащее инвертор, ключ, пиковый детектор, выход которого является выходом устройства, интеграторы, выход первого интегратора соединен с первым входом нуль-органа, второй вход которого является входом устройства, выход соединен с управляемым входом ключа, вход первого интегратора соединен с источником опорного сигнала, о т л и ч а ю щ е е с я тем, что, с целью повыаения быстродействия и расьжрения функциональных воэможностей, оно содержит делители напряжения, блоки умножения, блок вычитания, блок сложения, переключатель, вход первого интегратора соединен с первым входом первого блока умножения, ВыхоД кОторого через делитель напряжения.соединен с первым входом блока сложения,второй вход которого соединен с выходом блока вычитания, а выход первого блока сложения соединен с первым входом блока вычитания и с входом ключа, выход ключа через переключатель соединен с входом второго интегратора непосредственно и через инвертор, а выход интегратора соединен с входом пикового детектора и с вторым входом

nepaoro блока умножения, выход первого интегратора соединен с первым входом второго блока умножения, второй вход которого соединен с выходом ключа, а выход через второй делнтельнапряжения соединен с вторым входом блока вычитания °

Источники информации, принятые во внимание при,экспертизе: ар к х

% где

1 рг

* =eo Lt ф„%

Следовательно, в течеииеЕ одного периоИ да работы интеграторов, напряжение на выходе интегратора 2 пропорционально входному напряжению Q» в степени где и. и п любые целые числа, задаваемые с помощьв делителей напряжения. ®

Выходное напряжение интегратора 2 фиксируется пиковым детектором 12.

В случае, когда замкнуты контакты а и 5 . переключателя 13, напряжения

Ug (В) с выхода клвча 11 поступает через инвертор, 10 на вход интегратора

2. Напряжение О,,„И) на выходе интегратора 2 описывается уравнением е

М

U „(<) Q „„-x I v,„(t dt (ge) р

>ещив это уравнение, аналогично уравнению (10), получим

Включение в состав устройства ука- 50 занных элементов изменение связей между элементамн позволили существенно повысить быстродействие устройства и расширить его функциональные возможности. В прототипе рвзультат получают М за периодов работы интегратора, в

1. 1емников Ф.Е., Славинский В.А.

Математические развертывающие системы.

И., Энергия, 1970.

2. Авторско свидетельство СССР

9 382104, М,кл, 6-06 & 7/16, 1973.

Проинтегрировав и подставив пределы измерения переменных, получим

Фнп g ape i В (Ф) = - Ы4

Решив это уравнение, получим

Формула изобретения

604009

Составитель Л. Сниищикова

Редактор E.Ãoí÷àð Техред Е.Давидович Корректор A. Кравченко

Заказ 2097/41 Тираж 826 Подписное цИИИЛИ Государственного комитета Совета Министров СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4