Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

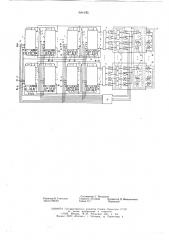

604033 шины 20

Блок 1.1

0011 шины

0001

0000

Выходы дешифратора 4

1 !

0

1

Ьлок 1.2 (после записи)

1! 00 !

1111

1111

Блок 1.2 (до записи)

1111

1111

llll

1!11 шины 20 001 опроса 4. Выходы дешифраторов 4 соединены с соответствующими шинами 2 блоков 1. Входы указанных дешифраторов 4 соединены с выходами элементов ИЛИ 5, одни входы которых подключены к прямым или обратным выходам соответствующих триггеров 6 регистра 7 опроса, а другие — к прямым выходам триггеров 8 регистра 9 маски. Устройство содержит также элементы И 10, выходы которых присоединены к соответствующим входам триггеров 6 регистра 7. Одни входь1 элементов И 10

10 соединены с соответствующими выходами триггеров 11 регистра !2 операнда, а другие —— с управляющими выходами дешифратора операций 13. Регистр 12 выполнен в виде нескольких независимых регистров 14 сдвига, а регистр 9 — в виде нескольких кольцевых ре15 гистров 15 сдвига по числу строк матрицы из блоков 1. Устройство содержит также сумматоры 16 по модулю два. Каждый блок 1 имеет вход 17 управления записью, вход 18 управления выборкой, информационный вход

19 и разрядные шины 20 записи по числу шин 3. Блоки 1 каждой строки объединены в группы по два, шины 3 каждого блока в группе соединены с информационными входами сумматоров 16, выходы которых подключены к соответствующим шинам 20 другого 2 блока 1 данной группы. Управляющие входы сумматоров 16 данной строки, а также вхоВыходы Блок 1.1 дешифратора 4 0101 шины 3

1 0001

0 0010

l 0100

0 1000

1 0000

0 0000

1 0000

0 0000

На вход 17 блока 1.1 подается сигнал разрешения считывания (например логический «О»), на вход 17 блока 1.2 — сигнал разрешения записи (например логическая «1»), на входы 18 обоих блоков — сигнал разрешения выборки и на вход 19 блока 1.2 сигнал «О». В результате на шинах 3 блока 1.1 появляются считанные сигналы 0101. На общий вход сумматоров !6 блока 1.2 подается сигнал «О», что приводит к появлению на ши-нах записи этого блока сигналов 0101 и записи кода «О» на пересечении 2-й и 4-й разды 17, 18, 19 блоков 1 каждого столбца матрицы подключены к соответству1о1цич выходам дешифрцтора 13. Входы дешифратора 13 подсоединены к выходам соответствующих триггеров 11 регистра 12.

Работу устройства проиллюстрирусм на примере выполнения логических операций в группе, составленной из двух запоминающих блоков 1.1 и 1.2 с восемью адресными шинами 2 и четырьмя выходными разрядными шинами 3 (на чертеже этот вариант не показан).

Рассмотрим, например, последовательность действий при выполнении операции инвертирования массива чисел, хранящихся в блоке 1.1.

Все запоминающие элементы блока 1.2 предварительно устанавливаются в состояние «1».

B блоке 1.1 хранятся четыре числа 011, 010, 001, 000, записанные на четырех его разрядных линиях в коде «1» на фоне «О». На регистр 15, являющийся регистром маски этих блоков, заносится код 110, на регистр 14 заносится код первого операнда 000. Код «О» с выхода триггера 11 младшего разряда регистра 14, поступающий на входы элементов

И 10, используется для установки в «О» триггеров 6 регистра 7. Код опроса 000 и код маски 110, поступая на входы элементов ИЛИ 5, обеспечивают возбуждение четных выходов—

000, 010, 100, 110 дешифратора 4 и соответствующих шин 2 обоих блоков.

Ьлок 1.2 Блок 1.2 (до записи ) (после записи) ! 1!1 1010

llll 1111

) 1 1 1010 !!! llll

11! 1010

111! 11! 1

llll 1010

1111 lll!

О!О!

f рядных линий и четных адресных шин блока 1.2 (33llHcb производится по коду «1» па шине 20).

В следующем такте обращения код на регистре 14 сдвигается на один шаг — 000, код на регистре 15 циклически сдвигается ——

101, что приводит к возбуждению 000, 001, 100, 101 — выходов дешифратора 4. Запись «О» в блок 1.2 производится также как в первом такте — в запоминающие элементы на пересечении возбужденных шин 2 и 20.