Реверсивный дешифратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (® 604151

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свих-ву— (22) Заявлено 030$7б(2Ц 2355008/18-21 с присое)аинениеае ааявки №вЂ” (23) Йриоритет (43) Опублнковано 25,04.78,Бюллетаать ¹ 15 (51) М. Кл.

Н 03 К 13/247

Гаатдаратаеаанй аеватет

Веаета Маааатрее COOP аа,дааев ааееретеааа а етарытаа (68) УДЫ 681.325.63 (088.8) (4$) дата опублтековаций ойисаний 07,04.78

В.Г.Колосов А С.Лопатин В.Ф Мелехин И Л.Туккель и Ю.В.Шелонин (72) Двторм аеаобретенив

Pa) Заявитель (54) РЕВЕРСИВНЫИ ДЕШИФРАТОР

Изобретение относится к области втз" числительной техники и может быть ис4 польэоваио при построении запоминаю- щих устройств.

Известны дешифраторы для запомина ющих устройств, содержащие. первую ступень дешифрации на потенциальных эле- ментах (например, на интегральных микросхемах), а вторую. ступень - на транзисторных ключах с трансформаторным : ао входом и диодной иатрицей, подключен- ной к шинам накопителя (lj

Недостатками таким дешнфраторов являются сравнительно низкая помехозащищенность потенциальмых элементов и " 1я сложность первой ступени дешифрации. известны также дешифраторы для эа; поминающих. устройств, содержащих матрицы магнитных:сердечников имеющих две ступени дешифрации, причем одна в0 ступень дешифрации выполнена на диодах, подключенных к адресным шинам матрицы, а другая - на ключах, выпол ненных в виде магнитных переключателей тока .(ИПТ) (2 ). 25

ЦеЛь изобретения - повьааенне быстродействия и упрощение дешифратора., Это достигается тем, что реверсивный дешифратор для запоминающих устройств на матрицах магнитных сердеч- 30

3 ников, шины которых соединены с диодами, образующими оконечную ступень де4 шиФрации, содержащий источник питаниф, транзисторные ключи, формирователи импульсов:тока:и ограйичители тока, со- держит три ступени дешифрации с каскаднюе включением матричных дешифрат9Ров, :при -этом вторая ступень выполне . на:на,траизисторах. Выводы конечного диодкого матричного дешифратора, связанные .с анддайае -дйодов, подключены к:коллектораш:,транзисторов таапа р-н-)р первого, траазиаторного матричного де шифратора второй.ступени. Выводы диодного матричного дешифратора, связанwe.c катодами диодов, подключены к коллекторам траеазисторов типа и-р-и второго транзисторного матричного де шифратора второй ступени. Объединенные аноды и:катоды диодов конечного матричного дешифратора соединены с шинами матриц магнитных сердечников, а другие концы шин подключены к кол лекторам транзисторов типа р-и-р н п-р-и состветственно третьего и четвертого транзисторных матричных дешифраторов второй ступени. Объединенные группы эмиттеров транзисторов каждого транзисторного матричного дешифратора второй ступени через транзисторные

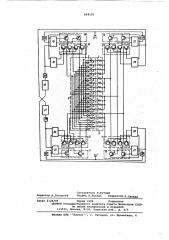

604151 ключи соединены с выходами одного дешифратора первой ступени, а объединенные группы базовых выводов транзисторов каждого транзисторного матричного дешифратора второй ступени — с выходами другого дешифратора первой ступениНа чертеже изображена схема описываемого устройства.

Реверсивный дешифратор содержит матрицу 1 магнитного оперативного запоминающего устройства (МОЗУ), на шинах 2

10 которой находятся сердечники, диоды

3,4 конечной (третьей) ступени 5 дешифратора, транзисторы 6,7 типа р-и-р и транзисторы 8,9 типа п-р-п первого 10, второго 11 и 12 третьего четвертого 13

l5 транзисторных матричных дешифраторов второй ступени дешифратора транзисторные ключи 14-17, дешифраторы 18-25 первой ступени дешифратора, формирователи 26,27 импульсов тока, ограничители тока 28-30.

На чертеже изображена схема реверсивного дешифратора íà n = 16 выходов.

Для коммутации импульсов тока считы-25 вания съема содержит первую ступень дешифратора считывания, в которой используется четыре дешифратора 18-21, выполненные, например, на МПТ, транзисторные ключи 14, 15 для выбора эмит-30 теров транзисторов 6,9 транзисторных матричных дешифраторов 10, 11 второй ступени, диоды 3 третьей ступени 5 дешифратора.

Четыре дешифратора 22-25 íà NIIT 35 ступени, транзисторные ключи 16, 17, транзисторные матричные дешифраторы

12,13 второй ступени, диоды 4 третьей ступени 5 дешифратора обеспечивают коммутацию импульсов тока записи (с таким же числом элементов в каждой ступени, что и для дешифратора считывания). Выходы дешифратора 18 на МПТ соединены с базовыми цепями транзисторов транзисторных ключей 14, а выходы дешифратора 19 на МПТ вЂ” с базовыми це45 пями транзисторов 6 транзисторного матричного дешифратора 10, .эмиттеры транзисторов объединенных групп которого соединены с коллекторами соответствующих транзисторов транзисторных клю-50 чей 14.

Выходы транзисторного матричного дешифратора 10 подключены к анодам диодов 3, а к катодам диодов 3 подключены шины 2 матрицы 1 МОЗУ, к этим же >5 точкам подключены аноды диодов 4. Катоды диодов 4 соединены с выходами транзисторного матри:ного дешифратора

13, входы которого подключены к выходам дешифратора 24 на МПТ и через тран- 60 зисторные ключи 17 — к выходам дешифратора 25 на МПТ.

Вторые .концы шин 2 матрицы 1 МОЗУ объединены в группы и подсоединены к выходам транзисторных матричных дешифраторов 11, 12, входы которых подсоеди- иены к выходам дешифраторов 20, 21 и

22, 23 соответственно (выходы дешифраторов 22 и 21 подключены к матричным дешифраторам на транзисторах через транзисторные ключи 16 и 15 соответст венно) .

Для ввода информации в описываемый реверсивный дешифратор используются обмотки записи сердечников дешифраторов 18-25 на МПТ, обмотки считывания которых одним концом через резистор (на чертеже не показан) и ограничители тока 29 соединены с формирователями 26 и 27 импульсов тока, а другим концом через диоды и резисторы (на чертеже не показаны) и ограничители тока 28,30 — с источником питания.

Работа устройства происходит следующим образом. При обращении к запоминающему устройству (Зу) вначале поступает код выбираемой шины матрицы на обмотки записи сердечников дешифраторов

18-25 на МПТ, причем одинаково готовят ся сердечники дешифраторов 18 и 22, 23, 20 и 24, 21 и 25 на МПТ.

После записи кода в каждом из них будет только одна проводящая ветвь с малым импедансом для распределяемого импульса формирователей 26, 27.

В режиме считывания запускается формирователь 26, в выходную цепь которого включены обмотки считывания сердечников дешифраторов 18-21 на МПТ.

Импульс тока формирователя 26,пройдя по проводящим ветвям дешифраторов

18-21 (в каждом дешифраторе только одна проводящая ветвь), создает напря жения, полярности и величины необходимой для открывания соответствующего транзистора. При этом, благодаря описанной последовательности связей, срабатывают по одному транзистору в транзисторных ключах 14, 15 и матричных дешифраторах 10, 11, что обеспечит выбор только одной шины 2 матрицы 1 МОЗУ

Импульс тока считывания идет от полюса источника питания последовательно через ограничитель 28, выбранные транзисторы транзисторных ключей 14 и транзисторного матричного дешифратора 10. диод 3, выбранную шину 2, выбранные транзисторы транзисторного матричного дешифратора 11 и транзисторных ключей 15, ограничитель 30 на минус источника питания.

Амплитуда импульса тока считывания и ее независимость от импеданса шины матрицы 1 определяются ограничителями

28, 30, которые целесообразно выполнять в виде нелинейного элемента, например, на магнитных сердечниках с °

ППГ. В виде таких же нелинейных элементов целесообразно выполнять и ограничители 29. Кроме того, использование для ограничения амплитуды импулье сов тока одинаковых ограничителей 28 и

30 уменьшает перепад потенциала на шиá04151 нах 2 матрицы 1, делает его примерно равным потенциалу общей точки, что уменьшает помехи, возникающие в разрядных шинах матрицы из-эа паразитных связей.

В режиме записи запускается формирователь 27 и дальнейшая работа дешифрирующих ступеней выбора шины 2 при записи происходит аналогично описанной для режима считывания.

Таким образом, предлагаемый реверсивный дешифратор обеспечивает прохожжение импульсов тока считывания и тока записи по выбранной шине матрицы сердечников.

Формула изобретения

Реверсивный дешифратор для запоминающих устройств на матрицах магнитных 20 сердечников, шины которых соединены с диодами, образующими конечную ступень дешифрации, содержащий источник питания, транзисторные ключи, формирователи импульсов тока и ограничители 2я тока, отличающийся тем,что, с целью повышения быстродействия и упрощения, он содержит три ступени дешифрации с каскадным включением матричных дешифраторов, при этом вторая ступень выполнена на транзисторах, выводы конечного диодного матричного дешифратора, связанные с анодами диодов,подключены к коллекторам транзисторов типа р-п-р первого транзисторного матричного дешифратора второй ступени, выводы диодного матричного дешифратора, связанные с катодами диодов, подключены к коллекторам транзисторов типа п-р-п второго транзисторного матричного дешифратора второй ступени, объединенные аноды и катоды диодов ко. ечного матричного дешифратора соединены с шинами матриц магнитных сердечников, а другие концы указанных шин подключены к коллекторам транзисторов типа р-и-р и п-р-и соответственно третьего и четвертого транзисторных матричных дешифраторов второй ступени, объединенные группы эмиттеров транзисторов каждого транзисторного матричного дешифратора второй ступени через транзисторные ключи соединены с выходами одного дешифратора первой ступени, а объединенные группы базовых выводов транзисторов каждого транзисторного матричного дешифратора второй ступенис выходами другого дешифратора первой ступени.

Источники информации, принятые во внимание при экспертизе:

1. Патент Англии Р 9б4487,кл. G 4 С, 1971.

2. Авторское свидетельство СССР

9 247351,кл. fi 03 К 13/247, 1972.

604151

Составитель Г.Кутний

Техред A.Áîãäàí Корректор д.лакида

Редактор В. Гончуков

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Заказ 2124/49 Тираж 1086 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5