Устройство автоматического выравнивания времени распространения при передаче дискретных сообщений по параллельным каналам

Иллюстрации

Показать всеРеферат

<

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (в1) Î41áÎ (6li) дополнительное к авт. свид-ву (22) Заявлено 02.10.75 (2в) 2177521/18-09 (53) М. Кл.

Н 04 В 3/04 с присоединением заявки ло

Гоотдоротввииый иояитот оовоти 1йинивтров ШР ио иоиоя ивойротоиий и открытий (23) Приоритет (53) УДК 621. 394.

662.2(088.8) (43) Опубликовано250478, Бтоллетень % 15 (45) Дата опубликования описания 060478 (72) %втор изобре1ения

В.П.Савин (71) Заявитель (54) УСТРОЙСТВО АВТОМАТИЧЕСКОГО ВЫРАВНИВАНИЯ ВРЕМЕНИ

РАСПРОСТРАНЕНИЯ ПРИ ПЕРЕДАЧЕ ДИСКРЕТНЫХ СООБЩЕНИЯ

ПО IIAPAJIJIEJIbHblM КАНАЛАМ

Изобретение относится к электричес кой связи и может использоваться в системах передачи дискретных сообще-. ний по параллельным каналам.

Известно устройство автоматического выравнивания времени распростране-. ния при передаче дискретных сообщений по параллельным каналам, содержащее элементы задержки, выходы которых подключены соответственно к первым и втс- Ip рым входам выходного коммутатора и блока контроля, выход последнего подключен к третьему входу выходного коммутатора, а через ключи к первому входу элементов задержки (1). 15

Однако известиое устройство обладает недостаточной точностью выравниват ния.

Для этого в устройство автоматического выравнивания времени распрсстра- 2О нения при передаче-дискретных сообщений по параллельным каналам, содержащее элементы задержки, выходы которых подключены соответственно к первым и вторым входам выходного коммутатора 25 и блока контроля, выход последнего подключен к третьему входу выходнога коммутатора, а через ключи к первому входу элементов задержки, введены входной коммутатор, рнрвый и .второй регистры сдвига, коммутатор, элемент

НЕТ-ЭКВИВАЛЕНТНОСТЬ, задающий генератор, элемент запрета, триггер управления, элемент И и счетчик цикла вырав нивания, при этом к вторым входам элфментсв задержки подключены входы входного коммутатора, выход которого под- ключен к третьим входам элементов за " держки через псследовательно соединея вЂ, ные коммутатор, первый регистр сдвигу, выход которого соединен с вторым входом коммутатора, элемент НЕТ-ЭКВИВАЛЕНТНОСТЬ, элемент запрета, второй регистр сдвига, выход которого подключен к второму входу элемента НЕТ-3КВИВАЛЕНТНОСТЪ, к третьему входу которого подключен выход выходного коммутатора, при этом задающий генератор подключен к входу управления элементов задержки, к второму входу второго регистра сдвига и третьему входу коммутатора — непосредственно, и к вторыь„ входам ключей через последовательно соединенные счетчик цикла выравни"вания, второй выход которого соединен соответственно с вторым и первым вхс " дами элемента запрета, .емента И, триг гер управления, к второму входу которого подключен выход элемента запрета, а к третьему входу — третий выход счет604160

f = ХЗ(х хг+ Х1 хг) чика цикла выравнивания, и элемент И, выход блока контроля подключен к входу управления входного коммутатора.

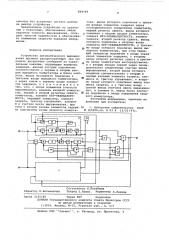

На чертеже изображена структурная электрическая схема предложенного уст- 5 ройства.

Устройство содержит элементы 1 и 2 задержки, выходы которых подключены соответственно к первым входам выходного коммутатора 3 и блока 4 контрол, 10 выход которого подключен к третьему входу выходного коммутатора 3, а через ключи 5 и б, к первому входу элементов 1 и 2 задержки, к вторым входам о которых подключены входы входного коммутатора 7, выход которого подключен к третьим входам элементов 1 и 2 задержки через последовательно соединенные коммутатор 8; первый регистр 9 сдвига, выход которого соединен с вто-. рым входом коммутатора 8; элемент НЕТ- 20

ЭКВИВАЛЕНТНОСТЬ 10; элемент 11 запрета и второй регистр 12 сдвига, выход которого подключен к второму входу элемента HET-ЭКВИВАЛЕНТНОСТЬ 10, к третье. му входу которого подключен выход вы- 25 ходного коммутатора 3, при этом задающий генератор 13 подключен к входу управления элементов 1 и 2 задержки, к второму входу второго регистра 12 сдвига и третьему входу коммутатора 8 30 непосредственно, и к вторым входам ключей 5 и б через последовательно соединенные счетчик 14 цикла выравнивания, второй выход которого соединен соответственно с вторым и первым вхо- 35 дами элемента 11 запрета и элемента И

15; триггер 16 управления, к второму входу которого подключен выход элемента 11 запрета, а к третьему входу— третий выход счетчика 14, и элемент 40

И 15, выход блока контроля 4 подключен к входу управления входного коммутатора .7.

Каждый элемент 1 и 2 задержки содержит коммутатор 17,регистр 18 сдвига, элемент И 19, коммутатор 20, регистр 21 сдвига, триггер 22 с раздельными входами, управляемый Д-триггер

23 и триггер 24 с раздельными входами.

Устройство работает следующим образом.

В начальный момент работы элементы

1 и 2 задержки устанавливают в положение, соответствующее значению задержки, равному >

Допустим, единичный потенциал на выходе блока 4 соответствует выбору сигнала данных, поступающих с второго входа устройства на элемент 1 задержки. Тогда входной коммутатор 7 пропускает на первый вход коммутатора 8 сигнал данных с первого входа устройства, а выходной коммутатор 3 пропускает .на 65 выход устройства сигнал данных второго входа устройства, прошедший через элЕмент 1. Сигнал данных первого входа устройства стробируется импульсами час-: тоты f1 длительностью С (где C / ),.

Логическое значение сигнала данных в момент стробирования проходит через коммутаторы 7,8 и 17 и записывается в регистры 9 и 18 сдвига.

Триггер 24 с раздельными входами устанавливается в единичное (исходно состояние от импульса частоты g>, п4ступающего на единичный вход.

B управляемый Д-триггер 23 производится перепись с триггера 22 предварйтельно записанного в него предыдущего единичного элемента, и одновременно установка триггера 22 в нулевое (исходное) состояние. Регистры 12 и 21 в это время находятся в режиме хране+. ния. Регистр 12 сдвига в исходном состоянии выравнивания заполнен нулями.

После окончания режима записи регист; ров 9 и 18 сдвигов наступает режим рвциркуляции регистров 12„ 9, 18 и 21.

В начальный момент времени в регистрах 21 хранится 2 @ -разрядное двоичное слово с единицей в пК -ом разряде.

На выходах элементов 1 и 2 с часто-. той j, появляется логическое значениб

mK -ro разряда, а на втором входе элемента НЕТ-ЭКВИВАЛЕНТНОСТЬ 10 логическое значение мК-го разряда элемен . та 1 на все время режима рециркуляциф.

Элемент НЕТ-ЭКВИВАЛЕНТНОСТЬ 10 реализует переключательную функцию где х -логическое значение первого

1 входа, х - логическое значение второго г входа, х — логическое значение входа

Ъ управления.

Таким образом, элемент НЕТ-ЭКВИВАJIEHTHOCTb 10 производит операцию поразрядного сравнения двоичного слова регистра 9 с логическим значением выхода устройства и, одновременно, операцию поразрядного логического умножения результата сравнения с содержи мым регистра 12.

На вход элемента 11 подается инверсное значение сигнала с выхода элемента НЕТ-ЭКВИВАЛЕНТНОСТЬ 10.Счетчик 14 задает количество последовательных операций вравнения и логического умножения, по результатам которых выносится решение о временном рассогласовании сигнала данных первого и второго входов устройства.

Допустим цикл выбран равным Ы периодам частоты,, тогда на (К-2)-ом пе риоде частоты (1, на втором выходе декодера счетчика 14 появится импульс с длительностью, равной периоду часто 604160 ты j<, который поступает на нулевой вход триггера 16 управления с раздельными входами и устанавливает его в исходное (нулевое) состояние.

На (N -1)-ом периоде частоты на третьем выходе декодера счетчика 14 появится импульс, который поступает на вход управления триггера 16 и разрешает на все время (N -1)-й рециркуляции установку триггера 16 сигналом инверс- 10 ного значения с выхода элемента 11 ïîñтупающего на единичный вход триггера 16V .После окончания (М -1)-го периода, рециркуляции в регистре 12 будет нахоО диться двоичное 2 К разрядное слово,. заполненное единицами, за исключением

К соседних разрядов, заполненных нулями. Эти К соседних разрядов однозначно определяют место в элементах 1 и 2 задержки, в котором находится единичный элемент сигнала данных первого и 20 второго входов, совпадающий с единичным элементом, считываемым с выходов элементов 1 и 2 и поступающим на вы- ход устройства. На N -ом периоде час-тоты f на первом выходе декодера счет- 25 чика 14 появится импульс с длительностью, равной периоду частоты 1, который поступает на вход управления элемента 14 и на axîä элемента И 15.

В результате на все время g --го пе- 30 риода рециркуляции на выходе элемента

11 устанавливается нулевое значение, регистр 12 заполняется нулями и одновременно двоичное слово, хранившееся в регистре 12 и характеризующее величину задержки, поступает на вход ввода величины элемента 2 задержки. Одновременно логическое значение выхода триггера 16 через элемент И 15 и ключи 4 (5) поступает на вход управления 4 ввода величины задержки в элементах

1 и 2.

В случае единичного потенциала на выходе триггера 16 коммутатор 20 элементов 1 и 2 пропускает на вход регистра 21 в режиме рециркуляции двоичное 45 слово величины задержки сигнала данных первого и второго входов устройства.

В случае нулевого потенциала на выходе триггера .16 управления комму- 50 татор 20 пропускает на вход регистра

21 в режиме рециркуляции сигнал с выхода регистра 21 и, таким образом,сохраняется прежнее значение величины задержки элементов 1 и 2. 55

Ра (0,5) -(O,S) 6 (О т.е. по существу равна нулю.

Тогда возможная погрешность выравнивания при переключении из-за возможного отставания определения величины задержки вследствие суммарной нестабильности и возможности ошибок н сигнале данных параллельных каналов не будет превышать величины Т /К, При

К З, это эквивалентно ЗЗЪ от То.

На третий вход элементов 1 и 2 по-р дается с выхода регистра 12 инверсный сигнал, таким образом, регистр 21 хранит двоичное 2пК -разрядное слово,за- > полненное нулями за исключением К со, седних разрядов, заполненных единица-ми .

С помощью триггера 24 а раздельными входами производится считывание в режиме рециркуляции единичного элемен-" та в регистре 18 с номером разряда, совпадающим с номером первой правой единицы (из К единиц) н регистре 21, Логическое значение единичного элемента, считанного с регистра 18 сдвига, через элемент И 19 записывается в трнггер 22 с раздельными входами, выполня-: ющего функции промежуточной памяти.

Очередным импульсом частоты 1 дли тельностьв Т; производится запись сигнала на выходе триггера 22 н Д-триггер 23, установка триггеров 22 и 24 исходное состояние, перевод регистров

21 и 12 н режим хранения, перевод коммутатора 17 с регистром 18 и коммутатора 8 с регистром 19 в,режим записи очередного единичного элемента сигнала данных первого и второго входов устройства.

Допустим где ЬЖ- суммарная нестабильность частоты задающего генератора и генератора на передающей стороне;

— скорость передачи информации.

Тогда емкость регистров 12, 9, 18, и 21 равна 2 к = 2 ° 7 3 = 42 (разряда), где Р = В = 1200 Гц.

f1= FK= )200 Ъ =эь00 гц, -» Р (2 g a 1) = 3200 5 (4Ь «.1 = (51 800 ги, Вследствие нестабильности ьФ с учетом днух параллельных каналов, через М единичных элементов, где

M = 2 а, = . =- 2. 10 (элементов) будет происходить флюктуация значащих моментов сигнала данных первого входа и второго входа устрой::тна на © величину.

< учетом этого выбирается у «14 например г1 = 15.

Вероятность ложного выравнивания при этом будет ранна учитывая наличие системы синхронизации дискретной информации в приемнике информации с исправляющей способностью, равной 48Ъ, можно утверждать,. что уже при K=3, возможно переключенне

604160

Формула изобретения

Составитель Е.Погиблов

Редактор Н.Большакова Техред 3.×óæèê - Корректор А.Лакида

Заказ 2125/49 Тираж 805 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Ра.ушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 каналов без искажения сигнала данных на выходе устройства.

Предложенное устройство по сравнению с известным, обеспечивает любую заданную точность выравнивания, обладает высокой надежностью и обеспечивает повышение скорости передачи информации. устройство автоматического выравнивания времени распространения при передаче дискретных сообщений по параллельным каналам, содержащее элементы задержки, выходы которых подключены соответственно к первым и вторым входам выходного коммутатора и блока контроля, выход последнего подключен к третьему входу выходного коммутатора, а через ключи к первому входу элементов задержки, о т л и ч а ю щ е е с я тем, что,. с целью повышения точности выравнивания, введены входной коммутатор, первый и второй регистры сдвига, коммутатор, элемент НЕТ-ЭКВИВАЛЕНТ.—

НОСТЬ, задающий генератор, элемент запрета, триггер управления, элемент

И и счетчик цикла выравнивания, при этом к вторым входам элементов задерж- 30 ки подключены входы входного коммутатора, выход которого подключен к третьим входам элементов задержки через последовательно соединенные коммутатор, первый регистр сдвига, выход которого соединен с вторым входом коммутатора, элемент НЕТ-ЭКВИВАЛЕНТНОСТЬ, элемент запрета, второй регистр сдвига, выход которого подключен к второму входу элемента НЕТ-ЭКВИВАЛЕНТНОСТЬ, к третьему входу которого подключен выход выходного коммутатора, при этом задающий генератор подключен к входу управления элементов задержки, к второму входу второго регистра сдвига и третьему входу коммутатора непосредственно, и к вторым входам ключей через последовательно соединенные счетчик цикла выравнивания, второй выход которого соединен соответственно с вторым и первым входами элемента запрета, элемента И, триггер управления, к второму входу которого подключен выход элемента запрета, а к третьему входу третий выход счетчика цикла выравнивания, и элемент И, выход блока контроля подключен к входу управления входного коммутатора.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

9 365099,кл. Н 03 К 13/32 1971.