Устройство для разделения асинхронных каналов

Иллюстрации

Показать всеРеферат

Все, „, /.Нф- 1., ° с ..

"е В,а

ОП "" . Е

ИЗОБРЕТЕН ИЯ (И) 604167

C:oKI3 Советских

Социалистических

Ресяублин

К АВТОРСКОМУ СВИДЮТИЛЬСТВУ (6l) Дополнительное к авт. свид-ву (22) Заявлено 25.05.7 6 (21)2366358/09 с присоединением заявки Ж (53) М. Ка.Я

Н 04 Ю 3/08 (23) Приоритет е (43) Опубликовано 25.04.78. Бюллетень М4

Гюсуднрстннннмй кфинтет

Сеавта Мнннстрна СССР не данаи нзейретвнкй н нткритпй (53) УДК 623..394.662 (088,8) (45) Дата опубликования описаиия13.0 .7ф (УЯ) АВТ9р изобретения

И. Т, Картюшов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ АСИНХРОННЫХ

КАНАЛОВ

Изобретение относится к передаче данных.

Известно устройство для разделения асинхронных каналов, содержащее последовательно соединенные первый триггер, первый элемент

И и первый делитель частоты, выход которого подключен к первым входам фазового компара-. 5 тора .и буферного накопителя, второй вход которого соединен с вторым входом фазового комнаратора,.а к управляющему входу первого делителя частоты подключен выход генератора импульсов ()!.

Однако в известном, устройстве небольшой диапазон допустимых расстроек тактовых частот каналов.

Цель изобретения — расширение диапазона допустимых расстроек тактовых частот кана лов. !5

Для этого в устройство для разделения асинхронных каналов, содержащее последовательно соединенные первый триггер, первый эле.мент И и первый делитель частоты, выход которого подключен к первым входам фазового компаратора н буферного накопителя, второй вход которого соединен с вторым входом фазового компаратора, а к управляющему входу первого делителя частоты подключен выход генератора импульсов, введены второй и третий делители частоты, второй н третий трнг2 геры и второй, третий и четвертый элементы

И. Прн этом первый выход второго триггера подключен к первому входу второго элемента

И, второй вход которого соединен с вторым входом первого элемента И и выходом второго делителя частоты, к входу которого подключен выход первого .делителя частоты, второй и третий входы которого соединены соответственно с выходамн второго и третьего элементов И, а второй выход первого триггера подключен к первому входу третьего элемента И, второй вход которого соединен с вторым выходом второго триггера, первый вход которорого соединен с первым входом первого триггера и выходом четвертого элемента. И, к первому входу которого подключен выход третьего триггера, первый и второй входы которого соединены соответственно с выходами третьего элемента И и фазового компаратора, второй выход которого подключен к второму входу четвертого элемента И, причем третий вход третьего элемента И соединен с первым выходом третьего делителя частоты, второй выход которого подключен к второму входу буферного накопителя, третий вход которого сое-, динен с входом третьего делителя частоты, к управляющему входу которого подключен выход генератора импульсов, а на вторые вхо57

4 тий триггер 10 в нулевом состоянии. Импульс записи с выхода третьего делителя 8 поступает на вход записи накопителя 5 и продвигает информацию, поступающую на информационный вход накопителя 5. Импульс считывания с выхода первого делителя 3 частоты поступает на вход считывания буферного накопителя 5 и считывает информацию с него абонентский выход 15.

Импульсы записи и считывания поступают, кроме того, на вход компаратора 4, который измеряет фазовый сдвиг между этими импульсами, Когда фазовый сдвиг между импульсами записи и считывания равен нулю, формируется импульс на выходе компаратора 4, подключенном к входу установки третьего триггера 10.

Г!ри фазовом сдвиге, равном Л; фазовый компаратор формирует импульс на своем выходе, соединенном с одним иэ входов закрытого четвертого элемента И 13. В исходном состоянии компаратор 4 постоянно формирует импульс, соответствующий фазовому сдвигу Л.

На выходе второго делителя 7 частоты формируются импульсы с частотой, в m раз меньшей частоты импульсов считывания, поступающих на его вход, С приходом команды запуска, поступившей на вход !б или !7, взводится первый триггер или второй триггер 9, и соответственно открываются первый или второй элементы И 2, !1 закрывается третий элемент И 12. Импульсы с выхода второго делителя 7 начинают поступать соответственно на вход сложения или вычитания первого делителя 3 через первый или второй элемент

И 2, 11. Каждый импульс, поступивший на вход сложения илн вычитания соответственно добавляет или исключает импульс на счетном входе первого делителя 3. В результате фаза импульса считывания относительно фазы импульса записи начинает изменяться в ту или иьую сторону. Когда эта фаза достигнет нулеsoro значения компаратор 4 выдает импульс иа соответствующем выходе и устанавливает триггер 10 в единичное состояние; тем самым четвертый элемент И 13 откроется.

Дальнейшее смещение фазы продолжается до тех пор, пока она не достигнет значения Х.

Г, этот момент на соответствующем выходе фазового компаратора 4 формируется импульс, который через четвертый элемент И 13 сбрасывает в ноль первый нли второй триггеры 1, 9, после чего подстройка фазы прекращается, и импульс с вновь открытого третьего элемента

И 12 сбрасывает в ноль третий триггер 10, Так корректируется временной сдвиг информа-, ционной последовательности на один бит в ту или иную сторону. С приходом следующей команды запуска процесс повторяется. °

Таким образом, предложенное устройство позволяет расширить диапазон допустимых расстроек тактовой частоты канала относительно номинальной. ды первого и второго триггеров поданы импульсы синхронизации.

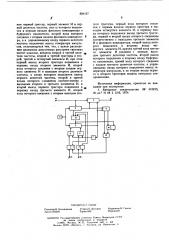

На чертеже дана структурная электрическая схема предлагаемого устройства.

Оно содержит последовательно Соединенные первый триггер 1," первый элемент И 2 и первый делитель 3 частоты, выход которого подключен к первым входам фазового компаратора 4 и буферного накопителя 5, второй вход которого соединен с вторым входом фазового компаратора 4, а к управляющему входу пер-,р вого делителя 3 частоты подключен выход геиератора 6 импульсов, второй и третий дели .ели 7, 8 частоты, второй и третий триггеры

9, 10 и второй, третий и четвертый элементы

И 11, 12, !3..При.этом первый выход второго триггера 9 подключен к первому входу второго элемента И l l, второй. вход которого соединен с вторым входом первого элемента И 2 и выходом второго делителя ? частоты, к входу ко- торого подключен выход первого делителя частоты 3, второй и третий входы которого соединены соответственно с выходами второго и третьего элементов И 11, 12, а второй выход первого триггера 1 подключен к первому входу третье о элемента И 12 — второй вход которого соединен с вторым выходом второго триггера

9, первый вход которого соединен с первым 2s входом первого триггера 1 и выходом четвертого элемента И 13, к первому входу которого подключен выход третьего триггера 10, первый и второй входы которого соединены соответственно с выходами третьего элемента

И 12 и фазового компаратора 4, второй выход которого подключен к второму входу четвертого элемента 13, причем третий вход треть-, его элемента И 12 соединен с первым выходом третьего делителя 8 частоты, второй выход

Формула изобретения которого подключен к второму входу буферного накопителя 5, третий вход которого соединен с входом третьего делителя 8 частоты, к управляющему входу которого подключен выход генератора импульсов 6, а на вторые входы первого и второго триггеров l, 9 поданы импульсы синхронизации.

Устройство работает следующим образом.

В исходном положении первый и второй триггеры l и 9 находятся в нулевом состоянии. Первый Ивторой элементы И 2 и 1 закрыты, а третий элемент И 12 открыт. Разуплотненный сигнал. поступает с информационного входа 14 на информационный вход буферного накопителя 5 и на управляющий вход третьего делителя 8, где происходит подстройка выходной частоты генератора 6 от сигнала„

Выходная частота третьего делителя 8 точно равна nf, где f — скорость информации на информационном входе 14, à n — коэффициент деления третьего 8 н .первого 3 делителей.

Таким образом, выходные частоты делителей ,3, Sравны,,но сдвинуты по фазе одна относительно другой íà 3. Это достигается тем, - что импульс, формирующийся на выходе среднего состояиия третьего делителя 8, когда он находится в среднем состоянии; через третий элемент И 12 сбрасывает в ноль первый делитель 3..Этот же импульс подр.ржнвает треУстройство для разделения асинхронных как,алов, содержащее последовательно соедннен604167

Составитель Г. Серова

Корректор И. Гокснч

Подписное

Техред О: Луговая

Тираж 805

Редактор Н. Большакова

Заказ 2I39/50

0НИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

l I 3035, Москва, Ж.35, Раушская наб. д. 4/5

Филиал ППП «Патент», г. Ужгород,. ул. Проектная. 4 ные первый триггер, первый элемент И и первый делитель частоты, выход которого подключен к первым входам фазового компаратора н буферного накопителя, второй вход которого соединен с вторым входом фазового компаратора, а к управляющему входу первого делителя частоты подключен выход генератора импульсов, отличающееся тем, что, с целью расширения диапазона допустимых расстроек тактовых частот каналов, введены второй и третий дели- тели частоты, второй и третий триггеры и второй, третий и четвертый элементы И, при этом первый выход второго триггера подключен к первому входу второго элемента И, второй вход которого соединен с вторым входом первого элемента И н выходом второго делителя 1э частоты, к входу которого подключен выход первого делителя .частоты, второй и третий входы которого соединены соответственно с выходами второго и третьего элементов И, а второй выход первого триггера подключен к первому входу третьего элемента И, второй вход которого соединен с вторым выходом второго триггера, первый вход которого соединен с первым входом первого .триггера н выходом четвертого элемента И, к первому входу которого подключен выход третьего триггера, первый и второй входы которого соединены соответственно с выходамн третьего элемента

И н фазового компаратора, второй выход которого подключен к второму входу четвертого элемента И, причем третий вход третьего элемента И соединен с первым выходом третьего делителя частоты, второй выход которого подключен к второму входу буферного накопителя, третий вход которого соединен с входом третьего делителя- частоты, к управляющему входу которого подключен выход генератора импульсов, а на вторые входы первого н второго триггеров поданы импульсы синхронизации, Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство Ж 415815, М, кл Н 04 J 1/ 16; 1974.