Устройство для обнаружения сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАЙ ИЕ<о6044Б

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Ссцнапистнческих

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 01.09.76 (21) 2402728!18-09 (51) M.Kë.3 6 01 S,7/30 уЯ М Яиь с присоединением заявки— (23) Приоритет—

Государственный комитет

СССР

А0 донам изобретений и открытий (43) Опубликовано 07.01.82. Бюллетень № 1 (53) УДК 621.396.96 (088.8) (45) Дата опубликования описания 07.01.82 (72) Авторы изобретения

К. К. Васильев и Г. Ф. Комиссаров (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ СИГНАЛОВ

Изобретение относится к,радиотехнике, в частности к техн яке выделения некогерентных сигналов .на фоне нестационарных

:по.мех.

Известно устройство для обнаружения сигналов, содержащее аналого-цифровой преобразователь, выход которого соединен с входом N последовательно включенных многоразрядных, регистров сдвига,;каждый из которых содержит К отводов, синхронизатор, первый и второй выходы которого соединены соответственно с входами управленияя аналого-цифрового преобразователя и каждого из N многоразрядных .регистров сдвига, и блок принятия решения (Ц.

Однако это устройство обладает нестабильностью уровня ложных тревог.

Целью изобретения является увеличение стабильности уровня ложных тревог.

Для этого в устройство для обнаружения сивналов, .содержащее аналого;цифровой преобразователь, выход которого соединен с,входом N иоследователыно включенных многоразрядных .регистров сдвига, каждый из,которых содержит К отводов, синхронизатор, аервый и втооой выходы которого соединены соответственно с входами управления аналого-цифрового преобразователя IH каждого из N многоразрядных

Регистров сдвига, л блок (принятия реше.ния, введены М логических блоков и два сумматора, при этом одноименные отводы и выходы каждого из N многоразрядных регистров сдвига соединены с соответствующими,входами каждого из М логических блоков, выходы одного из,которых соединены с входами первого сумматора, а выходы всех остальных логических блоков, а также отводы первого многоразрядного региспра сдвига соединены с соответствующими вхсдами второго сумматора, а выходы сумматоров соединены с входами блока принятия:решения,,причем,каждый из логических блоков содержит N — 1 логических

15 элементов, при этом иервые .входы каждого из N — 1 логических элементов и второй вход N — 1 логическото элемента являются соответствующими входами логического блока, выход каждого из N — 1 логических

20 элементов является соответствующим выходом логического блока, а вторые и первые входы каждого из N — 1 логических элементов, кроме иервого, соединены между собой.

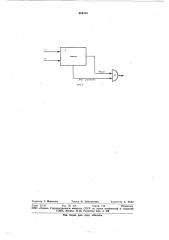

К роме того, каждый из логических элементов логического блока выполнен в в иде последовательно соединенных блока .вычитан ия .и ключа, второй вход которого соедииен с вторым .выходом блока вычитания, лервый и ВТо.ðîé входы которо,го являются

ЗО соответственно первым и вторым входом

604415

65 лагичесюго .элемента, а выход ключа является, выходом логического элемента.

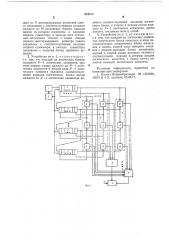

На фиг. 1 приведена структурная схема предложенного устройства; на фиг. 2— функциональная электрическая схема логического элемента.

Устройство для обнаружения сигнала содержит аналого-цифровой,преобразователь 1, выход которого соединен с входом

N последовательно включенных многоразрядных регистров 2 сдвига, каждый из котарых содержит К отводав, синхронизатор

3, первый и втарой выходы котораго соединены соответственно c входами управления аналого-,цифрового преобразователя 1 и каждого из N многоразрядных регистров

2 сдвига, и блок 4 принятия решения, М логических блоков 5 и два сумматора 6 и 7, при этом одноименные отводы и выходы каждаго из N мно гораз рядных регистров 2 сдвига соединены с соответствующими входам и .каждого из М логических б.л.оков 5, выходы одного,из которых соединены с входами первого .сумматора 6, а выходы всех остальных логических блоков 5, а также отводы первого многоразрядного регистра 2 сдвига соединены с соответствующими,входами, второго сумматора 7. Выходы сумматоров,6 и 7 соединены с входами блока 4 принятия:решения. Каждый из логических блоков 5 содержит N — 1 логических элементов 8, при этом,первые входы каждого из N — 1 логических элементов 8 и второй вход N — 1 логического элемента 8 являются соответствующими входами логического блока 5. Выход, каждого .из N — 1 логических элементов 8 является соответствующим выходом логического блока 5, а вторые .и .первые входы каждого из N — 1 логических элементов 8, кроме первого, соединены .между собой. Каждый из логических элементов 8 логического блока 5 выполнен в виде последовательно соединенных блока 9 вычитания .и ключа 10, второй вход которого соединен с вторым .выходом блока 9 вычитания. Первый .и втарой входы блока 9 являются соответственно перзым,и вторым входом логического элемента 8, а выход ключа 10 является, выходом логическаго элемента 8.

Устройство, работает следующим образом.

Видеосигналы с выхода приемника радиолокационной станциями (РЛС),поступают ,на аналого-ци фрозой преобразователь 1, где,осуществляется временная дискретизация.,и квантование сигналов на и уровней.

Квантованные сигналы поступают íà MHQгоразрядные:регистры 2 сдвига. Синхронизатор 3, запускаемый синхроимпульсами

РЛС, обес|печивает синхронную, работу aIHaлого-цефрового 1преобразователя 1, управляет движением сигналов,,в многоразрядных,регистрах 2 сдвига. Скорость движения сигналов определаетея часжтой квантов

З0

45 дальности, а от одного мнагоразрядното,регистра 2 сдвига,к другому — частотой повторения импульсов РЛС. Число, разрядов .каждого канала многоразрядного регистра

2 сдвига ра вно mlczy квантов дальности, а число каналов равно числу уровней квантования многоразрядного регистра 2 сдвига.

Анализ поступающих на .многоразрядные ,регистры 2 сдвига сипналов осуществляется с помощью логичвсиих элементов 8. При этом,квантованные сигналы анализируются адноаременно в диск ретах по дальности для двух соседних периодов повторения пакета и мпульсов длиною N. Число анализируемых дискретов по дальности п определяется пер иодом,нестащионарности помехи и зависит от параметров РЛС (в данном случае

n=3; N=4).

Логический элемент работает следующим образом.

Если на вход лагическо го элемента 8 поступают сигналы Х1 и Х> из двух соседних периодов повторения, то на .выходе, будет ,разность XI — X> при XI)X> и,нуль при

XI(Xq. Далее сигнал с лопическаго элемента 8 поступает в сумматоры 6 или 7, таким образом в сумматорах 6,и 7 c)MMHpóþòñÿ только, положительные приращения, процесса в области,предполагаемого сигнала (сумматор 6) и в области помехи (сумматор 7). Для пplиняTия решения о,наличии цели используется сумма положительных приращений в области cHII íaëà, .нор|мированная к сумме положительных приращений B области помехи. Использование дополн ительной информащи и, содержа щейся в положительных приращениях отсчетов в области помехи, позволяет обеспечить хорошую устойчивость ложной тревоги ipaccматриваемопо обнаружителя лри изменении корреляции помех от моря.

Предложенное устройство для о бнаружения сигнала обладает хорошей устойчи.востью ложной тревоги при изменении кор реляционных свойств поыехи. При изменении в пределах 0 — 09 величина ложной тревоги изменяется всего ea,порядок.

Формула изобретения

1. Устройство для обнаружения clHTналов, содержащее аналого-цифровой преобразователь, выход которого соединен с,входом последовательно, включенных .многоразрядных регистров сдвига, каждый из коToipbIx содержит .К отводов, синхронизатор, первый и второй выходы которого соединены соответственно с входами управления аналого-ци фроваго преобразователя .и каждого из N ìíoãolðàçðÿäHûõ регистров сдвига, и блок (IIpHHятия,решения, о тл и ч а ющ е е с я тем, что, с щелью увеличения стабильности уровня ложных тревог, введены

М логических блоков и два сумматора, при этом одноименные отводы и выходы кахк604415 дого из N,ìíîãîðàçðÿäíûõ регистров сдви. га соединены с соответствующими,входами .каждого из M логических блоков, выходы

:одного из которых соединены с входами пер ного сумматора, а выходы всех остальных логических блоков, а также отводы первого многораз ряднаго репистра сдвига соединены с соответствующими входами второго сумматора, а выходы сумматора соединены с входами блока принятия реыения.

2. Устройство по п. 1, отл ич а ю щ е ес я тем, что каждый .из логических блоков содержит N — 1 логических элементов, при этом первые,входы, каждого из N — 1 логичесиих элементов и второй, вход N I логического элемента являются соответствую.щими входами логического блока, выход каждого из N — 1 логических элементов является соответствующим, выходом логического блока, а вторые и первые входы каждого из Л вЂ” 1 логических элементов, кроме первого, соединены между собой.

3. Устройство по,п. 1, отл.ич а ю ще ес я тем, что каждый из логических элементов логическото .блока вьиполнен в виде IIоследовательно соединенных блока,вычитания и ключа, второй .вход которого соеди,нен с вторым выходом блока вычитания, первый и второй входы которого являются соответственно первым и вторым входом логического элемента, а выход ключа является выходом логического элемента.

Источник ни формации, принятый во внимание прои экапертизе:

1. Патент Великобритании № 1216406„

НКИ Н 4 D, опублик. 02.02.71.

604415

Риг. г

Редактор Т. Морозова

Техред И. Заболотиова Корректор С. Файн:"

Тня. Харис. фил. пред. «Натек»

Заказ 27/32 Изд. М 106 Тираж 718 П одни сное

ННО «Поиск» Государственноге кемитета СССР по делам изобретений и открытий

113%5, Москва, 7К-35, Раушская наб„д. 4/5"