Активное вероятростное реле

Иллюстрации

Показать всеРеферат

1I I) 6053I7

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

СОЮЗ СОВЕтокик

Социалистических

Республик ф"" - Ф Ъ@

1@ф . с Яй1 ф

Ф

Л .1,». сД<"т ф1,1, %» т,,л „ . д- 6

Н ОЗК 17/60 (61) Дополнительное к авт. свпд-ву (22) Заявлено 09.03.76 (21) 2331103/18-21 (51) М. Кл.- с присоединением заявки №

Совета Министров СССР по делам изобретений и открытий (43) Опубликовано 30.04.78, Бюллетень ¹ 16 (45) Дата опубликования описания 17.04.78 (53) УДК 621.382.63 (088.8) (72) Авторы изобретения

Ю. М. Корпууно, А. В. Симкин и Ю. А. филатов

Рязанский радиотехнический институт (71) Заявитель (54) АКТИВНОЕ ВЕРОЯТНОСТНОЕ РЕЛЕ

ГосУдарственный комитет (23) априори

Изобретение относится к устройствам для фильтрации нспрерывных сигналов и может быть использовано для определения положения искаженного помехой двухполярного полезного сигнала, меняющегося от — 1 до 1 относительно заданного нулевого порога.

Известны устройства для обраоотки сигналов с помощью двухпозициопных бесконтактных реле, содержащие нелинейный интегратор с элементами положительной и отрицательной обратных связей, которые решают задачу в случаях, когда помеха отсутствует.

Реле выдает сигнал — 1 или 1 в зависимости от того, превышает или не превышает двухполярный полезный сигнал на его входе значение нулевого порога (11. Недостатком рслейных устройств обработки сигналов является то, что при поступлении на вход реле сигнала, искаженного помехой, выходной сигнал не дает возможности достоверно судить об истинном положении по7сзного сигнала ilо отношению к порогу.

Целью изобретения является определение диапазона нахождения непрерывного двухполярного сигнала по отношению к фиксированному .нулевому порогу. Эта цель достигается тем, что в активном вероятностном реле, содержащем нелинейный интегратор с элементами положительной и отрицательной обратных связей, логи1сское устройство и четырс цепи перезаряда выходной емкости нелинейного интегратора, согласно изобретсишо каждая из четырех цепей псрсзаряда выходной емкости нелинейного интегратора содержит последовательно соединеьп1ы" ключевой управляемый полевые транзисторы с каналами одинакового типа проводимости, причем в двух цепях транзисторы имеют канаl одного типа проводимости, а в двух других— канал противоположного типа проводимости; затворы ключсвыx транзисторов соединcны с выходами логического устройства, а затворы управляющих тр нзистороз — с выходами четырех дополнительных элементов нелинейных обратных связей, входы которых соединены с выходом нелинейного интегратора;

11p II этом элементы двух 11оложптс 7hlll>1х и двух отрицательны; обратных связей нелинейного 11нтсгратора содержат по одному по20 левому транзистору, затворы которы.; подключены к выходу логического устройства, причем элементы первой отрицательной и второй положительной обратных связей содсржат полевые транзисторы с каналами од25 ного типа проводимости, а элементы первой положитсльной и второй отрицательной обратных связей — полевые транзисторы с каналом противоположного типа проводимости.

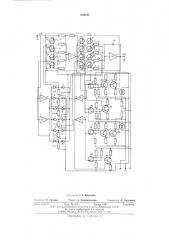

На чертеже приведен а схсх1 а предл агасмо30 го вероятностного рслс.

605317

Устройство содержит лоп!чс кос устро?(«7во, образова?(иос шсстью лоп)ческими э„((ментами И на диодах 1 — 12, управл.- :,;ых

ВХОДНЫМ Z (i) if ВЫХЛ ?((ЬIМ V (t) Ciii ii а:(2М i через иеипвсрп<рующие cif

1 7 Входил!.О и B»f <0,7 II 0, 0 C ill и;)лов, If «.) Ji! I«?)ный интегратор, собра;шый B.i усилителе поо

СТОЯННОI О TÎI(2 1 <)> J>:;(<0 i??d!>1 с 1(л:i Бь((. ра li»11сторы 19 — 22, управля«мы«по. «»i>i«тра).3:гсторы 23 — 2б, ключ«зы«!(ол« i(»c тра;(зис;лры

27 — 30, транзисторы 31 — 40 ii коilд«исатср 21.

Работа устройства осноьапа::(2 опр.дслспии логическими элементами иа диодах 1 — -1? зоны пребывания входного z(t) и выходного о(t) сигналов по отношению к нул«вому 110POi У И ПОДКЛЮЧ«НИИ С .IOXIOllli>10 К. ПО -I(. ВЫХ транзисторов 19 — -22 и 27 — 30 к ш(гратор. цспи OTP(1UBTc. Ibíné или 110. Io)I>fiT«,(ь fell 00ратных св?!3«?! и соотВстств) 10(цс>( (z(t) )О) и ниже (z(t) (0) I ó (c»0»0 поро, а, а через оь, о — — пребыва !с Бblx07110(0 cããнала v(t) выше (о(1) )0) п ниже (u(i) О }! нулевого порога. При этом образую!ся «л«дующие четыре области совместного пребывания входного z(t) и выходного v(<) < ип!аЛОВ IIO ОТНОШС?!ИIО К ИХЛ:)Л)1 У ИОРЛГЛЬ>л:<(Г

ЗН2ЧЕНИIО; Z, О; Z О,; Z ., V(, 2, V

i) ИСХОДНОМ СОСТОЯНИИ i!P1; Иа,!1(i(f11 Иа»ХОде сигнала лтриц21 сл1>НОЙ пл 7?lp)10«7 и

z(t) =z конденсатор 41 заряжен до L . Lll:0го отрпцатсльпог0 напряжения. Кчю-iсвыс пÎлcDые тра)içèñi 0ðû 22 . 30 От!;ppытLI и, лсв!».,I потенц iaлом с выхода шсс-<о:о и пятого чоГil ICCI

11, 12 и 9, 10, а другие ксночезые пол«Вы« транзисторы 19 — 21 Il 27 -29 закрыты

OThpbITblX,7,i!0 >OB 1, 3, 5,, -., б ll 8 )е ?ь<р(>Х

!еских 37«XICFITOB . I. ПОЗTО <1 < lln входу интегратора через усилитель 17 подключены только вторая IJ0,70æJ»òcëülfая 00 ратная связь ?i упр2»7ÿ«ìûé полевой:рапзистор 2б. Зтот транзистор 32êðü(ò ы хо;)п!»м напряжением интегратора через lp2113(гсторы

39 и 40 четвертой пслин«йиой обратной с»язи, ьследствис чего значение парам«

При поступлении па вход всрояп(о "i) о:: реле положительного сигнала, прсвыш(пощгo нулевой порог, выполняется первое услоь

1,)

25 30

<О .<

<) ) ) ()() ()5 вие =- ., V совместно!о пребывания входно:о и выходного сигналов. Пр:i этом только перВый элемент И логи fccKQIO устройства, обра3OBciiiilbIII iiO jd)J i 1 il 2, 0«12«TC?1 32I(pbITJ». (, а остальные диодпые элементы И открыты.

Поэтому к интегратору оказываются подклюC l(O

v(t) иа выход« интегратора приоткрываются транзисторы 31, 32 и 33 первой нелинейной обратной связи и умспьша=тся запирающий положитслы(ый потенциал на Çà) âîðc трапзистор2 23. Прн э> х(слпрл 1 1(зле)iи сго и(pсхода исток — сток, а слс;оватслы:о. и значение параметра т(о } всрлятиостпогn рсл« уменьшается по нелинейному закону с кni(«Bного значения до минимального.

В момент превышения выходным напряжением о(/) интегратора нулевого порога выИОЛИЯСТСЯ 13TOPOC ) C,710»!IC С-, О COB:;!ÑСТНОГО пребываш:я сигналов. Э О приьодит к открытию дш)до» 2, 10 и 12 первого, пято(о и шее(ого ллгич«ских э fc»«)!To», И и к закрыi fifo диодов >1 и б второго и третьего эл«мспТ0В И. В p«3< льтате это: 0 32крыь210тся Tp2ilзисторы 19 и 27 и открываются транзисторы

20 и 28, которые пс).!кл!0>)а!От ко входу и тсгратора нерву о пс,ложитсльпую обратную

СВЯЗЬ ЧСРСЗ 1!ПВЕРТИР, lощнй ВХОД СУ)(:, 10щего усилIITеля 17 и Второе нелинcéíîc СОпротивлснпс, образованное переходом исток — сток полевого транзис)ора 24 и соотзстстг>ующсй обрат юи связью на транзистора.

34 и 35. 11 f,; 02! 0}) исpcx03?IT в актиВны .i рс)к)<м рабл-.ы. Быстро растущее с!0 положительное ьыходиос папряжсниp открывает

f10.7«1 0?i Tp21l3liCT0p )>-1 и )(p«)fii . < ВЫЙ Тр21131!стор 35. Псложительиf>il потенциал, снимас)»ый с коллектора (р"-„ifçистлра 35. Закрыва«т

1 p2!1»licTop 2 ). Е(л < ÎJI J)07 иl.лсlillc псрс.":0,72 ис(Ок- — c > Ок 3«лli (;l»i . (";.л леско):«÷ínc(и, что приводит к < Bp;ill

:< стра т(v} 1:):i«;ратлра и ()J кci>ii:.".(Быхлдно1 О папряж,!(iiя v (т) 112 лп)1(д«,lсп;!л\(< рОВ((( прин((\I ас (О. 2 (},5 L, (2 (Одс) р?1 p«3 сл

ci 0 Вы.содплм напр?!жеiililf, Oлизко)! к О, ), схема с>-апозптся псчув т» ггсльпой к ко7«02! f J! Jf)i »ХО,.!1101 n ilci lip >7)(сс)1 ПЯ, ВЫЗВ2 "fl(bfh! Д«йcTBIIp)I помех, и с1 а билbli(7 поддсряси»2с l Вы.п.,110« папряжспис 1 2 этл)I «po!31!c. При э l Ом значении в<.: (o;li>n;o с)ь нa»I2 иитс(.ратора полевой транзистор Зб третьей нел?(нейной обP2TI:0É «ВЯЗИ и! И32КРЬ)т за СЧЕТ С >(ЕЩЕИИЯ С делит»я:!2 резисторах, следовательно, призакрыты li «ремни«вые тг)анзисторы 37 и 38.

Отрицательно".. Напряжение, снимаемое с с0l1р071I!3лси ия пагрмзк и тpс) iIÇисTОр 2 33, призакрываст полевой транзистор 25 трет(,сй цепи

605317 перезаряда конденсатора 41, задавая тем самым начальное значение сопротивления перехода исток †ст этого транзистора равным сопротивлению перехода исток — сток транзистора 23 при исходном отрицательном сигнале на входе вероятностного реле.

Если выходной сигнал меньше нулевого порога z(t) (0, выполняется третье условие

= îâìåñòíîãî пребывания входного и выходного сигналов z, v+. В этом случае открываются диоды 3 и 5 второго и третьего логических элементов И и закрываются диоды 7и 8 четвертого логического элемента И. Это приводит к закрытию транзисторов 20 и 28, отключающих от интегратора первую положительную обратную связь и второе нелинейное управляемое сопротивление транзистора 24 соответственно, и к одновременному открытию транзисторов 21 и 29, подключающих ко входу интегратора через неинверсный вход усили"сля 17 вторую отрицательную обратную связь и третье нелинейное сопротивление, образованное управляемым полевым транзистором 25 и третьей нелинейной обратной связью на транзисторах 36 — 38. При этом интегратор переходит из активного:режима рабогы,в пассивный, сопровождающийся переключением его параметра т(о) с бесконечно большого значения за счет закрытого управляемого транзистора 24 на заданное меньшее значение за счет приоткрытого управляемого транзистора 25, чем и обеспечивается стабилизация длительности спада вершины заднеI0 фронта импульса с отстройкой от ложных дроблений полезного сигнала помехой. С уменьшением напряжения на выходе интегратора третья нелинейная обратная связь, действующая аналогично рассмотренной выше первой нелинейной обратной связи, обеспечивает изменение сопротивления перехода исток — сток транзистора 25 по нелинейному закону с конечного значения до минимального значения. При переходе выходного сигнала

v (t) в область отрицательных значений (о (t) (О) выполняется четвертое условие совместного пребывания сигналов z v . При этом открывается диод 8 четвертого логического элемента И и одновременно закрываются диоды 10 п 12 пятого и шсстопо логических элементов И, что приводит к закрытию транзисторов 21 и 29 и к открытию транзисторов 22 и 30. В результате происходит подключение к ипвертирующему входу усилителя 17 второй положительной обратной связи и четвертой нелинейной цепи перезаряда сглаживающего конденсатора 41 и перевод нелинейного интегратора в активный режим

5 раооты. В этом режиме происходит закрытие управляемого транзистора 26 по нелинейному закону, сопровождающееся увеличением параметра т(о) вероятностного реле до бесконсчно большего значения под действием

10 возрастающего отрицательного выходного напряжения v (t) через четвертую нелинейную обратную связь на транзисторах 39 и 40.

Формула изобретения

Активное вероятностное реле, содержащее нелинейный интегратор с элементами положительной и отрицательной обратных связей, логическое устройство и четыре цепи перезаряда выходной емкости нелинейного ннтегра2О тора, отличающееся тем, что, с целью определения диапазона нахождения непрерывного двухполярного сигнала по отношению к фик ированному нулевому порогу, каждая из четырех цепей перезаряда выход ой емкости нелинейного интегратора содержит последовательно соединенные ключевой и управляемый полевыс транзисторы с каналами одинакового типа проводимости, причем в двух цепях транзисторы имеют канал

ЗО одного типа проводимости, а в двух других— канал противоположного типа проводимости, затворы ключевых транзисторов соединены с выходами логического устройства, а затворы управляемых транзисторов соединены с вы35 ходами четырех дополнительных элементов нелинейных обратных связей, входы которых соединены с выходом нелинейного интегратора, при этом элементы двух положительных и двух отрицательных обратных связей

4О нелинейного интегратора содержат по одному полевому транзистору, затворы которых подключены к выходу логического устройства, причем элементы первой отрицательной и второй положптсльной обратных связей со45 держат полевые транзисторы с каналами одного типа проводимости, а первой положительной и второй отрицательной обратных связей содержат полевые транзисторы с каналом противоположного типа проводимости.

50 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Ne 448598, кл. H ОЗК 17/60, 1972.

Составитель Т. Морозова

Техред A. Камышннкова

Рслактор Н. Громов

Корректор Л. Брахннна

Заказ 600/17 Изд. 5е 420 Тираж 1087

I II1O Государственного комитета Совета Министров СССР по делам изобретений и открытий

1!3035, Москва, К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Подписное