Устройство для компенсации межсимвольных искажений дискретного сигнала

Иллюстрации

Показать всеРеферат

И 4

1 т

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пц 605329

ВаВ Саюатваа

60@E33NCYN%CNIK

Рвоиублня (61) Дополнительное к авт. саид-иу (22) Заявлено 19.07.?6 {21) 2392948(18-09 (5l) М. Кл.а Н 04L 7/08

Н 04В 1(12 с присоединением заявки № (23) Приоритет

ЙеуАарстаялны» камвтат

Сарета Инниртраа gggp

64 делам иаабратеинф к еткрытнй (43) Опубликовано 30.04.78. Бюллетень № 16 (45) Дата опубликования описания 26.04.78 (53) УДК 621.394.6 (088.8) (72) Авторы изобретения

В. А. Егоров, В. Ф. Кабанов, В. П. Покровский, И. М. Провоторский, Н. П, Хворостенко и А. И. Цимблер (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОМПЕНСАЦИИ МЕЖСИМВОЛЬНЫХ

ИСКАЖЕНИЙ ДИСКРЕТНОГО СИГНАЛА

Изобретение относи ся к технике передачи дискретной информации и предназначено для использования в каналах коротковолновой радиосвязи, а также проводной связи.

Известно устройство для комленсации меж- 5 символьных искажений дискретного сигнала, содержащее входной блок вычитания, выход которого подключен к входу демодулятора и к первому входу блока выделения интерференционной составляющей, выход которого со- 10 единен с другим входом входного блока вычитания, а второй вход соединен с основным выходом демодулятора (1).

Однако точность компенсации межсимвольных искажений дискретного сигнала недоста- 15 точна.

Цель изобретения — повышение точности компенсации.

Для этого в устройство для компенсации межсимвольных искажений дискретного сиг- 20 нала, содержащее входной блок вычитания, выход .которого подключен к входу демодулятора и к первому входу блока выделения интерференционной составляющей, выход которого соединен с другим входом входного блока 25 вычитания, а второй вход соединен с основным выходом демодулятора, введены блок выделения сннхросигнала, распределитель, блок памяти, блок считывания и блок инерционной фазовой автоподстройки, при этом дополни- з0 тельный выход демодулятора подключен через блок выделения синхросигнала к тактовому входу распределителя и к входу блока и нерционной фазовой автоподстройки, выход которого соединен с тактовым входом блока считывания, к информационному входу .которого через блок памяти подключены выходы распределителя, к информационному входу которого подключен основной выход демодулятора.

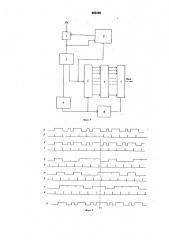

На фиг. 1 представлена структурная электрическая схема устройства; на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство для компенсации межсимвольных искажений дискретного сигнала содержит входной блок 1 вычитания, выход которого подключен к входу демодулятора 2 и к первому входу блока 3 выделения интерференционной i ставляющей, выход которого соединен с другим входом входного блока 1 вычитания, а второй вход соединен с основным выходом демодулятора 2, блок 4 выделения синхросигнала, распределитель 5, блок 6 памяти, блок 7 считывания и блок 8 инерционной фазовой автоподстройки, прн этом дополнительный выход демодулятора 2 подключен через блок 4 выделения синхросигнала к тактовому входу распределителя 5 и к входу блока 8 инерционной фазовой автоподстройки, 605328

5 (О

25 до

4()

Выход KoTopot 0 сОединен с га ктовым Входом блока 7 считывания, к информационному входу которого через блок 6 памяти подключены выходы распределителя 5, к информационному входу которого подключен основной выход демодулятора.

Устройство для компенсации межсимвольных искажений дискрет)(ого сигнала работает следующим образом.

С помощь(о входного блока 1 (ВыkH(d)II!» в постуна!Ощем на вход устройства сигнале компенсируется интерфоренционная составляюи(а51, коГОрая ф01)ми()устся Олоком 3 ее Выделения. Результиру)о!цее напр)(ж IIHB детектируется демодулятором 2, а с помощью блока 4 выделения сннхросигнала из него извлекастс» синхросшнал, Инфо!)М((ц(!Ониа)! последовательность с основного выхода демодулятора 2 поступает в распределитель 5, который ц?!к)!?(Ческ?! записывает ее ноэлем(.нтно в ячейки блока о памяти. Со сдвигом иа нолпсриода цикла происходит c÷èòûâàHHå записанной HHф 0 ) Ы а ц И И C 11 O M Î I U b i O O JI O K B 7 C H H T I v J 11 B H», ! Олупериодный сдвиг обеспе)икается блоком 8 инерционной фазовой автоподстройки, Распределитель 5 преобразует посл.довательный сигнал в N (!араллеJkh(IJ,(x сигналов, увеличивая нри этом J(J(J(reJIbtk0(. Гь 1)осылок и Л" раз, где N — -период цикла, выра)кенный в числе тактовых интервалов. Фаза распределителя 5 устанавливается в соогвегстви?! с фазой выделенного в блоке 4 ьыдсления с?п(хросигнала и тем самым обеспечивается сохранение исходного закона распределен?(я иифорMBl(JI0I»Ibl)(посылок 1(0 подканалам прп сме()((снии входного сигнала, Период цикла îïðåделястся удвоенной максимально возможной

Величиной смещения основного (рабочего) отcue((i импульсной реакции канала. При ка>кдом смещении Во времени ннформациснной !

IocJi(довательпости на входе распределителя

5 С%Си(я(отея одновременно и синхроимпульсы, т. с. фаза распре,челнтсля. )ТО приводит к сдвигу передних фронтов посылок в подканалах. Однако поскольку Область стробироВанпя, используемая при считывании, располагается в середине этих посылок, нарушения (пнхронизма не происходиf.

Па фиг. 2 приведены временные дпаграм;,;ы, 1(0»cH5rio)JIHe работу устройства, когда по каналу передается пери()днческ»ÿ комбинапи» (фиг. 2а) н цикловые импульсы (ф(г. 2б) с Ii(риодом повторения в три тактовых интервала. IIB фиг. 2в, г, при!!сдены СОГлветствены информационная и ц((кловая последовательности на Выходе де Олулятора 2, при (ем в момент времени tk 5!)!ест место смещение фазы на один тактовый и(!терв((л («вы(!здание» одного импульса). На фиг. 2д, ж, н изображены информационные последовательности в каждом из трех ()одканалов, а на (риг. 2е, з, к — соответг гну(ошне последова cJlbIiÎcTl! счи1 ыв(!)Он(их импульсов. ВыхОднОЙ с?(ГН(ц! приведен )(а (1)нг, 2л. Сме(цение информа и ионной (и Оследо!)ательности и а выходе д(.модулятора 2 привело к смешении моменТОВ ЗаПИСИ НОСЫЛОК В И!)(КЯНЯЛ!1 ОтпоентЕЛЬН() Jv(UМ IITO СЧИ (1)(ВЯНИ>!. 0)1НЯКО фаэа ВЫХС Дной последовательности Jl(изменилась. При этом Jiместо «выпавшего» их(1(ульса зафиксир()ва!! Один и 3 !) анси Jl!)И1!51 111х и. i(Г!у JlbcOB.

ЕлОк 8 и и () ц и о ! (О ?1 ф (1 J () H (J J ! ВГ 0 н О, (cT p o ?I J(H

0()CСн(. (Нна(Т ВО«(Г)(но(:JJCJJJJJ! ((c ()В()JJ(! (ЯЛЬНОГО сдвига фаз IM(!жду записью и с и!тыванисм послс ка;кд()ГО смснгсния входногÎ сигнала, ПоСКОЛ),КУ BOCC ГЯНОВЛ.:Н ИЕ фа ЗЫ Cviki J b(BBHII» ПРОИСХОД(!T МЕДЛ(11110, О!JО MО f((:Т 0(!1 Ь 01СЛ(Ж(-НО обычной схемой актовой сш хронизации ?но 1 р(;0)ГГBJ»I J(JIC)cf) с !!0é )!В(()uрмации.

VLTPBII(vJlHC СМ(:111C klliii ?JI((f!Of)MQ((? .0(II!Ok! НОс)!с,(о(за Гельнос Г! J на выходе комненсатсра !

vJ(!rJ(CИМВ0ЛЬНЫХ ИСКаске((И(! 1(ОЗ()О)!»С! уС 1ра нить срывы синхронизма,нри синх!)Онных мето;(ах не()с)(а (н ДнсlсйстнОй JJJJ()0f)M(k(1?kk(, (СM самым исключается нсобход JMOc)b дополни(сльных вхо>кдсннй в инхронизм li повторной

1Icрсдачи неправильно принятых у-(астков информационной последонательносзн, что позJ)c)л»ег повысить пропускную способность канаJld СВ5!3H.

Фоомула !(зобретения

YCT j) J)ACTBu ДЛ» КО vill(liC(11(l! i! МЕЖ JJ Jv?BO)ibных искажен! й;(нскретног0 сигнала,. содержащее ikходной бл()к сыч?1!анин, Выход которого по..(к)!ючсн к вхо.(у д(модулятора и к первому входу блока выделения интерференционной сос(ааля к)щей, выход которого соединеH с д )уГ."(м ВхОдОм входнОГО блока вычитЯния, Я

НТО(>ОЙ ВХОД С()ЕДИНСН. С ОСНОВНЫМ ВЫХОДОМ демодулятора, о т л и ч а к: щ е е с я тем, что, с ц(ль!О .Новы)пения точности комг)енсации, в него введены блок выделения синхросигнала, распределитель, блок памяти, блок считывания и блок инерционной фазовой автоподстройки, при этом дополнительный выход демодул5Г(опа нодключсн через блок выделения

CIIJI (POC?I Jl3Л I(TBH C)BOMY ВХОДУ РЯСПРЕДЕЛИтел» и к входу блока инерционной фазовой явтоп()дстро?!к)(, выход которого соединен с тактовым в)з)дом блока считывания, к информанионному B>;0,(ó которого через блок памяти подкл(очсны выходы распределителя, к информационному входу которого подключен основной выход,пех(одулятора.

Источники информации, прин»тые во внимание при экспертизе

l. Лвторское сь?)детельство СССР М 517168, к.(. Il 0!8 ljl2, 1!. 75.