Синхронизатор несущей частоты

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОВРЕТЕН ИЯ

И АВТОРСКОМУ СВИДВТЙЛЬСТВУ (t>) 606221

Союз Советских

Социалистических

Республик (6l) Дополнительное к авт. свиа-ву(22) Заявлено 29.11.76 (2т}2425733/18-0 (53} М. Кл.

Н 04 L 7/04 с присоединением заявки №вЂ”

Государственный ком«тет

Совета теин«строе СССР оо делам «зобретений

« открытий (23) Приоритет (43) От1убликовано 05.05.78. Бюллетень №1 (53) УДК

62 1.394.662 (088.8 } (45) Дата опубликования описания 19.04.78

Нго Вьет Нья (СРВ), Е. А. Волков и Л. Г. Жук (CCCP} (72} Авторы изобретения (7 т } За я витель (54) СИНХРОНИЗАТОР НЕСУЩЕЙ ЧАСТОТЫ

Изобретение относится к радиотехнике и может испопьзоваться в устройствах когерентного приема фазоманипупированных сигнапов.

Известен синхронизатор несущей частоты, содержащий поспедоватепьно соединенные перемножитепь, приемник символов и управпяемый генератор, объединенный по входу с перемножитепем (1).

Однако это устройство характеризуется тем, что при случайном перескоке фазы ге- 1О нератора управляемого напряжением с íà р» будет осуществпяться "обратная" работа, что приводит к ухудшению достоверности приема сигналов.

Целью изобретения явпяется повышение д5 точности синхронизации сигнапов несущей частоты, Дпя этого в синхронизатор несущей чаототы, содержащий поспедоватепвно соединенные перемножитепь, приемник симвопов и 20 управляемый генератор, объединенный по входу с перемножитепем, между выходом управпяемого генератора и другим входом перемножителя включен бпок контроля и установления синхронизма фазы, другие входы которо- 25

ro соединены с выходом приемника симвопов и входом перемножитепя, кроме того блок контропя и установпения синхронизма фазы состоит из последовательно соединенных первого блока совпадения, фазового детектора, первого бпока задержки, триггера и фазовращатепя, другой вход которого соединен с другим входом фазового детектора, причем выход решающего блока через поспедоватеп но соединенные второй бпок задержки и фор мирователь строб-импульсов подключен к входу первого бпока совпадения, а через второй бпок совпадения — к другому входу . триггера, при этом другой выход второго блока задержки подключен к другому входу второго блоке совпадения, причем другие входы фазоврашатепя, фазового детектора, блока совпадения .и вход решающего блока, а также выходы фазовращатепя и решающего бпока являются соответствующими входами и выходами блока контропя и установления синхронизма фазы.

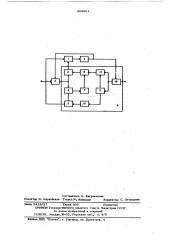

На чертеже приведена структурная электрическая схема предложенного устройства.

60622 1

Э

Синхронизатор несущей частоты содержит последовательно соединенные перемножи тель

1, приемник 2 символов и управляемый генератор 3, объединенный по входу с перемнсжнтепем 1, между выходом управляемого генератора 3 и другим входом перемножитепя 1 включен блок 4 контроля и установпения сянхрониэма фазы, другие входы которого соединены с выходом приемника 2 символов и входом перемножитепя 1, 10

Блок "Ф контроля и устаиов4жния синхро низма фазы состоит из поспедоватепьно соеаинениых первого бпока 5 совпадения, фазового детектора, 8, первого бпока 7 задержки, триггера 8 и фаэоврааатепя 9, другой вход

koroporo соединен с другим входом фазового детектора 6 ° причем выход решающего блока

10 через поспедоватепьно соединенные вто рой блок 11 задержки и формироватепь стробимпупьсов 12 подкпючен к входу перво1.о бпока совпадения 5, а через второй блок

13 совпадения к другаиу щюду триггера

8, ври атом другой выход второго бпока

11 задержки подклеен к другому входу втереге бпока 13 совпадения, причем другие ииФы фазовращатепя 9, фазового детектора

6, блока 5 совяадения и вход решающего бежа 1О, а также выходы фаэовращателя 9 и рещакнцего блока 10 авпяюиж соответствующими входами и вьииаами бпока 4 контроля зо и установпения синхрснизма фазы.

У с тройс тво pa6oreer следующим об разом.

На один вход перемножитепя 1 поступает ,входной фаэоманипупированный сигнал, а на другой вход - сигнап с управляемого гене- 3е ратора 3 через фазовращатепь 9. На выходе перемножитепя1 потщатся "1, если входные сигнапы совпщьмот ио фазе, и "-1", если входные сигналы воступвют в противофазе. Ириемиик 2 симвопов выходным сн 40 налом воздействует на управпяемый генератор 3 и решающий баок 10 системы цикповой синхронизации. Решающий блок 10 выраба тывает сигнал тревоги при отсутствии сигнала цикцовой синхронизации. Отсутствие сигнана цикповой синхронизации на протяжении нескольких поспедовательных циклов свндетепьствует; о том, что нроизошел случайный перескок" фазы, в результате чего происходит "обра ная работа.

Сигнал тревоги с решающего блока 10 поступает на один вход второго блока 13 совпадения тракта защиты непосредственно, а на другой его вход - через второй блок

11 задержки, обеспечивающий o"àäåðæêó на время длительности цикла (Тц), за которое осуществляется контроль синхронизма фазы, При этом входной сигнал через первый блок

«5 совпадения, откры заемук строб-нл;.пульсол с выхода формирования строб-импульсов 12, поступает на один вход фазового детектора

6, на второй вход которого подается сигнал с выхода управляемого генератора 3.

Если сигналы совпадают по фазе, то фазовый детектор 6 через первый блок 7 задержки. выходным напряжением удерживает триггер 8 s исходном состоянии,,и сигнал тревоги от решающего бпока 10 через второй блок совпадения 13 не воздействует на фазовращатепь 9. Следовательно, тракт защиты предотвращает ложное срабатывание фазоврашатепя 9 в спучае отсутствия "обратной работы. Еспи фазы входных сигналов фазового детектора 6 не совпадают, то выходной сигнал фазового детектора 6 опрокидывает триггер 8, и фазоврашатепь 9 изменяет фа зу колебаний с выхода управляемого. генератора 3 най радиан.

Формупа изобретения

1. Синхронизатор несущей частоты, ссщер жащий поспедоватепьно соединенные иеремножитель, приемник симвопов и упрввпяемый генератор, объединенный ио входу с перемножитепем,о тл; н чаю щий с я тем, что, с цепью повйшениа точности синхронизации сигяапов несущей частоты, между выходом управляемого генератора и др гим входом иеремножнтепя включен бцок контропя и установления синхронизма фазы, другие входы которого соединены с выходом приемника символов и входом перемножителя.

2. Синхронизатор и. 1, о т и и ч а юшийся тем, что, блок контроля и установления синхронизма фазы состоит иэ последовательно соединенных первого блока совпадения,:фазового детектора, первого блока задержки, триггера и фаэоврашатепя, другой вход которого соединен с другим входом фазового r атектора, причем выход решающего блока через последовательно соединенные второй блок задержки н формнроватепь стробимпупьсов подключен к входу первого блока совпадения, а через второй блок совпадениях другому входу триггера, при этом другой выход второго блока задержки одкпючен к другому входу второго блока совпадения, причем другие входы фаэоврашатепя фазово- го детектора, блока совпадения и вход решающего блока, а также выходы фазоврашатепя и решающего блока являются соответствук . шими входами и выходами блока контроли и установления синхронизма фазы.

Источники информации, принятые во внимание при экспертизе:

1 ° Дж.Дж. Стнффпера Теор я синхронной связи, М., "Связь", 19 5, =. 243 44.

60622 1

Составитель Л. Каграманова

Редактор H. Марховская Техред М, Келемеш Корректор С. Патрущева

Заказ 2418/37 Тираж 805 Подписное

UHHHllH Государственного комитета Совета Министров СССР по делам изобретений и отк1оытий

113035, Москва, ЖЭ5, Раушскаа наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4