Устройство цифровой фильтрации на основе дискретного преобразования фурье

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 607224 (61) Дополнительное к авт. свил-ву (22) Заявлено 27.03.75 (21) 2117520/18-. 24 с присоединением заявки № (23) Приоритет (43) Опубликовано 150578.Бтоллетень ph18 (51) м. KJt.

С 06 F 15/34

Гоа1даратееааыМ ааматет

Саеата Минаотрае СССР оо .делам азобретенай а открытей. (58) УДК 681.18 (088. 8) (45) Дата опубликования описания 260478

Г.Д.Бахтиарон и A.Þ.ÒèùåHêo (71) Заявитель (54) УСТРОЙСТВО ЦИФРОВОЙ ФИЛЬТРАЦИИ НА ОСНОВЕ

ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ

Изобретение относится к области цифровой вычислительной техники, а именно к области цифровой Фильтрации, использующей дискретное преобразование

Фурье (ДПФ) ° Устройство может найти применение при цифровой обработке простых и линейно частотно-модулировайнйх сигналов н гидро-, звуко- и радиолокации а также н аппаратуре связи, наt

10 нигации и телеметрии и других областях техники, йспользующих подобные сигналы.

Известны устройстна цифровой Фильтрации $1$, содержащие дна ны чслителя прямого ДПФ и один вычислитель обратного ДПФ,. три умножителя комплексных чисел и четыре промежуточныХ блока памятй.

Недостатками известных устройств Ж являются значительная аппаратурная сложность и ограниченность функциональных возможностей.

Наиболее близким по технической сущности к изобретению является устрой-Я ство цифровой фильтрации на основе

ДПФ $2$ содержащее два смесителя, два аналого-цифровых преобразователя, умножитель комплексных чисел, блок памяти, процессор быстрого преобразова- 80

2 ния фурье и детектор. ПРичем входы аналого-цифровых преобразователей через соответствующие смесители соединены с входом устройства, первый выход блока памяти подключен к первому входу умножителя комплексных чисел, первый выход которого соединен с первым входом процессора быстрого преобразования

Фурье, Недостатками известного устройства янляются черезмерно большой объем аппаратуры и слабая помехозащищенность по отношению к мешающим сигналам гармонического характера.

Цель изобретения — упрощение Устройства и повышение его надежности °

Это достигается тем, что в устройство ннедены первый и второй коммутаторы, первый, второй и третий регистры сдвига, первый, второй и третий сумматоры и элемент задержки, Причем ныходы первого и второго аналого-цифровых-преобразователей соединены через первый коммутатор соответственно с вторым и третьим входами умножителя комплексных чисел, четвертый вход которого соединен с вторым выходом блока памяти. Второй выход умножителя комплексных чисел соединен через первый регистр сдвига

607224 входом п<а Jc»ccopg быс<"ро)"o преобразован(.я ФЬ -bec первый ны":<ад котаРого непас17едс <. ванно,. а второй через BTQ)7og pcгн-. р сдвига соединены соатн(."c Y)»:,"»<< "..") г"с -:г:.зэ"ч)ым H нта17ым B«<7 да«<ж и -ОРОПGк,Оммутата<за .-. <1 ерный Вы ход втор<)го к<)мм;<тат(7т)л через тр(» (ий

Регистр сдвига соединен с первыми входами пеРВОго к нтара) c) сум<матаран нтО рай нь)хад второго коммутатора <."аединен с вторыми в><одами первого и второго 10 сумматоров „„. Выход II

KQTQpQx»o соединен с входам:детекг<)ра.

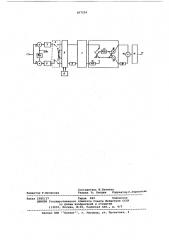

Выход детет<тара является выходом устройства. чертеже !- <-Дстанлена (эт< р i< T.. рная 2О схима ) стройся<. в)<

<.;Игнал е )) <а)<а ), через смеситель

2 поступает ка аналога-цифровые преОбразОнатели .) Б полученные таким Об разам два кв<)лР<зтурных «акала поступают на КОммутатар 4 ) KGTG1)ый наЩ)анляет четные выборочные зка<)ения H

Один, а нечетные на д1)угой BKozb) двухканальbGго умкожкTеля;:) комп)

Фильтра, <" .выходов умнажителя скгиалы пРОхОДят на входы пранессОра 7 быстрого преобразования Фурье, по верхней шине непосредственна, а па нижней=:через регкстр сдвиг" Я, 35

Ка Оба ВХОДЯ працессОра сначала ,поступают отсчеты, относящиеся к первому каналу {четные на верхний нхад), а в течение следуп <кх И тактов посту- 4О пают Отсчеты выборки нтарага канала. процесса17 7 с Регистром сдвига 8, также ко))мутатор 9, ре истры сдвига

1О 11, суммат<.ры 12, 1З„И 14 =» емент задержки )Á можно рассматринать 45 как мОдифициРОванный прОцессор< осуществляющий прямое бысTpo& преобразана ние Фурье выборки длиной 2 И отсчетов.

Модификация процессора вызвана тем, чта в нем при обработке двух различных 5О каналов данных используются различные

ВЕКТОРЫ ПОВОРата < CC G.< rq<»TOT ) <НЦК< ПОЛ ному преобразованию Фурье выборки длиной 2 И отсчетов.

Сигналы с выходов сумматоров 12. и

13 суммируются н соответствии с алгаРИТМОМ СЕКЦИОНИРаваНИЯ С СУММИРОнr)HH— ем в сумматоре 14, причем нижний выход соединен с сумматорам 1,. черн".; элемент задержки 15 длиной Я слоев, <" ны)<ада сумматора 14 сигнал поступает на нхо- ды цифрового детектора 16, выход которога является выходом 17 устройства.

Использование предлагаемого устройства уже при н и 2 дает уменьшение его оба<его объема примерно н два раза.

Формула изобретения

Устройство цифровой фильтрации на основе дкскретнага,преобразования

Фурье, содержащее дна смесителя, два аналого-,<цифровы« преобразователя, комплексных чисел, блок памяти, процессор быстрого преобразования Фурье и детектор, причем входы аналого-цифровых преобразователей через соответствующие смесители соединены с входом устройства, перный ныхад блока памяти подключен к пернаму входу умножктеля комплексных чисел, первый выход которого соединен с пер-, вым входам процессора быстрого преобразования Фурье, о т л и ч а ю щ е ес я тем,. что, с целью упрощения устройства и паны(<)ения его надежности, н него введены первый и второй коммутаторы, первый, второй и третий регистры сдвига, первый, второй и третий сумматоры и элемент задержки, причем выходы первого и второго аналого-цифровых преобразователей соединены через первый коммутатор соответственно с нторым и третьим входами умножителя комплексных чисел, четвертый вход которого соединен с нтарым выходам блока — а.м,яти, второй выход умножителя комплексных чисел соединен через первый регистр сдвига с вторым входом процессора быстрого преобразования

Фурье, первый выход котарога непосредственно, а второй через второй Регистр

<двига соединены соответственно с первым и вторым входами второго коммут)тора, первый выход которого через третий регистр сдвига соединен с пер" ными входами первого и второго сумматоров, второй выход второго коммутатора соединен с вторыми входами первого и нтарого сумматоров, выход .Перво- го сумматора подключен к первому входу третьего сумматора, выход нтарого сумматора соединен через элемент задержки с вторым входам третьего сумматора, выход которого соединен с входом детектора, выход детектора является выходом устройстна.

Источники информации, принятые во внимание при экспертизе".

1. Патент CMA Р. 36<<0195, кл. 343-17, 2P, < 1964.

2.HeI H J.È.,áÐe<)I1B L. ДРРбсаба)< df PIфе1)н< ГРТ k.ech)I<)P<)gy <и )а< а)" ь<фио0 а)<<)

<)аЫ yr oceein ô, )«)н<ре )вн(),ий "EAGAN 71 !

607224

Составитель Й.Палеева

Техред А, Богдан Корректор С.Гарасиняк

:Редактор T.Þð÷èêoâà

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Эаказ 2585/37 Тираж 826 Подписное

GHHHIIH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5