Устройство цифровой фильтрации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11)б07225 (61) Дополнительное к авт. свид-ву— (22) Заявлено 1507,76 (21) 2385670/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 150578.Биоллетень pk 18 (45) Дата опубликования описания 260478

2 (51) М. Кл. (06 % 15/34

Гоотннротввнннн новнтвт

Соввтв Мнннвтров СССР во нвнав наобрвтвннй н открытой (5З) УДК 681. 14 (088.8> (72) Авторы изобретения

Ю. С. Ицкович, Н. Н. Немаилов, Л. И. Сулин и А. Н. Шполянский с

Pl) Заявитель (54) УСТРОЙСТВО ЦИФРОВОЙ ФИЛЬТРАЦИИ

Изобретение относится к цифровой обработке сигналов, в частности к цифровой фильтрации и может быть использовано в различных цифровых комплексах. 5

Известно цифровое устройство, выполняющее дискретное линейное преобразованиеи е си гнала, содержащее блок памяти, блок хранения коэффициентов умножитель и накапливающий сумматор. 10

Это известное устройство имеет низкое быстродействие и значительную конструктивную сложность. Наиболее близким к изобретению по технической сущности является цифровой фильтр, содержащий 15 первый, второй и третий регистры сдвига и первый и второй знаковые регистры, комбинационный сумматор, причем выход сумматора соединен со входом третьего регистра. сдвига, выход треть- ® его регистра сдвига соединен со входом комбинационного сумматора, со входом второго знакового регистра и с группой входов второго регистра сдвига, вход первого знакового регистра и 25 группа входов первого регистра сдвига являются входами устройства, выход третьего регистра сдвига является выходом устройства. Однако этот известный фильтр характеризуется возможны- ЗО ми сбоями в работе иэ-за помех и мгновенных пропаданий напряжения, что обусловлено конструкцией блока хранения коэффициентов, а также тем, что фильтр предназначен только для обработки однополярных сигналов.

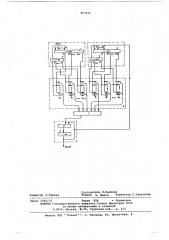

Целью изобретения является повьыение надежности и расширение класса выполняемых функций. В предлагаемом устройстве это достигается тем, что оно содержит постоянный запоминающий блок н многовходовый сумматор, причем группа выходов первого регистра сдвига соединена с первой группой входов запоминающего блока, группа выходов второго регистра сдвига соединена со второй группой входов запоминающего блока, группа выходов первого знакового регистра соединена с третьей группой входов постоянного запоминающего блока, группа выходов второго знакового регистра соединена с четвертой группой входов постоянного запоминающего блока, а группа выходов постоянного запоминающего блока соединена с группой входов многовходового сумматора, выход которого соединен со входом комбинационного сумматора.

На чертеже представлена блок-="õeèà предлагаемого устройства.

607225 поданных с выхода постоянного запоминающего блока б, сложение в сумма- .торе 8 полученной суммы с содержанием регистра 3 (в начальный момент первого цикла его содержимое равно нулю) и запись полученного результата в регистр сдвига 3. Во втором так:те цикла производится сдвиг на один разряд в сторону младших разрядов ре-, гистров 1, 2 и 3, после чего начинается очередной цикл работы.

Оно содержит регистры сдвига 1,2 и 3, .знаковые .регистры 4 и 5, постоянный запоминающий блок б, многовходовый сумматор 7 и комбинационный сумматор 8. Регистры сдвига 1 и 2 имеют число разрядов Мщ и ЯВ;соответственно и предназначены для хранения чисел без знака. Первые и разрядов регистров сдвига 1 и 2 имеют параллельные входы для приема входных и выходных выборок, соответственно, причем первые разряды регистров сдвига предназначены для старших разрядов выборок, а разряды с номером щ — для младших разрядов выборок. Каждый .Разряд Регистров сдвига 1 и 2, номер .которого кратен числу ltt, имеет выход, соединенный с соответствующим входом постоянного запоминающего блока б. Знаковые регистры 4 и 5 предназначены, соответственно, для хранения знаковых 20 разрядов входных и выходных выборок, Постоянный запоминающий блок б представляет собой набор контактов и перемычек, соединенных так, чтобы обеспечить на его выходе формирование 2д произведения очередного разряда выборок на соответствующие коэффициенты, представленного в дополнительном коде, Очередная выборка входного сигнала поступает на вход регистра 1, а ее знак — на вход Регистра 4. Для вычисления очередной выходной выборки устройство использует (ж + 1) циклов работы, из которых в первых w циклах вычисляются частные произведения, а в (И + 1) - м цикле вводятся поправка.

Каждый цикл состоит из двух тактов.

К началу первого цикла в первые и разрядов регистра 1 записана очередная входная выборка, à в следующих Разря- . дах — предыдущие входные выборки. Аналогично в регистре 2 записаны выходные выборки. В регистрах 4 и 5 записаны знаки соответствующих выборок.

Коды младших разрядов каждой выборки поступают в постоянный запоминающий блок б, на выходе которого при этом формируется И + М, И -разрядных кодов, равных произведению младших разрядов выборок на соответствующие коэффициенты. В первом такте каждого цикла производятся сложение в многовходовом сумматоре 7 частичных сумм всех кодов, По окончании М + 1 циклов работы на выходе фильтра оказывается сформированной очередная выходная выборка сигнала которая записывается в регистры ? и 5, одновременно в регистры

1 и 4 записывается очередная выходная выборка и производятся сдвиг на один разряд знаковых регистров 4 и 5, Далее описанный порядок Работы фяльтра повторяется многократно в течение всего времени фильтрация сигнала.

Вследствие простоты постоянного запоминающего устройства, содержащего набор контактов и перемычек, инфор-" мация о значениях коэффициентов, хранящаяся в нем, не разрушается при действии помех, пря пропадания напря* женил питания и других факторах, что обуславливает высокую надежность устpîéñTàà фильтрации, так как практически полностью исключается воэможность искажения частотной характеристики фильтра. Исключение из устройства фильтрации Регистров; я хранения коэффициентов я схем опроса обуславливает существенное сокращение его габаРитов.

Формула изобретения

Устройство цифровой фильтрации, содержащее первый, второй и третий регистРы сдвига я первый и второй знаковые регистры, комбинационный сумматор, причем выход комбинационного сумматора соединен со входом третьего регистРа сдвига, выход третьего регистра сдвига соединен со входом комбинационного сумма= îðà, со входом второго знакового Регистра я с группой входов второго регистра сдвига, вход первого знакового регистра и группа входов первого регистра сдвига являются входами устройства, выход третьего регистра сдвига является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности и расширения класса выполняемых функций, оно содержит постоянный запоминающий блок и многовходовый сумматор, причем группа выходов первого регистра сдвига соединена с первой группой входов запоминающего блока, группа выходов второго регистра сдвига соединена со второй группой входов запоминающего блока, группа выходов первого знако вого регистра соединена с третьей группой входов постоянного запоминающего блока, группа выходов второго знакового регистра соединена с четвертой группой входов постоянного запоминающего блока, а группа выходов постоянного запоминающего блока соединена с группой входов многовходового сумматора, выход которого соединен со входом комбинационного сумматора.

607225

Составитель Н.Палеева

Техред Зi фанта КорректоР С.Гарасиняк

Редактор Л.Тюрина

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Заказ 2585/37 Тираж 826 Подписное

ItHHHOH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5