Запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е I:, B0-,37В изоь етЕНиЯ(Союз Советских

Социалистических

Республик

1 (6() Дополнительное к авт. свил-ву 1 (22) Заявлено 14.04.75(21)2124919 18 24

5 11 С 11/00

& 11 С 29/00 с присоединением заявки ¹ (23) Приоритет

Гааудврстаенный номнтат

СаВВта Мнннатраа СССР аа делам нзоаретаннй н атнрытнй (43) Опубликовано 1 .О.>, 78, Бюллетень Ка 18 (45) Дата опубликования описания 24.34. I8 (%) УГИ 681.327.6 (088. 8) Л. А. Городипова, В, Г. Деревянченко, А. И. 1<ривоноссв и Д. Н. Мерзляков (72) Авторы изобретения (71) Заявитель (54) ЗАПОМИНАК)ШЕЕ УСТРОЙСТВО

> (з061)ете>>и(ыож(т быть Гlрим He!so t!pH построен и и з;> поминаю>ци:< ?(«i,:)ОЙС 1 Б (ЗУ ) Bblчислительных машин 1!ярялл<льного действия к которым прсдъявля>отея требования устранения Одной неисправности.

ИзВестны ЗЪ < Б котОрых исклк)чеHli(> нсиспряв!!Остей Осу!цсствлястся путем s3ì(HI! (I j > < и

Пере)ос !1;> !!<(x содержит рез(рв! Iос 06орх 10ванче, которо(. замс!пает вышедшее из стро;!.

Не \Ост l Гком эт(?ГО устройст B!I я«1HIOT(я 60;Ее>-; П шис аппа(?>>т pHblc затраты.

Няиб(>ле(близким тсхни !сским рспп?HI!(xl к !1306pcт(1tlt lo HB,. Iя(>тся 3 ), сод(.рж (I Hjo<- ?????? ?? ?? ?? ?? 3 ?? p b c 1, i! (? ?? (. ?? ?? ??, (?? ??! (?? bl ?? 0 b! 1! ?? ??. ??h(??o ??01k??i??????!!bl ?? 0:j?????? ???? ????(>, IC>I(->.i(МЕ>l)ОБ

И !!Срвой и Bгорой грм>>п, другие «ходы кото- 1;рых сосдинс>ы соотвстстве>1110 . l!x!)дами уст-. ройства li Вь!Х<)дами Одноразря jl!i>ix блoKÎE!

ПЯ МЯТИ, 3 ВЫХОДЫ I!

< входам одноразрядныx блоков !!Ямяти и выходам устройства, резервный одноразрядный

>(< блок памяти, управляюецую и коегг(>с)льнь>(шины (2). Недостатками этого 1, яьляютс.: длительное время исключен(H неисправности, В03можная потеря информации по всех разрядах

ЗУ после исключения неисправности, что снижает его 1>адежность. 2, ) Целью изоорстения является повышение >i;!дежности устройства и уменьшение времени ис кл>очения неисправности.

Это достигает< я тем, что у(тройство со,l(. ржит тре ью,:>ствсртую и пятую группы >лсментов И. Причем первые входы элементов И тр(тьей и четвертой групп подклю (е><ы к едини fHblM выходам регистра 3 Ip(03> Бторьи Входы - одноразряд>!<но блока 1 амяти, (I B!>lХОДЫ вЂ” - СООТБЕТСТB(H!IO h ВХОД" Р< ЗЕPВН(>1 од>орязрядного блока памяти и выходам устji>o> ;(Бя. Первые Входы элементов И пятой

:-р. Нпы coE;lliHc ø, с входами устройства, БтоРы(БХОЛ!>! — — С >>>!1Р

«ходами регистра адр(са. Нулевые Выходы !

)е Г>I(тря Ядре(3 подкл юч< ны v Bxo,:ji! м перВОГО

:>лсм(НТЯ И, В!>Iхо.j hoTopo! СО(jilf!(.!l 0 I!(1)«bl:.>и входами второго и тр< гьег(> элемс>! Г(<«1(. ..>Тор»>с Бхоты 110слсдпих по,>к. Iк !с I!!>!;<К) г«« СТБ(HHÎ K БХ() тн<>й K<)l! "!)! > i I !>0» ", !! < Ii B«< >., >Р(3 P 8 i !01 (! ОДI <ОРЯЗРЯ!1111

ХОДЫ < оответс I «(!!!!о !(Бх(<,.>т ih: >сi)l>il:,: (, о 1 HoÃ!33pяд!! ОГ<> ОлОкя пя хl >1) >I и Вь> х< > гнои h(! l . трольп<>и >пине.

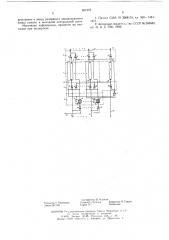

1(3 и )1(жс изображена функ(!110!.:<.:".>11:; < с.<смя . 1, >

607276

Устройство содержит одноразрядHbiL оло1, pf.3CpBHbtff O,IHOpd3pft3HbfA OJIOK

;:амяти 2, блоки 3 и 4 элементов И, регистр адреса 5, состоящий из триггеров б, первый элемент И 7. В блок 3 входят элементы И 8 первой группы, один из входов которых соединены с входами 9 устройства, а выходы — с входами

10 Олоков памяти 1. В блок 4 входят элементы

И 11 второй группы, Одни из входов которых подключены к выходам 12 б.;Оков 1, а вг>под»>к выходам !3 устройства. Д, у: ие входы элементов И 8 и 11 соединень; с нулевыми выходами !

4 триггеров б. В блок 3 входят также элементы И 15 третьей группы, выходы KQTophlx подh2ito÷åíû к вхг>ду !6 олока памяти 2. В блок 4 входят элементы И 17 четвертой группы, одни входы которых соединены с выходом 18 Олока

2, i дрмгие — с единичными выходами 19 григ> 1 гf »ип б ft первыми входам> элементов Л 15.

Вторые входы элементов И !5 подключены к вхо,>ам 9. выходы элемаш нтов И 7 соединены с выходами 13. Кроме того. устройство содержит второй 20 и третий 2! элементы

И, первые входы которых подключены к выходу эдеме>па И 7, вторые входы — соответственно к входной контрольной шине 22 и выходу 18 блока 2, я выходы -- соответственно к входу 16 блока 2 и выходной контрольной шине 23.

Входы элсмш Та И 7 соединены с выходами 14 триггеров 6. Устройство имеет также элементы

И 24 пятой гpi IIIII f, вь>ходы которых иодклк>чены к вя>дям „ 5 триггеров 6, первые входы -- к вх(>дам 9, я вторые входы -- к управляющеи пине 26.

Устройство работает следующим образом.

В исходном сОстОянии нри oTO)1 ñTÂèè сигнала на шине 26 элементы И 24 закрьпы„триггеры 6 реп>стра 5 установлены в нулсвос сосТОЯ нис (ti f> ify 1f>tf!>Ix вы ходах 14 — вы QKlfl Iloтснцнял, а на е.шничных выходах 19 — низкии), элементы И 15, 17 закрыты, а элементы И 8, 11 открыты и пропускак>т сигналы с входов

9 ii;! входы 10 блоков 1, с выходов 12 блоков

l на выходы 13. Высокий потенциал на нулевых выходах 14 триггеров б регистра 5 включает элем;Hã И 7. который открывает элементы И

20, 21, и шина 22. служащая для контроля на четность ЗУ, подсоединяется к входу 16 блока 2, а выход 18 блока 2 >к>дсоединяется к шине 23. Блок 2 выполняет функцию разряда контроля tta четность информации Одноразрядных блоков 1.

При наличии неисправности одного из блоков 1 «iti шину 26 подается сигнал адреса, КоГ торый открывает элем !ITbl И 24. С входоя 0 через элементы И 24 подается код на входы

25 триггеров 6 регистра 5. Код состоит-из нулевых сип алов и единичного сигнала, сг>г>тветстяу>огцего неисправному блоку 1. Единичный

cfffнял устанавливает один из триггеров регистра, в единичное состояние (на единичном выходе 19 -- высокий потенциал, на нулевом яыходс- 14 — низкий!; нулевые сигttялы кода

->Одтверждают нулевое состояние остальных триггеров регистра. Сигнал адреса снимается с шины 26 и элемснть: И 24 закрываются. Триг еры регисtpa;fpoдолжак>т находиться в нулевом состоянии, кроме одного, который перешел в единичное состояние и показывает, что соответствукнций блок 1 неисправен.

Элементы 8, 11, подключенные к нулевому выходу 14 триггера 6 регистра 5, установленного в единичное состояние, закрываются, а элементы И 15, 17, подключенные к единичному выходу 19 данного триггера регистра, открываются и соединяют вход 9 с входом 16 однои разрядного блока 2 и выход 18 блока с выходом 13. При этом неисправный блок 1 блокируется и вместо него подключается блок 2.

Одновременно элемент И 7 выключается, так как на один из его входов подан низкий потенциал с нулевого выхода !4 триггера 6 регистра 5, который установлен в единичное состояние. При этом элементы И 20, 21 выключаются и прерывают пепи для сигналов с шины 22 на вход 16 одноразрядного блока 2 и с выхода

18 блока 2 на шину 23. При этом контроль на четкость в ЗУ не производится.

Таким образом, описанное ЗУ в исходном состоянии (до появления неисправности) работает с контролем на четность, используя для этого оборудование одноразрядного блока 2.

2 При появлении неисправности одного из блоков

1 происходит его блокировка, подключение резервного одноразрядного блока 2 вместо неисправного, отключение контроля на четность ЗУ.

Формула изобретения

Запоминающее устройство, содержащее рез гистр адреса, нулевые выходы которого подклю>ены к одним из входов элементов И первой и второй групп, другие входы которых соединены соответственно с входами устройства и выходами одноразрядных блоков памяти, а выходы подключены соответственно к входам одноразрядных блоков памяти и выходам устройства, резервный одноразрядный блок памяти, управля>ощу>о и контрольные шины, отличающееся тем, что, с целью повышения надежности устройства, о»о содержит третью, четвертую и

4) пятую группы элементов И, причем первые входы элементов И третьей и че-вертой групп подключены к единичным выходам регистра адреcè, вторые входы-соответственно к входам устройства и выходу резервного одноразрядного

Олока памяти, а выходы — соответственно к входу резервного одноразрядного блока памяти и выходам устройства, первые входы элементов И пятой группы соединены с входами устройства, вторые входы — с управляющей шиной; а выходы — с входами регист»а адреса, нулевые выходы регистра адреса

> подключены к входам первого элемента И, выход которого соединен с первыми входами второго и третьего элементов И, вторые входы которых подключены соответственно к входнои контрольной шине и выходу резервного однобо разрядного блока памяти, а выходы — соот607276

Составитель В. Рудаков

Техред О. Луговин Корректор И. Гоксин

Тираж 7!7 Подписное

Редактор Т. 1Орчикова

Заказ 26!7/40

1ГНИИПИ Государственного комитета Совета Министров СССР во дела м изобретений! и открытий!

13035. Москва, Ж-35. Раувнскан наб., д. 4г5

Филиал 11П11 «Г!атснт», г. Ужгород, ул. Г1роек i ная. 4 ветственно к входу резервного одноразрядного блока памяти и выходной контрольной шине.

Источники информации, принятые во внимание при экспертизе:

1. Патент США № 3568153, кл. 340 — 146.1, 1971.

2. Авторское свидетель гво СССР № 263682, кл. G 11 С 7/00, 1966.