Запоминающее устройство типа 2,5 д

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИЛЛЬСТВУ

Союз Советских

Социалистических

Респубпик (11) 607278. i4h,; (Ф. Л :Н I

1 ! (61) Дополнительное к авт. свил-ву (2213аЯвлено 12,05.76 (21)2361152/18-2 (51) М. Кл

& 11 С 11/00 с с присоединением заявки № (23) Приоритет

Государственный комитет

Совета й(нннстров СССР по делам неооретеннй н открытнй (43) ОпУбликовано 15.05,78. Бюллстень №18 (5З) ÓÄÊ628.327,6 (45) Дата опубликования описанияВ4.09. М . (088.8) (72) Авторы изобретения

A. И. Васин, В. И. Агошков, В. С. Грабаров и Ю. Г. Андреев

,71) Заявитель (54) ЗАПОМИНА10ШБЕ УСТРОЙСТВО ТИПА 2,5Д

Изобретение относится к области вычислительной техники и может быть использовано в запоминающих устройствах на магHHTHblx элементах электронных вычислительных машин

Известны запоминающие устройства (ЗУ) на ферритовых сердечниках с выборкой типа

2 5Д (1(Из известных ЗУ типа 2,5Д наиболее близким по технической сущности является ЗУ, содержащее магнитный накопитель с адресным: и адресно-разрядными шинами, адресные к;ммутаторы, один из которых подключен к че. ным, а другой — к нечетным адресным шинам накопителя, адресно-разрядные коммутаторы и регистр информации (2).

Недостатком известных ЗУ типа 2 5Д является большой объем разрядного электронного оборудования, так как число адресно-разрядных коммутаторов равно числу разрядов ЗУ и, как следствие, большая потребляемая ЗУ мощность, определяемая мощностью адресноразрядных коммутаторов.

Целью изобретения является увеличение информационной емкости ЗУ без увеличения чис13;l,÷ðåñHo-разрядных коммутаторов и потребляемой мощности;

Поставленная цель достигается тем, что предлагаемое ЗУ содержит элементы ИЛИ, входы которых подключены к соответствующим выходам регистра информации, выходы — — к управляющим входам адресно-разрядных коммутаторов, выходы одного адресно-разрядного коммутатора подключены к соединенным rioc едовательно адресно-разрядным шинам двух первых разрядов магнитного накопителя, а выходы другого адресно-разрядного коммутатора подключены к соединенным последовательно адресно-разрядным цгинам двух последующих разрядов магнитного накопителя.

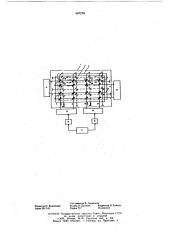

На чертеже. представлена схема ЗУ на четыре разряда.

ЗУ содержит магнитный накопитель 1, сердечники которого расположены в двух параллельных плоскостях 2 и 3 и прошиты адресными шинами 4 — 7, и адресно-разрядными шинами 8 — 11 (для упрощения чертежа показаны только четыре разряда и количество шин ограничено).

Нечетные адресные шйны 4,5 подключены к первому адресному коммутатору 12, а четные шины 6,7 - — ко второму адресному коммутатору

13. Адресно-разрядные шины 8, 9 первой пары разрядов. расположенных в разных плоскос25 тях 2, 3 накопителя .1, соединены последова607278

3 тельно и подключены к общему для перво" пары разрядов адресно-разрядному . коммутатору 14. Аналогично адресно-разрядные шины

10; 11 вторбй пары разрядов подключены к адресно-разрядному коммутатору 15. В цепи управления каждым адресно-разрядным коммутатором включена логическая схема ИЛИ l6, . входы которой подключены к двум разрядам регистра информации 17.

Обмотка считывания прошивает сердечни. ки аналогично как в известном устройстве и 1в на чертеже не. показана.

Работает ЗУ: следующим образом.

В такте считывания одновременно выбираются две адресные шины, например, нечетная шина 4 возбуждается ат коммутатора 12, а четная шина 6 — от коммутатора 13; и по > одной- адресно-раэрядной шине, например 8 и

10, в каждой. паре разрядов накопителя.

Направление адресных и адресно-разряд-. ных токов в шинах выбирается так, что в каждой паре разрядов возбуждаются полным током и переключаются только два.сердечника; один — в плоскости 2, другой — в плоскости

3 накопителя 1. Остальные сердечники, расположеннйе иа выбранных шинах,, возбуждаются полутоком и не переключаются. Например, при положительном направлении тока считыва- 2s ния, указанном на чертеже стрелками, переключаются сердечники !8 и 19, расположенные в плоскости 2 н сердечники.20, 21, расположенные в плоскости 3, то есть переключаются . четыре сердечника, соответствующие четырем разрядам ЗУ, а ток переключения сердечников

22, 23, 24, 25 равен нулю„так как при данном направлении токов выборки происходит их ком-: пенсация в сердечниках. 22, 23, 24, 25.- При смене направления адресных токов считывания на обратное, переключаются сердечники 22, 3g

23 в плоскости 2 и сердечники 24, 25 в плоскости .3, а сердечники !8, 19, 20, 21 не переключаются..

В такте, записи информация записывается в первый и второй. разряд каждой пары-разрядов последовательно, т. е, те же адресные 4В шины 4. и 6; которые возбуждались при считывании одновременно, при записи возбуждают; . ся последовательно со сдвигом во времени на величину длительности импульса тока записи,. например, сначала подается адресный ток эа- 4>

4 писи в шину 4, а затем в щину 6. Соответственно, также поспедовательно со сдвигом подается информация первого и второго разряда каждой пары разрядов от регистра информации l? через логическую схему ИЛИ 16 на коммутаторы 14, 15. В шины 8, 10 последовательно подается ток записи в случае. наличия

«l » в разрядах регистра информации, и не подается ток записи при «О» информации.

Время выборки информации в ЗУ не изменяется по сравнению с известными ЗУ гипа

2,5Д. Суммарная длительность цикла работы

ЗУ увеличивается примерно в 1,3 раза, но использование предложенного способа включения адресных и адресно-разрядных коммутаторов .позволяет в ЗУ типа 2,5Д увеличить число разрядов в два раза (при соответствующем уменьшении числа адресов в два раза) без увеличения числа адресно-разрядных коммутаторов и потребляемой ими мощности, или уменьшить примерно в 1,5 раза количество специального электронного оборудования ЗУ при заданном числе разрядов.

Фори ила изобретения

Запоминающее устройство типа 2,5Д, содержащее магнитный накопитель с адресными и адресно-разрядными шинами, адресные коммутаторы, один из. которых подключен к четным, а другой — к нечетным адресным шинам накопителя, адреснэ-разрядные коммутаторы и регистр информации, отличающееся тем, что, с целью увеличения информационной емкости устройства, оно содержи-. элементы ИЛИ; входы которых подключены к соответствующим выходам регистра ииформации, выходы — к управляющим входам адресно-разрядных коммутаторов, выходы одного адресно-разрядного коммутатора подключены к соединенным последовательно адресно-разрядным шинам двух первых разрядов магнитного накопителя, а выходы другого адресно-разрядного коммутатора подключены к соединенным последовательно адресно-разрядным шинам. двух последующих разрядов магнитного накопителя.

Источники информации, принятые. во внимание при экспертизе:

1. Шигин А. Г. и др. Цифровые вычислительные машины, М., «Энергия», 1975, с. 153 — 160., 2. «Вопросы радиоэлектроники» серия ЭВТ, вып. 5, 1974, е..25, 607278

Составитель В. Гордонова

Техред О. Луговая Корректор H. Тупииа

Тираж 717 Подписное

Редактор H. Каменская

Заказ 2617/40

1(НИИПИ Государственного ионитета Совета Яннистров СССР по дслам изобрг ген нй и открытий

1 13035, Москва, )K-35, Ра у нккая наб., д. 4/5

Филиал ПИП «Патент», г.. Ужгород, ул. Проектная, 4