Устройство для цифрового дифференцирования

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

У (61) И. Кл.

С О6 Г 1ZOZ

Гевударстваавый квматет

Вввета Ианастрав СССР вв делам пзобрвтаавЯ а аткрытаЯ (53) УДКВ81.328 (оев.в) (43) ( (УЯ) Авторы изобретевия

А. А. Липкин и В. И. Агибалов (71) Заявитель (84) УСТРОЙСТВО ДЛЯ UNbPOBOFO ДИФФЕРЕНЦИРОВАНИЯ .

Изобретение относится к области цифровой вычислительной техники и может быть применено при построении цифровых интегри. рующих машин с одноразрядными приращениями, которые часто называют цифровыми дифференциальными анализаторами (ЦДА).

Известно устройство цифрового дифференцирования (!), в котором-на входы нуль-органа (следящего интегратора) подаются с противоположными знаками приращения df диффереицируемой функции f и приращения f .dx; получаемые на выходе, на вход подинтегральной функции которого поступают выходные импульсы нуль-органа df, а. на вход переменной интегрирования — приращения dx аргумента х, по которому требуется дифференцировать функцию f.

Эта схема проста и строится из широко применяемых блоков (интегратор, следящий интегратор), но в ней погрешности формнроsaws производной Г могут достигать весьма больших значений.

Наиболее близким по технической сущности к предложенному устройству является устройство цифрового дифференцировании «2«, содержащее ри цифровых интегратора, блок управления, счетчик к делитель, причем выход первого цифрового интегратора соединен с пер;

2 вым входоа нуль-оргайа, Второй вход которого подключен к выходу второго цифрового ии. тегратора, третий вход-к выходу делителя q первому входу счетчика, четвертый — к выходу третьего цифрового интегратора, а выВход нуль-органа — к первому входу третьего цифрового интегратора, второй вход которого соединен с выходом счетчика, и первому входу второго цифрового интегратора.

Недостатком известного устройства являетта ся низкая точность.

Целью изобретения является повышение. точности цифрового дифференцирования не путем усреднения влияния, либо частичной «ом-. пенсации возникающих погрешностей, а йа.ос,, нове возможно более полного исключения их

1а основных схемных источников. Это достигаетдя тем, что в него введены два узла формирования пачек импульсов, при. чем входы обоих узлов формирования пачек и импульсов соединены с выходом делителя, а первые выходы, обоих узлов формирования. пачек импульсов подключены ко входу делителя; второй выход йервого узла формирования пачек импульсов соединен со входом первого цифрового интегратора, а второй выход вто33 рого:узла формирования пачек импульсов под608l45 ключен ко второму входу второго цифрового интегратора и второму входу счетчика.

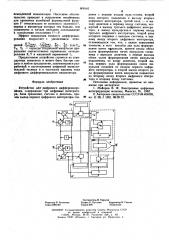

На чертеже показана схема предлагаемого устройства цифрового дифференцирования.

Устройство содержит два одина ковых узла l и 2 формирования пачек импульсов ((p((p(((((eиия dt машинной переменной t. каждый из которых состоит иэ двух клапанов усилителя, одноразрядный двоичный делитель 3, двоичный счетчик импульсов 4. трн интегратора 5„

6, 7 без регистров и и блок сравнения 8, состоящий из двух сумматоров 9 и 1О, регистранакопителя 11 и нуль-органа 12.

Каждый узел формирования пачек импульcos dt имеет входной и выходной клапаны 13, l4, l5 и 16, на входы которых поданы соответственно импульсы приращения переменной интегрирования dx(dy) и машинной переменной dt, а также двоичный делитель !7 и 18.

Выход узла I (его выходного клапана) соединен с входом «+»5, а выход узла 2 — со входом счетчика 4 и входом « — » HHTe(.ðnòoðà 6. ., На 8xoj3, подинтеграл -BGA функции тора 5 поданы импульсы приращения dz, аналогичный же вход интегратора 6 соединен с выходом блока сравнения 8, генерирующего импульсы приращения df искомой производной Г, которые кроме того поданы на вход « — » переменной интегрирования интегратора 7.

Блок сравнения 8 содержит входной сумма вр 9, регистр накопитель 11 со своим сумматором 10 и нуль-орган 12, выход которого является выходом этого блока и всего устройства и целом. Ко входу сумматора 9 подключены выходы интеграторов 5 и 6 (при отсутствии регистров К ими являются выходы кодов про-. изведения П подинтегральной функции на единичное приращение переменной интегрирования}, выход этого сумматора через сумматор 10 присоединен ко входу регистра — накопителя.

Выход одноразрядного делителя 3 подключен еще и к цепям сброса кода из регистранакопителя в регистр раэбаланса нуль-органа 12 и кода из счетчика 4 в регистр подинтегральной функции интегратора 7, для которого регистром К служит регистр разбаланса нуль-органа 12. Первый импульс dx(dy), пришедший на вход узла 1 (2), открывает выходной клапан этого узла. В результате с выхода узла 1 (2) иа вход переменной интегрирования делите. ля и счетчика 3, 4 начинают прступать импульсы приращения машинной персменной (И.Двоичные делители 17 и 18 в узлах 1 и 2 одинаковы и осуществляют деление на целое число N. После прохождения N импульсов (1х((1у) выходной импульс с делителя закрывает входной и выходной клапаны узла l (2} и поступает на одноразрядный делитель 3. Таким образом, пачка, состояц ая нз п (пх), импульсов dt формируется узлом 1(2) на интервале, равном М вЂ” 1 периодов следования импульсов dx(dy).

Число пх импульсов dt в ((aчке, формируемой узлом 2, фиксируется счетчиком 4. По окоичанйи формпрова(((((обеих пачеK вь(ходиой импульс с од((ораэряд((ого дели.(I J!H 3 ATкрывает входные клапаны узлов 1 и 2, после чего каждый из этих узлов получает возможность формирования новой пачки импульсов dt для очередного цикла сравнения.

Импульсы пачек разрешают поступление кодов подинтегральных функций г и f из интеграторов 5 и 6, в блок сравнения 8. Сумматоры 9 и О обеспечивают в каждом цикле сравнения образование в регистре-накопителе 11 этого узла разности !(„кодов z и п„.кодов f (ïðè (о этом коды z и !(не остаются постоянными, так как в ходе цикла сравнения на входы соответствующих регистров интеграторов могут поступать импульсы приращения dz и df().

Момент фиксации разбаланса (окончания цикла сравнения) определяется сигналом с вы(S хода одноразрядного делителя 3, по которому код разбаланса иэ регистра-накопителя сбрасывается в регистр разбаланса нуль-органа 12 блок 8, а код Ь„из счетчика 4 в регистр подинтегральной функции интегратора 7. Знак - импульсов df приращения производно" f, генерируемых нуль-органон 12 определяется знаком кода раэбаланса.

В приведенном выше описании, входы переменной интегрирования интеграторов 5 и 6, .к которым подключаются выходы узлов и 2, определены для случая, когда переменные х и у на интервале исследования монотонновозрастают, и импульсы их приращения dx, dy положительны, Если импульсы dy отрицательны, то пачки импульсов dt с выхода узла 1 должны подаваться на вход « — » (а не «+») переменной интегрирования интегратора 5, Если же отрицательны импульсы dx, то аналогичный выход .второго узла нужно присоединить к входу «+» (а не « — ») переменной интегрирования интегратора 6, N В случае, когда импульсы dx или dy знакопеременны, необходимо обеспечить автоматическую коммутацию цепи связи соответствующего интегратора с узлом или 2. Например, при знакопеременности импульсов dy выход узла 1 можно соединить с обоими входами переменной интегрирования интегратора 5 через клапаны, onин из которых (на входе «-1-») открывается положительными и закрывается отрицательными, а другой (на входе « — ») открывается отрицательными и закрывается пощ ложительными импульсами dy. Если знакопеременные обе последовательности импульсов dx, dy,.òî такие клапаны должны быть установлены на входах переменной интегрирования как интегратора 5, так и интегратора 6.

Так как цифровые дифференциальные сигнализаторы оперируют только с непрерывными переменными, то изменение знака импуль- сов dx(dy) в некоторой точке t означает прохождение производной " " через н нуль и сильное увеличение периода следования импульсов dx(dy) в окрестности этой точки. Точно так же и изменение знака производной 1(сопряжено с ее обнуленнем.

В задачах, решаемых на цифровых дифференциальных анализаторах такие случаи редки, а предложенное применительно к ним схем6в ное осуществление автоматической коммута6081-15

5 ции цепей с помощью клапанов, устанавливаемых иа входах переменной интегрирования интегратора 5 или (н) 6, тривиально.

Импульсы df с выхода нуль-органа 12 поступают не только на вход регистра подинтегральной функции интегратора 6, но к на вход « †» переменной интегрирования интегратора 7, благодаря чему из кода, хранящегося в регистре разбаланса нуль-органа, каждый раэ вычитается код n . После обнуления содержимого регистра разбаланса генерация импульсов

df прекращается. Таким образом, число hf импульсов df, поступающих в результате цикла сравнения в регистр подинтегралькой функции интегратора 6 компенсирует ту ошибку в значении производной Р, которая имела место в этом цикле и, будучи п„.раз переданной в регистр — накопитель, определила сформированный в нем код разбаланса.

Впрочем, в действительности вероятность обнуления регистра нуль-органа 12 весьма мала, так как ошибка hf, как и само истинное значение функции f, за время цикла сравкення не остается постоянной. Поэтому код разбаланса в общем случае не кратен значению и„.

Однако это приводит лишь к тому, что после выработки значения Af с избытком в одну единицу знак содержимого регистра разбаланса начинает изменяться с каждой машинкой . итерацией, н с той же частотой происходит пульсация единицы в младшем разряде регистра подинтегральной функции интегра.тора 6, что практически равнозначно обнулению регистра разбаланса и постоянству кода f . Обновление последнего (измеиение на величину Л19 начинается. сразу после сигнала об окончании цикла сравнения и завершается либо на интервале между двумя последовательными циклами, либо в начале очередного цикла сравнения. Естественно, что и в этом цикле.сравнения код разбалакса в регистре-накопителе узла 8 из-за переменности производной Р в общем случае окажется опять ненулевым. Легко видеть, однако, что при достижении истинного значения f он будет весьма мало отличатьск от нулевого.

В самом деле, если бы цикл сравнения начался в момент одновременного поступления приращений dx u dy закончился через промежуток времени Тф — в момент следующего одновременного поступления импульсов dx и ду и каждый импульс dy вызывал бы при этом выдачу на сумматор блока сравнения кода z, а Каждый импульс dx — кода (1 ), то при истинном значении последнего в результате этого цикла в регистре-накопителе действительно образовался бы нулевой код разбаланса. При таких условиях за время Т,. прошло бы П, импульсов dy, следующих с периодом Т» и п „импульсов dx, следующих с периодом Т„, т.к. имело бы место

ТтЬ „y=Т„п„ = T откуда к пу

Но в предложенной схеме числа п„и п„импульсов dt в пачках, формируемых узлами 1,2

6 и также управляющих поступлением кодов z н (-f ) в блок сравнения 8, определяются как

ny =--(И вЂ” 1) -" —, Т.

Тч

Д 1) Т1

) где ҄— период следования машинных итераций (импульсов dt). Таким образом, н здесь имеет место то же соотношение

n . Т, и<

Заметим, что это сооткои)ение не является вполне точным, потому что зкачения периодов Т. и Тт эа время цикла сравнения Т« не остаются постоянными. И дело здесь не только и ке столько в изменении производных от Х и 1 за малое время Т», сколько в особенностях работы цифровых дифференциальных анализаторов. Ведь даже в том случае, если приращения dx (dy) формируются цифровым интегратором, в регистре подинтегралькой функции которого хранится постоянный код, а ка вход переменной интегрирования поступают импульсы dt приращения машинной переменной, последователькые значения Т, (Тт), измеряемые числом периодов Т„, часто отличаются друг от друга на единицу, потому что коэффициент заполнения регистра подинтегральной функции ке представляется простой дробью: вида !

При достаточно больших значениях отношении — э — и — "- (которые всегда являются

Т Ч

Tf4 Т„ целыми числами) это ке имеет существенного значения и делителями I? к 18 узлов I и 2 целесообразно реализовать число N =-2.

Ио при малых значениях -- х- и — может

Т

1 Тм оказаться выгодным увеличить это число во избе>какие частых появлений поправок hf с чередующимися знаками в значения искомой производно" f .

Правда, с возрастанием N снижается час4О тота обновления значения производной f Поэтому выбор величины N должен в каждом случае сообразоваться как со значениями отношений — — и — так к с ожидаемой скот рф !я ростью изменения функции Р, в соответствии с чем в делителях 17 и 18 узлов 1 и 2 надле-. жит предусмотреть обратные связи между их выходами и входа ми их двоичных разрядов. подключаемые нужным образом тумблерами, Эффект повышения точности выполнения операции дифференцирования предлагаемым устройством, по сравнению с прототипом и другими иэвестнымн его модификациями, определяется применением блока сравнений, в ко. тором правильность полученного значения производной проверяется ка основе сопоставления полных, а не квактоваккых изменений соотИ ветствующих интегралов (перекосом регистров иэ интеграторов в блок сравнения», рациональной организацией циклов сравнения с помощью узлов Iк2,,к, наконец, использованием интегратора 7 для определения ошибки Л! в значении производной f имевшей место в проведенном цикле сравнения, и ее

608! 45

Формула иэобретеиия

Редактор Р. Антонова

Заказ 2801/32

liHHHllH Государствеиного комитета Совета Министров СССР но делам изобретений н открытиИ

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Филиал Г1Г1П <Патент>, г. Ужгород, ул. Проектная, 4

Х ,Иемедленйой компенсация. Последнее обстоятельство приводит к устранению неизбежных для прототнпа колебаний формируемой функцйй f относительно ее истинного значения !, ПЕрйОд и амплитуда которых тем боль1пе, чем уйомянутое в начале описания запаздывание в определении отклонения Р— f .

Эффект повышения точности дифференцирования возрастает с увеличением отноШЕНйй ."","", «1-.»",, -Т -à — (где Т (in Гм Чн

Ту, Тм — периоды следования импульсов приращения соответственно переменных интегриРования.Х, Y и машинной переменной t1.

Предлагаемое устройство строится иэ стандартных элементов н может быть быстро создано в любом предприятии, занимающемся разраб1угКой и изготовлением цифровой вычислительной техники и в частности машины типа цифрового дифференциального анализатора.. Устройство дЛя .цифрового дифференцирования, содержащее три цифровых .интегратора; блок сравнения, счетчик и делитель, причем выход первого цифрового интегратора соее динен с первым входом нуль-органа, второй вход которого подключен к выходу второго цифрового интегратора, третий вход — к выходу делителя и первому входу счетчика, четвертый к выходу третьего цифрового интегратора, а выход нуль;органа-к первому входу третьего цифрового интегратора, второй вход которого соединен с выходом счетчика, и первому входу второго цифрового интегратора, отличающееся тем, что; с целью повышения

19 точности, в него введейы два узла формирования пачек импульсов, причем входы обоих узлов формирования пачек импульсов соединены с выходом делителя, а первые выходы обоих узлов формирования пачек импульсов подключены. ко входу делителя, второй выход первого узла формирования пачек им пульсов соединен со входом первого цифрового интегратора, а второй выход, второго узла формирования пачек импульсов подключен ко второму входу второго цифрового итеграЭ1 тора и второму входу счетчика.

Источники информации, принятые во внимание при экспертизе:

1. Майоров В. Ф. Электронные цифровые интегрирующие машины, Машгиэ, М., !962.

2. Авторское свидетельство СССР Ì 404095, кл. G 06, J 02, 08.09.72.

Составитель В. Тарасов

Техред О.Луговая Корректор И. Гокснч

Тираж 826 Подписное