Время-импульсное множительно-делительное устройство

Иллюстрации

Показать всеРеферат

ИЗОБРЕТЕНИЯ

Союз Севетсиив

Сецнанистнчесиик

Раснубпии

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву (22) 3аяВЛЕНо 11057б (23) 2359855/24 (Ч) М. Кл.

6.05 Ф 7/161 с присоединением заявки %

Гещеретеееев1 ееветет

Вееете Меееетрее 666р ее 4ееев 19ееретееее е етеритей (23) Приоритет (43) Опубликовано 250578.Бюллетень %19 (45) Дата оп бликования описания 060578 (Р) УДК Е81.aa>

{088 8) (72) Автор. изобретения

И.В.Герасимов

P1) Заявитель ленинградский ордена ленина электротехническнт) институт им. В.И..Ульянова {Ленина}

{54) ВРемя-иипульснОе мнОжительнО-делительнОе

УСТРОЙСТВО

Изобретение относится к аналоговой и комбинированной вычислительной технике и позволяет выработать напряжение постоянного тока по множительно-делительной зависимости 5

8,8g о g {1)

3 где V 0 — значение напряжения источника опорного напряжения 30 пос гоянного тока;

81,8,.8 — относительные длительности входных широтно-модулированных сигналов {ИИИ);

V — выходное напряжение посто- )5 янного тока),4).

Такие устройства находят широкое применение в информационно-вычислительных и управляющих системах, обрабатывающих широтно-импульсную инфор- ВО мацию, а также в ряде других систем.

Известны устройства,в которых выходной сигнал, подчиняю.бийся множительно-делительной зависимости, представлен в широтно-импульсной форме(2). N

В этих устройствах выполняется демодуляция входных широтно-модулированных сигналов согласно операции деле- ния с одновременным умножением на величину напряжения источника опорного ЗЭ напряжения постоянного тока. Такие устройства являются наиболее близким техническим решением к предложенному время-импульсноМу множительно-делительному устройству. Они содержат операционный усилитель постоянного тока, в цепь обратной связи которого включен сглаживающий конденсатор, параллельно которому включены последовательно соединенные первый масштабный резистор и первый ключ, а входная цепь операционного усилителя содержит последовательно соединенные источник опорного сигнала, второй ключ н второй масштабный резистор, управляющий вход первого ключа является первым входом устройства.

Недостатком такого множительно-делительного устройства является невозможность выработки напряжения постоянного тока согласно множительно-делительной зависимости при широтно-импульсной форме представления сомножителей.

Цель изобретения — расширение класса решаемых задач н повышение точности выполнения множительно-делительной операции, Это достигается тем, что устройстso содержит инверторы, элементы И, 608171

ИЛИ и параллельно соединенные цепочки, включенные между выходом источника опорного сигнала и входом операционного. усилителя постоянного тока, причем первая цепочка состоит иэ последовательно соединенных первого и второго

5 дополнительных ключей, общий вывод которых через последовательно соединенные первый дополнительный масштабный резистор и первый дополнительный. сглаживающий конденсатор соединен с )О шиной нулевого потенциала, а вторая цепочка сосгоит иэ последовательно соединенных дополнительных ьторого масштабного резистора, второго сглаживающего конденсатора, третьего масш- 15 табного резистора, обкладки второго дополнительного сглаживающего конденсатора через дополнительные третий и четвертый. ключи соединены с шиной нулевого потенциала, входы первого эле- 20 мента ИЛИ соединены с вторым и третьи: входом устройства, выход первого мента ИЛИ соединен с управляющими входами третьего дополнительного ключа непосредственно и четвертого дополнительно."о ключа через первый инвертор, первые входы второго элемента

И и второго элемента ИЛИ соединены с четвертым входом устройства, а вторые входы соединены с первым входом первого элемента ИЛИ, выход второго элемента И через второй инвертор и выход второго элемента ИЛИ соединены с вхо дами третьего элемента И, выход которого соединен с управляющими входами 35 второ; о дополнительного ключа непосредственно и первого дополнительног ключа через третий ипвертор, а управляющий вход второго ключа соединен с выходом второго элемента И.

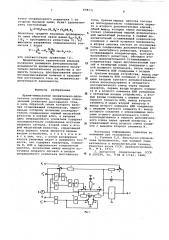

На фиг.l изображена функциональная схема устройства; на фиг.2 даны временные диаграммы, поясняющие Работу устройства.

Оно содержит операционный усилитель постоянного тока 1, в цепь об- 45 ратной связи которого включены последовательно соединенные ключ 2, масштабный резистор 3 и сглаживающий конденсатор 4, входная цепь операционного усилителя содержит последователь- 80 но соединенные источник опорного сигнала 5, ключ б и масштабный резистор

7, управляющий вход ключа 2 язляется одним из входов устройства, и гаоаллельно соединенные цепочки, одна из 55 которых состоит из последов".òåëüíî соединенных ключей 8, 9, общий вывод которых через последовательно соединенные масштабный резистор 10 и сглаживающий ко:.денсатор 11 соединен с 60 шиной нулевого потенциала, а вторая цепочка состоит из последовательно соединенных .»асштабного резистора 12, конденсатора 13 и масштабного резистора 14, обкладки =глаживающего кондепсатора 13 через ключи 15, 18 соедине65 ны с шиной нулевого потенциала, элементы И 17, 18, элементы ИЛИ 19, 20, инверторы 21, 22, 23, первый вход элемента И 17 и входы элемента ИЛИ являются входами устройства.

Принцип расширения функциональных воэможностей устройства и повышения точности выполнения им множительноделительной операции состоит в .следующем.

Известно, что е,е -„((8, e,I -(В,-e,} ). т>

Путем введения логических операций выделения мАкс. (8,, 6,) и мин (В : 8,) возможно сформировать ) 8 = 6 1 за счет выполнения операции вычитания млкс (,9,, 6 ) — мин (б,, Ь ), (Ъ) при которой вычитаемое никогда не превосходит уменьшаемое. Последнее необходимо при реализации операции вычитания широтно-модулированных сигналов средствами цифровой вычислительной техники, когда млкс(6, 9 ) и мин (9„, g, ). формируются соответственно с помощью элементов ИЛИ и И, а операция вычитания — с помощью инвертора элемента И. Операция сложения широтномодулированных сигналов также осуще" ствляется с помощью цифровых логических схем, но с тем ограничением, что относительные длительности 81 и 8, не должны превосходить 0,5 и отсчет каждой из них имеет место от переднего и заднего фронтов соответственно.

На фиг.2 (см. кривые 1,2,4) представлены ШИМ-сигналы, длительности котоРых отсчитываются от гередних фронтов, и (см. кривая 3) второй ШИМ-сигнал, длительность которого отсчитывается от заднего фронта.

С учетом соотношения (3) выражение (2) преобразуется к моделирующему входной цепью предполагаемого устройства уравнению

G(e„e,1:Ka,e;K((e, ВД -(» (Ь„В,)-» M(e„a,)1 )Я где ((— коэффициент пропорциональности; ф 8 - среднее значение проводимости входной цепи операционного усилителя 1 постоянного тока.

Устройство работает следующим образом.

Ha его первую входную клемму поступает (лИМ-сигнал (см.фиг.2, кривая 4) с относительной длительностью 8 стсчитываемой от переднего фронта, причем синхронизация этого сигнала относительно других входных сигналов

608171

10 ос= заь, (s) 6

С 11 Р 14 ÇàÐ 1„= 1 РаЗР (Ò" t<< ) устройства не является обязательной.

Этот ШИМ-сигнал управляет средним значением проводимости двухполюсника, включенного в цепь обратной связи операционного усиди еля 1, состоящего из резистора 3 и ключа 2. Как известно, среднее значение проводимости такого двухполюсника, зашунтированного сглаживающим конденсатором 4, пропорционально 8, т.е. где Cr — среднее значение проводимости цепи обратной связи операционного усилителя 1; 18

G> — проводимость резистора 3.

На вторую, третью и четвертую входные клеммы устройства соответственно поступает ШИМ-сигнал с относительной длительностью а 2,,отсчитываемой от 20 переднего фронта (см.фиг.2, кривая 2), ШИМ-сигнал с относительной длительностью . 81, отсчитываемой от переднего фронта (см.фиг.2, кривая 1), и

ШИМ-сигнал с относительной длитель- 2) ностью 62,, отсчитываемой от заднего фронта (см.фиг.2, кривая 3) и рав. ной по величине относительной длительности 9 . Входные элементы И 17 и ИЛИ 19 вырабатывают ШИМ-сигналы со- 3(} ответственно с минимальной 86л»ин (6» e+)

2 (см.фиг.2, кривая 6) и максимальной е,рмлкс(81,6+) (см.фиг..2, кривая 5) относительными длительностями, причем упомянутые ШИМ-сигналы синхронны по переднему фронту. На выходе элемента

ИЛИ 20 формируется ШИМ-сигнал с относительной длительностью ед=а»+62 (см. фиг.2, кривая 9), который через инвертор 23 управляет ключом 16 и непосредственно:ключом 15. Выходной ШИМ-сиг- 40 нал элемента И 17 через инвертор 22 (см.фиг.2, кривая 7) поступает на первый вход элемента И 18, на второй вход которого поступает ШИМ-сигнал с относительной длительностью 8,1= млкс (61,8 ) 4б с выхОда элемента ИЛИ 19. В результате выполнения операции конъюнкции на выходе элемента И 18 формируется разностный ШИМ-сигнал с относительной длительностью, равной Ос=о -86= млкс(618 )-50

-иии (81,8 ) (см.фиг.2, кривая 8) . Последний через инвертор 21 поступает на управляющий вход ключа 8 и непосредственно на управляющий вход ключа 9.

В установившемся режиме приращение 85 заряда на конденсаторе 11 за период коммутации ключей 8, 9 равно нулю, т.е. пренебрегая пульсациями напряжения на конденсаторе 11 {последнее справедливо при достаточно большой его емкости), можно записать уравнение баланса зарядов в виде

raeI>z> — ток заряда конденсатора 11>

Т;1 — время замкнутого состояния ключа 8;

1раьр- ток разряда конденсатора 11; т t11 — время замкнутого состояния ключа 9;

Т вЂ” период коммутации ключей 8,9.

Заметим, что ключи 8л9 работают в противофазе, Принимал во внимание значения токов заряда 1 и разряда 1 раЗр из (6) можно вывести, напряжение на конденсаторе 11, которое равно где 8„ "- р„/Т вЂ” относительная длительность ШИМ-сигнала, управляющего ключом 8;

7о — напряжение опорного источника 5. постоянного тока.

Аналогичным путем можно показать, что в установившемся режиме напряжение на конденсаторе 13 будет определяться как гце 6 — относительная длительность

ШИМ-сигнала, управляющего ключом 15..

Заметим, что ключи 16 и 15 работаютв противофазе. Знак минус в выражении (8) означает, что токи в резисторах

12 и 14 имеют противоположные направления.

Согласно полученным выражениям (7} и (8} среднее значение тока, втекающега в суммирующую точку операционного усилителя 1 со стороны второй и третьей входных цепей, равно

1 "УР (811(1-611)" e„(("e„)j (9) где 6 — проводимость резисторов 10, 12 и 14.

С учетом того, что

8,„* -. (ь„, а,) - - (е„а,)-1в„- е, I, Ь=61+аЪ /(}2-(} = 4/у выражение (9) можно представить н виде

oG(l 1 e l (1 82) " 1 2) Жр& (2мин (8«6>)+ Ч 8162) .

Если проводимость резистора 7 выбрать вдвое большей, чем проводимости резисторов 10, .12, 14, и обеспечить управление ключом 6 с помощью ШИМ-сигналов с относительной длительностью

Ь « „„ (0,, которые формируются на выходе элемента И 17, то очевидно, среднее значение тока, втекающего в суммирующую

6081 7q точку операционного усилителя 1 со стороны входной цепи, будет удовлетво" рять соотношению

I<=I+2V &vua (61,9у) Ч ЗЕ ф

Поскольку среднее значение проводимости цепи образиной связи равно С = 9

ЮС (6 — проводимость резистора 3), то выхоцное напряжение операционного усилителя 1 будет

? ае

f0 — Ь „р,4 а4, что соответствует уравнению (1) .

Предложенное техническое решение позволяет расширить функциональные возможности время-импульсного множительно-делительного устройства и повысить точность преобразования широтно-модулированных величин и напряжение постоянного тока по множительно- 20 делительной зависимости.

Формула изобретения

Время-импульсное множительно-делительное устройство, содержащее операционный усилитель. постоянного тока, в цепь обратной связи которого включен сглаживающий конденсатор, парал- З0 лельно которому включены последовательно соединенные первый масштабный резистор н первый ключ, а входная цепь операционного усилителя содержит последовательно соединенные источник опорного сигнала, второй ключ и второй масштабный резистор, управляющий вход первого ключа является первым входом устройства, о т л и. ч а ю щ ее с я тем, что, с целью расширения класса решаемых задач и повышения точности, оно содержит инверторы, элементы И, ИЛИ н параллельно соединенные цепочки, включенные между выходом источника опорного сигнала и входом операционного усилителя постоянного тока, причем первая цепочка состоит из последовательно соединенних первого и второго дополнительных ключей, общий вывод которых через последовательно соединенные первый дополнительный масштабный резистор и первый дополнительный сглаживающий конденсатор соединен с шиной нулевого потенциала, а вторая цепочка состоит иэ последовательно соединенных дополнительных вто« рого масштабного резистора, второго сглаживающего конденсатора,. третьего масштабного резистора, обкладки ВТорого дополнительного сглаживающего конденсатора через дополнительный третий и четвертый ключи соединены с шиной нулевого потенциала, вхогы первого элемента ИЛИ соединены с вторым и третьим входом устройства, выход первого элемента ИЛИ соединен с управляющими входами третьего дополнительного ключа непосредственно и четвертого дополнительного ключа через первый инвертор, первые входы второго элемента И и второго элемента ИЛИ соединены с четвертым входом устройства, а вторые входы соединены с первым входом первого элемента ИЛИ, выход второго элемента И через второй инэертор н выход второго элемента ИЛИ соединены с входами третьего элемента И, выход которого соединен с управляющими входами зторого дополнительного ключа непосредственно и первого дополнительного ключа через третий инвертор, а управляющий вход второго ключа соединен с выходом второго элемента И.

Источники инФормации, принятые во внимание при экспертизе:

1. Угрюмов E.Ï. Импульсно-управляемая проводимость, как элемент схем автоматики и вычислительной техники.

Известия вузов СССР. Приборостроение, М., Р 4, 1971.

2. Авторское свидетельство СССР

9 260290, кл. G 06 G 7/161, 1968.

608171

Составитель Л.Снимщикова

Техред ц. Келемеш Корректор Н.Ковалева

Редактор Н.Разумович

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Заказ 2804/34 Тираж 826 Подписное

ЯНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5