Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советснин

Соцмалмстичасник

Рес убанн (ее) 608197

ИЗОВРЕТЕЙ Ия

И АВТОРСКОМУ СВИДВТВД СТВУ (63)Дополнительное к авт. сеид-ву (22) За Явлено 06.01. 76(2l)23 1 1269/18-24 (51) М, Кл.

6- 11 C 11/22 с присоединением заявки №

Гасударственный квмнтет

Сввете Мнннетрав СССР еа делам нзааретеннй н еткрмтнй (23) Приоритет (43) Опубликовано 2g.05.78,Бюллетень № 19 (53) УДК 681.327 (088.8) (45) Дата опубликоеаннн описания (9 М (3

Ш. К. Кадышев, Л. Л. Твердов, Q. К. Фаттахов, В. 4. Липченко, А. И. Бородин, К. Г. Самофалов, Я. В. Мартьппок и A. Е. Бушманов (72) Авторн изобретения (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО е 2

Изобретение относится к запоминающим ус- б. оков памяти, выполненных нз шнрокополостройствам и может быть использовано для ных сегнетоэлектрических пьезотрансформатордлительного хранения н неразрушающего счи- ных запоминающих элементов, дешифратор бло. тывания информаиии (с. редкой сменой инфор- ков памяти, входы которого подключены к мации в запоминающем устройстве). другим выходам регистра адреса, а выходы — к

Известны запоминающие устройства, выпол- управляющим входам соответствующих элеменненные на широкополосных сегнетоэлектричес- тов И, усилители считывания, входы которых ких пьезотрансформа,орных запоминающих подключены к выходам блоков памяти, а вы; элементах. ходы через ггоследовательно соединенные элеОдно. из известных устройств содео кит ре- менты И .и ИЛИ вЂ” к входам регистра гистр адреса, дешифратор, адресные ключи, д числа, блок управлейия и шину нулевого повходы которых объединены и подключены через тен и ла (2j

4 < общие ключи к источникам поляризации и счи- . В этом. устройстве обеспечивается аппара.тывания, матрицу из широкополосных пьезо- турой считывания неразрушающее считывание трансформаторов, адресные шины которой под- н нформации йутем прикладывания к адключейы к выходам адресных ключей экрани- ресной шине блока памяти импульса считыва1 !5

v рующйе шины через разрядные ключи — к шн- . ния. Импульс считывания, приложенныи к выбне нулевого потенциала и разрядные шины — к раиной адресной шине, вызывает импульсную входам усилителей считывания ((). Это устрой. деформацию запоминающих элементов выбранство имеет невысокое быстродействие. ного числа. При этом на разрядных шинах появляются разнонолярные .сигналы, полярэп. ность которых определяется записаннои йнфораи олее близким техническим решением

I u к изобретению является запоминающее устройацией ство, содержащее регистр. адреса, одни нз вы- . ходов которого подключены к входу дешифрато- Однако устройству свойственен малый инра адреса, адресные ключи, управляющие вхо- формационный объем запоминающего устройды которых соединены с дешифратором адре- ства (ЗУ), малое быстродействие при.считыса, а выходы- — с соответствующими входами 5 ванин, низкая помехозащищенность и большая

608!97 потребляемая мощность. Пропорциональное уменьшение выходного сигнала с увеличением

Кавичества запоминающих элементов, подключенных к одной разрядной шине, ограничивает информационный объем указанного ЗУ. В этом

ЗУ малое быстродействие обусловлено тем, что прн подключении запоминающих элементов выбранного числа к адресному ключу через адресные шины происходит заряд конденсаторов, образованных запомина ощими элементами. При этом н бходимо определенное вре- 1О мя для разряда этих конденсаторов после импульса считывания (время переходных процессов) н соответственно увеличивается нрн этом период следования импульсов считывания.

Известное ЗУ характеризуется также высокими уровнями сигналов помех, обусловленных тем, что экранирующие шины соединены с шиной нулевого потенциала через промежуточные цепи (в частности через транзисторый ключ) и. не приняты меры к.исключению влияния считывающего сигиала на выходной сигнал. 2о

Цель изобретения — увеличение быстродействия прн считываини и информационного объема .устройства, аовыщение помехозащищенностн устройства и уменьшение потребляемой мощности.

Достигается эте тем, что устройство содержит разделительные элементы и дополнительный ключ, один вход которого соединен через разделительные элементы с выходами адресных ключей,.другой вход подключен к .выходу блока управления, а выход дополнительного зо ключа соединен с шиной нулевого потенциала.

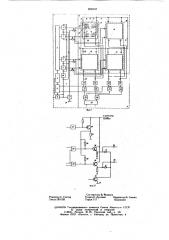

На фиг. 1 изображена структурная схема запоминающего устройства; на фиг. 2 — электеическая принципиальная схема ключа питапии н выходного каскада адресного ключа.

Запоминающее устройство содержит блок уаравлеиия l по адресу, накопитель 2, блок

3 усилителей считывания..

Влои l управления по адресу состоит из рагистра 4 адреса, дешифратора 5 адреса и дешифратора 6 блоков памяти. Выходы дешнфpampa 5 адреса соединены с управляющими входами адресных ключей 7. Выходы адресных .«лючей также объединены между собой разделительными элементами, например диодами

3, н соединены с одним входом донолнительного ключа,9. 45 .Уиравляющие входы адресных ключей 7 соединены с ключом 10 питания, через который нодилючаются цепи питания управляющих входов к источнику питания. В блок управления

1 по адресу входит также блок 11.управления.

Этот блок соединен с регистром адреса 4, адресными ключами 7, дешйфратором 6, управляющими входами ключей 9 и 10..

Накопитель 2 состоит из раздельных групп

12 съемных блоков памяти 13. Блок 13 выпол.нен иа-двухсторонней плате из стеклотекстолита СФ вЂ” 2, иа котором размещены широконолосиые сегнетоэлектрические пьезотрансформаториые запоминающие, элементы 14, входные электроды 15 которых объединены в адресные шины

l6, экраиирующне электроды 17 — в экранирующие шины 18, выходные электроды 19 — 60

Ф в разрядные шины 20. Адресные !б, экранирующие !8 н разрядные 20 шины блока l3 подключены соответственно к выходам адресных ключей 7, к шине 2! нулевого потенциала и к входам усилителей считывания 22. К шине нулевого потенциала 2! также присоединен выход дополнительного ключа 9. Соответствующие адресныг шины 16 одноименных блоков 13 различных групп !2 подключены к выходу одного адресного ключа 7, а соответствующие разрядные шины 20 блоков 13 одной группы 12 подключены к входу одного усилителя 22 считывания.

В запоминающих элементах 14 пьезокерамические пластины под входными электродами !

5 имеют жесткую поляризацию, а под выходными электродами 19 — различную поляризацию, которая определяется записанной информацией. Запись информации производится в каждый блок !3 отдельно на аппаратуре записи, выполненной в виде блока, в котором выходы адресных, экраннрующих и разрядных цепей соединены с контактами разъема для подключения блоков 13. Для записи информации необходимо снять блок !3 из устройства и подключить его к аппаратуре записи.

Блок 3 усилителей считывания состоит из усилителей 22 считывания, входы которых соединены с разрядными шинами 20 группы 12 блоков 13. Количество усилителей 22 считывания для группы 12 блоков 13 определяется разрядностью хранимого в накопителе числа.

Выходы усилителей 22 считывания через элементы И 23, одни из входов которых подключены к выходам дешифратора 6, и элементы

ИЛИ 24, на которых производится объединение одноименных разрядов считанной информации из различных групп 12 блоков 13, соединены с регистром числа Ж.

Ключ питания 10 выполнен на транзисторе 26 (см. фиг. 2). Коллектор транзистора подключен к источнику питания (не показан), база соединена через управляющий вход 27 с блоком l! управления. Эмиттер транзистора

26 через токозадающие резисторы 28 ссгдинен с управляющими входами 29 адресных ключей 7.;

Выходной каскад адресных ключей выполнен на транзисторах 30. Базы транзисторов соединены с управляющими входами 29, входы которых подключены соответственно к дешифратору 5 адреса и блоку ll управления..

Коллекторы транзисторов соединены с источником питания, эмиттеры подключены к адрес.ным шинам 16. и через диоды 8 и транзистор

31 — к шине 21. Ключ 9 выполнен на транзисторе 31, бааз которого соединена с блоком ll. Транзисторы 26, 30 и 31 в исходноЫ состоянии закрыты.

Конструктивно. адресные 16 и, ра®рядньЬ

20 шины в б.".оках .13 (см. фиг. !) расположе. иы взаимно перпендикулярно на противоположных сторонах платы, а в местах соединений с контактами разъема 32 разделены между собой экранирующимн шинами 18. Разъем. 32 используется для соединения блоков 13 с другими. блоками устройства.

608!97

О

25

Формула изобретения

Запоминающее устройство работает следу=ющим образом.

С приходом импульса обращения к ЗУ блок

ll управления вырабатывает определенную последовательность импульсов. По первому импульсу, совпадающему по времени с импульсом обращения, производится прием кода на регистр 4 адреса.. Код с регистра 4 адреса поступает на два дешифратора: младшая часть кода на дешифратор 5, старшая — на дешифратор 6.

Дешифратором 5 адреса производится выборка адресного ключа 7, соответствующего коду адреса.

Дешифратор 6 выбирается на элементах

И 23 группа 12 блоков 13, из которой производится считывание информации выбранного числа, соответствующего коду адреса.

В момент появления на выбранном адресном ключе 7 сигнала с дешифратора 5 на управляющий вход 27 ключа питания 9 поступает импульс запуска с блока 11.управления (длительностью 3 — 5 мксек). При этом транзистор 26 открывается и подключает источник питания на время действия импульса на управляющие входы 29 адресных ключей 7. Через

I — 1,5 мксек после прихода импульса запускана управляющие входы 29 адресных ключей 7 поступает импульс считывания с блока 1! управления. По этому импульсу срабатывает управляющий вход 29 выбранного адресного ключа 7, при этом открывается транзистор 30 н во время действия импульса считывания к адресной шине 16 через контакты разъема 32 прикладывается напряжение считывания. При этом длительность импульса считывания меньше длительности импульса запуска и во времени они расположены так, что импульс.считывания <вписывается» в импульс запуска, причем задние фронты импульсов могут совпадать, Это сделано для того, чтобы в момент появления импульса считывания на адресных шинах.

16 закончились переходные процессы от действия переднего фронта импульса запуска ключа

9 (питания) и установилось номинальное значение напряжения питания на управляющих входах 27.

По окончании импульса считывания (по его заднему фронту) блок 1! управления вырабатывает сигнал; открывающий транзистор 31.

При этом адресные шины 16 накопителя через диоды 8 и открытый транзистор 31 подключаются к шине 21 и тем самым происходит быст- рый разряд суммарной входной емкости запоминающих элементов 14. Длительность указанного сигнала, открывающего транзистор 3!. должна быть больше времени разряда суммарной емкости, Импульс напряжения, приложенный к адресной шине 16, вызывает импульсную деформацию пластин под входными электродами 15 запоминающих элементов 14 выбранного адоеса в каждой группе 12 блоков !3 и одновре-, ме.rno с этим импульсную деформацию пластин под выходными электродами !9, причем направление этой деформации зависит от направления поляризации пластин под.выходными электродами f9, т. е от записанной информации. При этом на разрядных шинах 20 каждой группы 2 блоков !3 появляются разнополярные сигналы, полярность которых определяется записанной информацией. Эти сигналы через контакты разъема 32 поступают на входы усилителя считывания 22 каждой группы 12 и на выходах усилителей 22 появляются сигналы, полярность которых однозначно связана с записанной информацией.

Выходные сигналы с усилителей считывания 22 поступают на один из входов элемента

И 23; на второй вход которого поступают сигналы выборки с дешифратора 6. На указайных элементах И 23 производится окончательная выборка числа, т. е. определяется конкретная группа 12 блоков 13, соответствующая коду регистра адреса, из которой производится выборка числа.

Сигналы с элемента И 23 поступают на элементы ИЛИ 24, где происходит объединение одноименных разрядов выбранных чисел из различных групп 12 накопителя при различных значениях кода на регистре 4 адреса и потом — на регистре числа 25.

Описанное устройство допускает многократное считывание, при этом считывание является неразрушающнм даже при отключении источников питания, так как амплитуда напряжения считывания значительно меньше напряжения поляризации при записи.

Запоминающее устройство, содержащее регистр адреса, одни из выходов которого подключены к входу дешифратора адреса, адресные ключи, управляюи ие входы которых соединены с дешифратором адреса, а выходы — с соответствующими входами блоков памяти, выполненных из широкополосных сегнетоэлектрическнх пьезотрансформаторных запоминающих элементов, дешифратор блоков памяти, входы которого подключены к другим выходам регистра адреса, а выходы —.к управляющим входам соответствующих элементов И, усилители считывания, входы которых. подключены к, выхо45 дам блоков памяти, а выходы через последовательно соединенные элементы И и ИЛИ вЂ” к входам регистра числа, блок управления и шину нулевого потенциала, отличающееся тем, чго, с. целью увеличения быстродействия устройства, оно содержит разделительные элеменЯ) ты и дополнительный ключ, один вход котордю соединен через разделительные элементы с выходами адресных ключей, другой вход. подключен к выходу блока управленйя, а выход дополнительного ключа соединен с шиной ну55

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 368645, М. кл. G i! С 1122, 1971.

2; Авторское свидетельство СССР № 385314 ьо М. кл. G 11 С 1! 00, 1971, 608I97. Составитель В. З удаков

Техред О, .!!уговая Корректор И. Гоксич

Тираж 7!7 . Подписное

Редактор E. Гончар

Заказ 2807 35

QHHHilH Говударствениого комитета Совета Министр и СССР по делам изобретений н открьггий! 13035, Москва, Ж-ЗЬ, Раушская иаб. д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4