Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

l;

1 (») еоелоа

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ к аетОаСкам СВИДатЕЛЬСтвю (61) Дополнительное к авт, свнд-ву— (22) Заяa>e 0 22.12.75 (21)2301908/24 с присоединением заявки №

{23) а ериоритет (43} Опубликовано 25.05.78,6вллатень %19 (45) Дата опубликования описания !9. 05 ° fS

Союз Советских

Социалистических

Республик (53) М. KJt.

С 11 С 2Î 00

Государственный комитет

Совета й!иннстров СССР по делам нзооретеннй н открытий (53) УДК 681.327 (088.8) (Т2) Авторы изобретения

В. Г. Слипченко, B. И. Корнейчук, A. И. Небукнн и Май Гупрун

Киевский ордена Ленина политехнический институт им, 50-летия Великой Октябрьской социалистической революции (73) Заявитель (54) ЗАПОМИНА!0ЩЕЕ УСТРОЙСТВО

С САМОКОНТРОЛЕМ

Изобретение касается запоминающих устройств. Известны запоминающие устройства с самоконтролем (!) и (2).

Одно из известных устройств содержит накопители, регистры слова и адреса, блоки кодирования и декодирования !!1.

Недостатком этого устройства является невысокая эффективная емкость.

Из известных устройств наиболее близким техническим решением к предложенному является запоминающее устройство с самоконтролем, !р содержащее основные и резервные накопители, подключенные к соответствующим регист-. рам слова и регистру адреса, блок декодирования, вход которого через элементы ИЛИ соединен с выходами основных регистров слова, . входы которых подключены к выходу блока кодирования; регистры мощности корректирующего кода, выходы которых через соответству. ющие элементы И подключены ко входам блока сравнения и блоков кодирования и декодирования, подключенных к выходному. регистру слова ф2!.

Недостатком этого. устройства является то, что в случае возникновения отказов в одноименных ячейках основных и резервных накопителей выдача информации невозможна, что существенно снижает надежность устройства. Ж

Цель изобретен:;л — польнленне надежности устройства.

Для этого в устройстве введены коммутаторы, блоки управления длиной кода и дополнительные элементы И н ИЛИ, выход резервного регистра слова через одни дололннтельные элементы И и ИЛИ подкл|очен к одному нз входов первого коммутатора, соединенного с блоком декодирования, вход резервного регистра слова через другие дополнительные элементы И и ИЛИ соединен с выходом второго коммутатора, подключенного к блоку кодирования, выходы регистров мощности и корректирующего -кода через соответствующие дополнительные элементы И подключены ко входам блоков управления длиной кода, выходы которых через соответствующие дополнительные элементы ИЛИ соединены со входами коммутаторов.

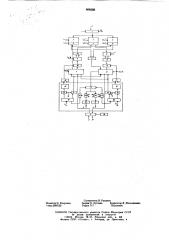

На чертеже приведена структурная схема устройства; содержащего, например два основных и один резервный накопители.

Устройство цэдержнт регистр адреса 1 с информационным входом 2. Выход регистра соединен с основными накопителями 3 и 4, в которых хранятся информационные разряды, и с резервным накопителем 5, в котором хранятся контрольные разряды слов накопителя 3 н кон608202 трольные разряды слов накопителя 4. Выход накопителя 3 соединен со входом регистра слова б. Другой вход регистра слова б связан с блоком кодирования 7. Выход накопителя 4 соединен со входом регистра слова 8. Другой вход регистра слова 8 подключен к блоку кодирования 7. Выходы регистров б и 8 подключсны через элементы ИЛИ 9 к блоку декодирования 10.

Выход резервного накопителя 5 соедине(со входом регистра слова 11. Выход регистра 11 подключен к одному входу элементов И 12.

Выходы элементов И 12 подключены через элементы ИЛИ ll3 ко входу коммутатора 14.

Выход коммутатора 14 связан с блоком 10.

Один выход блока 10. соединен со входом выходного регистра слова 15, имеющего информационный выход 16 и вход 17, а выход регистра

l5 соединен с блоком 7. Выход блока 7 соединен с одним входом коммутатора 18. Выход коммутатора 18 соединен со входом элементов

И 19, выходы которых через элементы ИЛИ 20 подключены ко входу регистра 11 ;

Второй выход блока !О подключен к одному входу блока сравнения 21. Другой вход блока 21 через. элементы И 22 подсоединен к регистру, мощности корректирующего кода 23.

Один вь(хад регистра 23 через элементы И 24 связан с блоками 7 и 10, а другой выход е".о через элементы И 25 соединен с блоком управления длиной кода 26, который выполнен, например в виде шифратора. Выход блока 26 чер э элементь(ИЛИ 27 и 28 связан с коммутаторами 18 и 14. Третий вход блока 21 через элементы И 29 соединен с регистром мощности корректирующего кода 30. Один выход регистра 30 через элементы И 31 соединен с блоками 7 и 10, а другой выход регистра 30 через элементы И 32 соединен с блоком управления длиной кода 33. Выход блока 33 через элементы ИЛИ 27 и 28 соединен с коммутаторами

1 4 и 18. Выход блока 21 соединен через элементы И 34 со счетчиком 35 и через элементы

И 36 — .со счетчиком 37. Блок управления

38 связан с регистром 1, с накопителями 3, 4 и 5, с регистрами 6, 8, 21 и 15, с блоками 7 и 10; с регистрами 23 и 30, с элементами И !2, 19,. 22, 24, 25, 29, 31, 32, 34 и

36 и со счетчиками 35 и 37.

Предложенное устройство работает следующим образом.

Регистры 23 и 30, управляющие блоками 7 и 10, настраиваются путем записи в них соответствующих слов на код, мощность которого определяется максимальной кратностью находящихся в ячейках накопителей соответственно 3 и 4 отказов (под мощностью К корректирующего кода подразумевается. его способность исправлять ошибки кратности от до К включительно). Настройка регистров

23 и 30 происходит следующим образом.

В начале работы устройства, когда отказы в ячейках накопителей 3 и 4 отсутствуют, регистры 23 и 30 настраиваются на код, мощность которого равна, например 1 (код Хэмминга). По мере, накопления в ячейках на5 (о (5

30 колей 3 и 4 во ик.(ои!Их в разнь(е мо менты времени, например однократных отказов, кратность отказов, имеющихся в иеиотором количестве этих ячеек, будет постепенно увеличиваться от I до K. При этом соответствующие регистры 23 и 30 перестраиваются на коды с мощностью, равной соответственно 2, 3, ..., К+ 1.

В исходном состоянии счетчики 35 н 37 установлены в»0». На регистр 1 ио входу

2 поступает адрес ячейки накопителя 3 или

4, к которой необходимо обратиться.

При считывании в случае нахождения ячейки. в накопителе 3 слово из накопителя 3 поступает на регистр 6, а и случае нахождения ячейки в накопителе 4 слово из накопителя 4 поступает в регистр 8. При этом слово из одноименной ячейки накопителя 5 считывается в регистр l l. Далее. слово из регистра 6 или из регистра 8 через элементы ИЛИ 9 подается в блок 10.

Контрольные разряды ири этом поступают из регистра 1! в элементы И !2. Еслч слово считывается иэ накопителя 3, то контрольные разряды без «разворота» проходят через элементы И 12, а если слово считывается иэ накопителя 4, то контрольные разряды «разворачиваются», т. е, п-ый разряд занимает место l го разряда, и — 1-ый разряд занимает место 2-го разряда и т. д. Слова из элементов

И 12 поступают через ИЛИ 13 в коммутатор

14. При считывании слова из накопителя 3 по содержимому регистра 23 блок 26 определяет количество необходимых контрольных раэрядов. По соответствующим сигналам из бло ка 26, которые через элементы ИЛИ 27 поступают в коммутатор 14, коммутатор разре- . шает выдачу только контрольных разрядов слова, записанного в накопителе 3. Если слово считывается из накопителя 4, то все происходит аналогично, но тогда работают вместо регистра 23 регистр 30, а вместо блока 26— блок 33.

В блоке 10 слово проверяется на наличие ошибки, и если ее нет, то информация выдается из блока 10 в регистр 15.

Если ошибка обнаруживается, то в блоке

45 !

О с помощью корректирующего кода она исправляется и декодированное исправленное слово выдается на регистр 15. При эз ом иэ блока

l0 выдается сигнал на блок 21, где сранивается кратность ошибки, обнаруженной блоком !О .и мощность корректирующего кода, задаваею мая регистром 23 или 30. При их равенстве блок 21 выдает сигнал через элементы И 34 в счетчик-35 в случае считывания слова из накопителя 3 или через элементы И 36 — в счетчик 37 в случае считывания слова из накопителя 4.. При этом содержимое .счетчика увеличивается на 1. Если сод..ржимое счетчика достигает заранее ус.(ановленного числа, из счетчика подается сигнал в блок 38 на перезапись информации в соответствующем накопителе с использованием кода, исправляю6о щего двойные ошибки.

6п8202

Перезапись информации в накопителе 3 или

4 с использованием более мощного кода осуществляется в<.який раэ, когда содержимое соответствукзгцего счетчика достигает заранее занн" вли I да ои е чины. При перезаписи слова с и тываются на регистр 15, кодируются более мощным кодом и записываются в те же ячейки соответствующего накопителя, откуда оии были счнтаны.

Информационные разряды из блока 7 непосредственно записываются в накопитель 3 10 илн 4 по адресам, последовательно указываемь. м регистром 1. Контрольные разряды поступают в коммутатор 18. Количество выдаваемых контрольных разрядов из коммутатора !

8 в элементы И 19 определяется блоком 26 или 33 в соотвегствии с новым содержимым регистров 23 или 30, задающих более мощный код. Контрольные разряды из элементов

19 поступают в элементы ИЛИ 20 и далее в накопитель 5 без «разворота», если перезапись идет в накопителе 3 и .с «разворотом», если перезапись осуществляется в накопителе 4.

Пусть в накопителе 3 в одной из ячеек было записано 16-ти разрядное слово 101

001, а в накопителе 4 в одноименной ячейке было записано 16-ти разрядное слово 001

011. Для исправления одиночной ошибки 16-ти разрядного слова требуется 4 контрольных разряда. Пусть Z — контрольные разряды накопителя 3, а У вЂ” контрольные разряды накотителя 4. Буквой 7 обозначены ец!е неиспользованные разряды. Тогда в накопителе 5 saписано слово

Z1Z2Z3Z4XI "- 4У4УЗУУ! °

При считывании слова информационные разряды поступают из -регистра 6 или 8 через элементы ИЛИ 9 в блок 10. Контрольные: разряды при этом из регистра l l поступают в элементы И 12. Если слово находится на регистре 6, то контрольные разряды без «разворота» из элементов И 12 поступают через элементы ИЛИ 13 в коммутатор 14. Так как 4 в регистр 23 записана «1», то блок 26 выдает в коммутатор 14 сигнал на пропускание. через него первых 4 разрядов, т. е, в блок 10 поступают контрольные разряды Zi

ZzZqZ<. Если слово находится на регистре 8, то контрольные разряды иэ регистра 11 в 4» элементах И 12 «разворачиваются», т. е. в коммутатор 14 поступает слово У|Уik У Х ...

X>ZZzZ>. По сигналу из регистра 30 блок

33 через элементы ИЛИ 27 дает сигнал для пропускания первых четырех разрядов из коммутатора 14 в блок 10 Таким образом, в блок

lO из коммутатора 14 поступают контрольные разряды У1У У,У . Из блока 10 на регистр

15 выдается декодированное слово.

Если блок 0 обнаруживает ошибку, то выдается сигнал «1» из блока 10. При этом блок

21 выдает сигнал в счетчик 35 или в счетчик 37, по которому в одном из них накапливается единица. Если содержимое счетчика достигает заранее заданной величины, то производится перезапись информации в соответствующем накопителе кодом, исправляющим двойную ошибI

Содержимое соответствующих регистров 23 или 30 увеличивается на единицу. Так как для исправления двойной ошибки необходимо

8 контрольных разрядов, то по соответствующим сигналам из регистра 23 или 30 блоки 26 или 33 разрешают выдачу иэ коммутатора !В, куда поступили контрольные разряды слова, находившегося а блоке 7, первых 8 разрядов.

Г!ри перезаписи в накопителе 3 через коммутатор 18 в элементы И 19 поступают слова Z,Z> . ..Zq, которые через элементы ИЛИ 20 поступают в накопитель 5. В накопителе 5 после перезаписи записано слово Z Z ...ZsX X X X V4

УэУ У1, Если перезапись осуществляется в накопителе 4, то иэ коммутатора 18 в элементы

И 9 выдаются слова У,Ó ...,У . После <разворота» в элементах И 19 выдаются через элементы ИЛИ 20 в накопитель 5 слова У8У,...У,.

В накопителе 5 после перезаписи будет записано слово Z ....Е,Х Х ХзХ4У ...У1.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее основные и резервные накопители, подключенные к со!ответствующим регистрам слова и регистру адреса, блок декодирования, вход которого через элементы ИЛИ соединен с выходами основных регистров слова; входы которь.х подключены к выходу блока кодирования, регистры мощности корректирующего кода, выходы которых через соответствующие элементы И подключены ко входам блока сравнения и блоков кодирования и декодирования, подключенных к выходному регистру слова, отличающееся тем, что, с целью повышения надежности устройства, оно содержит коммутаторы, блоки управления длиной кода и дополнительные элементы И и ИЛИ, выход резервного регистра слова через одни донолнительные "-чементы И и ИЛИ подключен к одному из входов первого коммутатора, соединенного с блоком декодирования, вход резервного регистра слова через д1!угие дополнительи ые элементы И и ИЛИ соединен с выходом второго коммутатора, подключенного к блоку кодирования, выходы регистров мощности и корректирующею кода через соответствующие, дополнительные элементы И подключены ко входам блоков управления длиной кода, выходы которых через соответствующие дополнительные элементы ИЛИ соединены со входами коммутаторов.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 385319, кл. G 11 С 29/00, 197!.

2, Авторское свидетельство СССР № 2! 7458, кл. G 11 С 29/00, 1968. ю

Составитель В. Рудаков

Техред 0..11уговая Корректор Д. Мельниченко

Тираж 717 Подписяое

Редактор Н. Разумова

3нкаэ 2807f35

UHHHllH Государственного комитета Сонета Министров СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Филиал ППП rÏeòåíò», г. Ужгород, ул. Проектная, 4