Устройство для определения разности частотных сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Донолнительнле н авт. свнд-ву (22) Зайвлеио190875 (2l) 2166191/18-24 с присоединением заявки,% (23) Прйоритет— (43) ОЩбдиковано 050678. Втоддетень. % 21

Союз Созетскнк

Социалистических

Республик (щ 61О127

О

Ф»! (ji (555 м: к»

& 06 G. 7/14

Государствеиио1й комитет

Совета Иииистроа СССР по делам изобретений и отиритий (53) УДК 681. 335 (088.8) (45) дата опублиттованнй описаний 11,05,78

Ю.Б.Соколовский (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ РАЗНОСТИ

ЧАСТОТНЫХ СИГНАЛОВ

Изобретение относится к области вычислительной техники и может быть использовано в цифровых системах управления электроприводами, в частностй в регуляторах скорости и соотношения 5 скоростей.

Известны устройства для получения разностной частоты следования импульсов двух импульсных последовательностей, содержащие, например, синхрониза- 10 тор, схеМы антисовпадений, расширитель импульсов и блок задержки (1) или два вхОдных триггера, триггер восстановления, выходной триггер и блок логики из нескольких элементов И-НЕ И (2j. 16

Недостатком известных устройств является их относительная сложность.

Наиболее близким техническим ре:1ением к изобретению является устройство для определения разности частотных Ж сигналов, содержащее триггер, установочные входы которого являются входами устройства, а выходы подключены к управляющим входам первого коммутатора, и интегратор со сбросом, управляющий вход ключа сброса которого подсоединен через блок задержки к выходу формирователя сигналов (3).

Недостатком этого устройства является узкий частотный диапазон.

Целью изобретения является расширение частотного диапазона работы устройства.

Поставленная цель достигается тем, что предложенное устройство содержит счетный триггер, второй коммутатор, последовательно соединенные преобразователь частоты в.напряжение и квадратор, фиксатор нулевого порядка, ключ, элемент И и последовательно соединенные выпрямитель, пороговый элемент и элемент НЕ, выход которого соединен с первым входом элемента И, подключенного вторым входом и выходом соответственно к выходу формирователя сигналов и к управляющему входу ключа. Вход ключа соединен со входом выпрямителя и с выходом интегратора со сбросом, а его выход подключен ко входу фиксатора нулевого порядка, выход которого является выходом устройства. Входы преобразователя частоты в напряжение и счетного триггера соединены с одним из входов устройства, а их выходы подключены соответственно к свободным входам порогового элемента и к управляющим входам второго коммутатора, информационный вход которого подключен к выходу первого коммутатора, а выходко входу интегратора со сбросом.

610127

Вход формирователя сигналов подсоединен к выходу счетного триггера, вход квадратора — к информационному входу первого коммутатора.

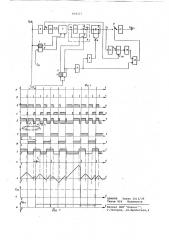

На фиг. 1 изображена принципиальная схема устройства; на фиг.2 — временные 5 диаграммы его работы.

Устройство содержит триггер 1, ус- тановочные входы которого являются .входами устройства, а выходы а, б подключены к управляющим входам первого коммутатора 2, интегратор со сбросом 3, управляющий вход ключа сброса 4 которого подсоединен через блок задержки

5 к выходу формирователя сигналов 6, счетный триггер 7, второй коммутатор )5

8, последовательно соединенные преоб раэователь частоты в напряжение 9 и квадратор 10, фиксатор нулевого порядка 11, ключ 12, элемент И 13 и последовательно соединенные выпрямитель 14, 20 пороговый элемент 15 и элемент HE 16.

Выход последнего соединен с первым входом элемента И 13, подключенного вторым входом и выходом соответственно к выходу формирователя сигналов б и к управляющему; входу ключа 12. Вход ключа соединен со входом выпрямителя

14 и с выходом интегратора 3, а выходсо входом фиксатора нулевого порядка

11, выход которого является выходом устройства. Входы преобразователя частоты в напряжение 9 и счетного триггера 7 соединены с одним из входов устройства,а выходы подключены соответственно к свободным входам порогового элемента 15 и к управляющим входам второго коммутатора 8,информационный вход которого подключен к выходу первого коммутатора 2,а выход-ко входу интегратора со сбросом З.Вход формирователя сигналов б подсоединен к выходу триггера .7,а выход квадратора 10-к информационному входу коммутатора 2.

Коммутатор 8 состоит, например, из двух цепей, работающих поочередно.

Причем, если первая цепь-инвертор 17 45 и ключ перемены знака 18, то вторая, ключ перемены знака 19.

Устройство работает следующим образом.

На преобразователь 9„ один из вхо- 50 дов триггера 1 и триггер 7 подается задающая частотная импульсная последовательность (ЧИП) fзц8 (фиг.2a) °

На другой вход триггера 1 подается

ЧИП обратной связи (фиг.2б).При 55 этом на выходах а и 8 триггера 1 получаем сигналы (фиг.2,в,г), которые поступают к управляющим входам коммутатора 2 (аналогично коммутатору 8) .

Выходной сигнал преобразователя 9

V9- Ê, „, (1) поступает на квадратор 10, С выхода которого снимается сигнал ю ю 1) ьаЭ 65

Пройдя через коммутатор 2, сигнал с квадратора 10 имеет вид, показанный на фиг.2, д (с амплитудой Uo ) .

Одновременно на выходах а и К триггера 7 формируются последовательности прямоугольных импульсов со скважностью 2 (фиг.2, е,ж) . 3TH импульсы дают команды на поочередное замыкание ключей 18, 19 коммутатора 8.

Сигнал У проходя, через коммутатор

8, преобразуется в сигнал Us (фиг.2,з) и поступает на вход интегратора 3.

Прямоугольные импульсы с выхода :S триггера 7 (фиг.2, ж) поступают через формирователь б (укорачивающий их до малой длительности 7,4,- —, напри-.

Кз ьь мер, на фиг.2,а по переднему фронту) к первому входу элемента И 13 и через блок задержки 5 на время 7 (фиг.2,и) к цепи управления ключа сброса 4 интегратора 3, обеспечивая его периодическое кратковременное замыкание от каждого, например, нечетного импульса из задающей ЧИП f 8, задержанного на время C< .

В результате на выходе интегратора

3 в процессе работы устройства получаем сигналУ(фиг.2к), В .случаях, когда напряжение Ц по модулю не превышает

Еоп на выходе элемента И 13 формируется импульс длительностью 7р, обеспечивающий кратковременное замыкание ключа 12. При этом проводятся замер (фиг.2 л) н фиксация конечного значе- ния интеграла У„ в Фиксаторе 11 (фиг.

2, м).

Однако з зоне фазового сдвига между входными :-»: ЧИП (2) возможен кратковременный всплеск производной -, ., получаемой в виде конечного значения интеграла U (наък пример, на фиг.2, к) .

Сигнал Ео„ пропорционален текущему значению частоты j;-„д. При этом конечное значение интеграла интегратора U> пропорционально разностной частоте входных ЧИП af = ц8-f поэтому выбоРом коэффициента Кап (Е „= к „1 g) определяем предельную величйну ошибки ь устройства независимо от текущего значения f<

В этом случае в момент прихода импульса с формирователя 6 сигнал с выхода выпрямителя 14 U, > Е,и,, пороговый элемент 15 срабатйвает, на его выхоце появляется .игнал " 1 ., a на выходе элемента НЕ 16 .- сигнал 0, который поступает на второй вход элемента И 13. В этом случае на выходе элемента И 13 не формируется импульс, ключ 12 не замыкается, а на фиксаторе

11 остается ранее зафиксированный сигнал (пунктирная линия на фиг.2, м).

Необходимо отметить, что Т с< -1—

f saj. и 4 -.* -,причем время выбрано из

610127 условия надежной передачи конечного значения интеграла Uù и его фиксации в фиксаторе 11. Блок .задержки 5 обес.печивает запаздывание переднего фронта управляющего импульса ключа 4 относительно заднего фронта импульса с формирователя 6 на время t необхоФ, димое для замыкания ключа 12.

Ниже приведены математические соотношения зависимости выходного сигнала устройства — преобразователя двух 10 частотных сигналов.

Из фиг.2в — ЬЧ1.- начальный, сдвиг, по фазе между входными ЧИП

6Т 2К

2 Г

Тьад. l5 где 6 T g — тот же сдвиг между ЧИП во времени.

Известно, что и Т в- {Т о.р -Тoc) >f Тsa8 Т оо (4) где а1 =1 8 -7" = f — раэностная 20 частота; тр= „= -„ =

Г т -тос, — период раэностной частоты.

Определим конечное значение интеграла Ugg, на интервале интегрирования Q5

Т„ 2Т 8 (фиг.2,а,к) с учетом формулы (2) Вод-Р1 Pas4» Го фт аД ак Т(f "+ 3 (.1 (4)ф2аТ„(5) за-ат1 i s8-аТ Ъ (при аТт 2аТ ), где T> — постоянная интегрирования интегратора 3; . кю "Э f> g — сигнал с выхода квадра2, 2, тора 35

С учетом формул (4) и (5) на выходе устройства получаем сигнал

ia е ьаЭ, . вам, <1

Т Ь 1МЗАс "ь ос 40

Область применения рассматриваемого устройства - малое рассогласование частот входных сигналов, т.е. отношение частот входных сигналов

45 ъаЗ м1 (Т) ос

В связи с формулой (7) с достаточно высокой степенью приближения выходной сигнал устройства 50 Вьюк + " 4f г И) при о

<» 2коке

Ф(55 а

Таким образом, выходной сигнал уст" ройства преобразования двух частбтных сигналов в аналоговый сигнал пропорционален по формуле (8) разности частот.

Предложенное устройство работает с достаточно высоким быстродействием.

Его запаздывание равное не более, чем двум периодам задающей частоты в то время как в известном устройстве постоянная узла усреднения на порядок больше.

Диапазон рабочих частот устройства принципиально не ограничен (при идеальных элементах), в то время как в известном устройстве он ограничен пос.— тоянными времени инерционных звеньев, Этому способствует также то, что Е оо пропорционально f

Формула изобретения

Устройство для определения разности частотных сигналов, содержащее триггер, установочные входы которого являются входами устройства, а выходы подключены к управляющим входам первого коммутатора, и интегратор со сбросом, управляющий вход ключа сброса которого подсоединен через блок задержки к выходу формирователя сигналов, о т л ич а ю щ е е с я тем, что, с целью расширения частотного диапазона, оно содержит счетный триггер, второй коммутатор, последовательно соединенные преобразователь частоты в напряжение и квадратор, фиксатор нулевого порядка, ключ, элемент И и последовательно соединенные выпрямитель, пороговый элемент и элемент НЕ, выход которого соединен с первым входом элемента И, подключенного вторым входом и выходом соответственно к выходу формирователя сигналов и к управляющему входу ключа) вход ключа соединен со входом выпрямителя и с выходом интегратора со сбросом, а его выход подключен ко входу фиксатора нулевого порядка, выход которого является выходом устройства; входы преобразователя частоты в напряжение и счетного триггера соединены с одним иэ входов устройства, а их выходы подключены соответственно к свободным входам порогового элемента и к управляющим входам второго коммутатора, информационный вход которого подключен к выходу первого коммутатора, а выход - ко входу интегратора со сбросом; вход формирователя сигналов подсоединен к выходу счетного триггера, выход квадратора подключен к информационному входу первого коммутатора.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

9 213977,кл.(3 06 & 7/14, 1968.

2. Авторское свидетельство СССР

9 337777779999, кл . G 06 G 7/14,,1970 .

3. Патент Франции 9 1388840, кл. & 05 Р, 1970.