Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Сотов Сееетеюа

OllNCAHHE

ИЗОБРЕТЕН ИЯ

k AIfOP ÑÌOÌÓ СЮИДВТИПЬСТВУ (>>) 610175

«.;; . J

j (6!)Яоаолнительиое к авт. сеид-ву (32) Заявлено 03.08.76(21) 2398328/18-24 (51) М. Кл.

& 11 С 15/00

-с присоединением заявки ¹

Гасраретвеаей кеыатет

Сваата Мвиктрев СССР

ЙФ 46мм изФбрВТВаиб и еткритий (23) Прнорытет (43) Опубликовано 05,0678.Бюллетень № 21 (53) УДК 681.327.6 (088. 8) (45) Дата опубликования опнсання 03.05.78 (79) Л вторы

ыаобретеныя. П. И. Рутенмахер, Ю, А. Тимошенко и С, Т. Тихончук к (71) За явнтель

Одесский ордена Трудового Красного Знамени политехнический институт (54) ACCGOHATHBHOE ЗАПОМИНАЮШЕЕ УСТНЗЙСТВО

Изобретение относится к вычислительной технике.

Известно ассоциативное запоминающее устройство (АЗУ), которое содержит накопитель, регистр опроса, детекторы (1j .

Недостатком этого устройства является сложная прошивка матрицы. накопителя.

Наиболее близким по технической сущности к изобретению является ассоциативное запоминающее устройство, содержащее ре- тЕ гистр опроса, выход которого подключен к одним входам логического блока, соединенного с детекторамя, блох оперативной памяти, подключенный к распределитеЛю импуль. сов, соединенному с блоком управления (2).14

Недостатком этого устройства является невысокое быстродействие, связанное с необходимостью производить регенерацию информации в блоке памяти после каждого цикла ее считывания, se

Целью изобретения является повышение быстродействия АЗУ, Для этого устройство содержит дополнительный блок оперативной памяти, дополнительный распределитель импульсов, цодключенный к блоку управления, и элемен-, ты ИЛИ, входы которых подключены соот; ветственно к информационным выходам блоков оперативной памяти, а выходы -:к другим входам логического блока, .информацяонные выходы кажного нэ блоков оперативной памяти и выходы каждого из распределителей импульсов соединены соответственно со входами другого блока оперативной памяти.

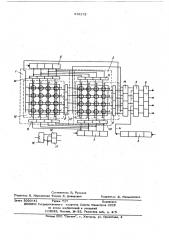

На чертеже изображена функциональная схема предложенного АЗУ.

АЗУ содержит блок 1 онератнвной памяти, дополнительный блок 2 оперативной памяти, регистр 3 опроса, выполненный в виде кольцевого сдвигакицего регистра, выход 4 которого подключен к одним иэ вхсоQoB o 0 o a S, соединенного с детекторами 6, распределитель 7 импульсов, дополнительный распределитель 8 ямпульсов. В состав каждого из блоков 1 и 2 входят формирователи импульсов записи

9 н 10, формирователи импульсов чтения

11, матрины 12 и 13, выполненные, например, из кольцевых магнитных сердечников, 3

610175

Устройство также содержит элементы

ИЛИ 14 и блок управления, часть которого .(триггер 15 н элементы И 16 и 17) показана на чертеже.

Входы распределителей 7 и 8 подклю- 5 чены соответственно к выходам элементов

И. 16 и 17, Входы элементов ИЛИ подключены соответственно к информационным выходам блоков 1 и 2, а выходы — K другим входам блока 5, о

Информационные выходы каждого из блоков 1 иля 2 и выходы каждого из распределителей импульсов 7 и 8 соединены соответственно со входами другого блока

2 или 1. 1S

Устройство работает следующим образом.

Пусть в исходном состоянии информация записана в матрице 12, а матрица 13 очищена (хранит нулевую информацию), триггер 5О

15 находится в состоянии 1", В регистр

3 записан поисковый образ. Во всех детекторах 6 записана "1 .

Работа устройства начинается с приходом тактовых импульсов на вход распределителя 7. Через формирователи 11 ийформация поразряцно считывается из матрицы 12. На этом же такте через формирователи 9 и 10 информа.М ция записывается в соответствующий разряд

; матрицы 13 по совпадению полутоков. Hapsnлельно с перезаписью информации из матрицы 12 и 13 через элементы ИЛИ 14 сигналы поступают на ахоп блока 5. .Блок 5 реализует логическую функцию сложение по моцулю 2" (исключающее ИЛИ) соответствующих разрядов матриц 12 и регистра 3. несовпадение кода поискового:: образца с содержимым соответствующего разряда матрицы 12 устанавливает детектор40

6 в состояние "0". Далее происходит перепись следующего разряда слов из матрицы

12 в матрицу 13. При этом содержимое регистра 3 опроса сдвигается влево, на 1 разряд, 45

Устройство работает таким образом в течение т?Ъ тактов, (где тт — число разрядов матриц), пока не будет проведено сравнение всех разрядов признака опроса с хранимой в матрице. 12 информацией, Пос-, 5Э ле тт тактов вся информация хранится в матрице 13, В матрице 12 записаны все нули, так как считывание производится полным током, 55

В конце цикла ассоциативной выборки сигнал 1" будет только в тех детекторах

6, где произошло полное совпадение кодов записанных слов с признаком опроса, При следующем обращении к АЗУ - so новому признаку опроса - информация переписывается из матрицы 13 в матрицу 12, и опновременно сигналы через элементы ИЛИ

14 поступают в блок 5 и т.д, Другим примером возможной реализации

АЗУ является выполнение всех его элементов на базе интегральной технологии, При этом вместо матрицы ферритовых сердечников используется матрица запоминающих элементов на МДП-транзисторах, выполненная в виде большой интегральной схемы.Запоминаюшим элементом такой матрицы является динамическая запоминающая ячейка с разрушением информации при считывании, Цикл регенерации при этом отсутствует, а хранимая информация циклически нерезаписывается между матрицами.

13 цепом АЗУ будет функционировать а налогично описанному выше на магнитных сердечниках с разрушаемым считыванием.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее регистр опроса, выход которого подключен к одним входам логического блока, соединенного с детекторами, блок оперативной памяти, подключенный к распределителю импульсов, соединенному с блоком управления, о т л и ч а ю ш е е с я тем, что, с целью увеличения быстродействия устройства, оно содержит дополнительный блок оперативкой памяти, дополнительный распределитель импульсов, подключенный к блоку управления, и элементы ИЛИ, входы которых .подключены соответственно к информационным выходам блоков оперативной памяти, . а выходы -. к другим входам логического блока, информационные выходы каждого из блоков оперативной памяти и выходы каждого из распределителей импуль сов соединены соответственно со входами другого блока оперативной памяти, Источники информации, принятые во внимание при экспертизе:

1, Авторское свидетельство СССР

¹ 290322, кл, & 11 С 15/00, 1969.

2, 3ЕЕЕ Тгi Sactiот э от Е есЬ.отАе

Co pute s,1965, т,14, М 4, рр. 600.-605, 610175

12

Составитель В. Рудаков

Редактор H. Марховская Техред Е. Давидович

Корректор Д. Мельниченко

Заказ 3020/41 Тираж 717 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам. изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4