Коммутатор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советсннк

Соцнаннстнчесннк

Респубпни (11) 6 10300

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 080476 (21) 2343398/21 (51) М. Кл, с присоединением заявки ¹

Н 03 К 17/00

Гввудврвтввнныу нввнтвт Ввввтв ввнннвтрвв ВОСР

II нвнвю нввврвтвннФ н втврытнй (23) Приоритет— (43) Опубликовано 05,06.78,Бюллетень № 21 (53) УДК 621.382 (088 8) (45) Дата опубликования описания 120578 (72) вторы изобретения

О.Э.Хесин и В.П.Чуркин (71) Заявитель (54) КОММУТАТОР

Изобретение относится к области связи и может найти применение в аппаратуре передачи данных и электронной коммутации.

Известны коммутаторы, содержащие дешифраторы адреса, регистры информации, триггер тактов, схему НЕ, блоки памяти, схему распределения приоритетов и адресные шины, причем регистры 10 информации и триггер тактов подключены к соответствующим входам схемы распределения приоритетов, выходы которой соединены с адресными шинами (1).

16

:едостатком коммутаторов являются узкие функциональные возможности, Известен также коммутатор, содержащий адресный дешифратор, блоки адресного переключения, блок объединения, при этом первые и вторые входы блоков адресного переключенйя подключены к выходам адресного дешифратора и к ши-. не стробирующнх импульсор соответственно, а выходы — ко входам блока 25 объединения, выход которого являетоя выходом коммг тора (2) .

Недостатком такого коммутатора является ограниченность функциональных возможностей., 30

Целью изобретения является расширение функциональных возможностей коммутатора.

Эта цель достигается тем, что в коммутатор, содержащий адресный дешифратор, блоки адресного переключения, блок объединения, при этом первые и вторые входы блоков адресного переключения подключены к выходам адресного дешифратора и к шине стробирующих .импульсов соответственно, а выходы — ко входам блока объединения.. выход которого является выходом коммутатора, введены устройства блокировки общего входа, блокировки информационных входов, два элемента " Запрет, при этом первые вхопы устройств блокировки информационных входов соединены с информационными входами коммутатора, вторые — с первым входом управления и входом первого элемента Запрет ., а выходы устройств блокировки информационных входов и первого элемента Запрет подключе ны к третьим входам блоков адресного переключения и второму входу устройства блокировки общего входа соответственно, причем первый вход устройст ва блокировки общего входа соединен с общим входом коммутатора, а выход

610300 устройства блокировки общего входа . подключен к четвертым входам блоков адресного переключения, выходы которых соединены с первыми входами устройства блокировки информационных вы- 5 ходов .и соответствующими входами блока объединения, при этом выходы устройств блокировки информационных выходов являются информационными выходами коммутатора, вторые .входы уст- )О ройств блокировки информационных выходов и вход второго элемента Запрет . объединены со вторым входом управления, кроме того, выход второго элемента Запрет соединен с со- 15 ответствующим входом блока объединения.

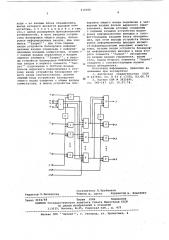

На чертеже приведена функциональная схема коммутатора.

Коммутатор содержит адресный дешифратор 1, устройства 2 блокировки информационных входов и общего входа, первый и второй элементы Запрет

3, общий вход 4, общий выход 5, блоки адресного переключения б, информационные входы 7, информационные выходы 8, устройства 9 блокировки информационных выходов, блок объединения 10, первый вход 11 управления, второй вход 12 управления, шину 13 стробирующих импульсов, входы 14 адресного дешифратора.

Коммутатор работает следующим образом.

С помощью сигналов управления Х и у, подаваемых на входы 11 и 12, устанавливаются четыре режима работы устройства; а) х = 1, у = Π— соответствует поочередному подключению информационных 40 входов 7 к общему выходу 5; б) х= О, у= 1 — соответствует поочередному подключению общего входа

4 к информационным выходам 8. в) х = 1, у= 1 — соответствует по- 45 очередному подключению информационных входов 7 к соответствующим информационным выходам 8; г) х= " О," у.="0"- соответствует подключению общего входа 4 к общему вы- 50 ходу 5.

Очередность подключения входов к выходам задается с помощью сигналов, поступающих на входы 14 дешифратора 1.

1IpH Х- 1, Ц- О блокируются IIblxo 5

8 и общий вход 4.

В этом режиме сигналы с входов. 7 поочередно поступают на общий выход

5. При этом дешифратор 1 в соответствии с адресом открывает блоки переключения 6, которые пропускают сигналы с устройств 2 на блок объединения 10.

Сигнал Х 1"через первый элемент 3 поступает на вход устройства 2, запрещая поступление сигналов на входы блоков б. Сигнал \I= О"поступает íà 65 вход устройства 9 и запрещает поступ-. ление сигналов на выходы 8.

Кроме того, сигнал Ц= О поступает через второй элемент 3 на вход блока

10 ч открывает его.

При х= 0, ц = 1 производится распределение сигналов, поступающих на общий вход 4 по информационным выходам

8. При этом сигнал к=" О"поступает на вход устройства 2 и через первый элемент 3 на устройство 2 блокировки общего входа 4. Устройство 2 блокировки информационных входов закрывается, а устройство 2 блокировки общего входа 4 открывается.

Сигнал у= 1 открывает устройства

9 блокировки информационных выходов и закрывает блок объединения 10.

Сигналы с общего входа 4 проходят через блоки адресного переключения б и поступают на ифнормационные выходы

8 в соответствии с адресом, подаваемым на дешифратор 1.

При x-- 1," Ij Г 1", устройство 2 блокировки общего входа 4 и блок объединения 10 закрываются, а, устройство

2 блокировки информационных входов и устройства 9 открываются., Сигналы с информационных входов 7 поступают через устройства 2, блоки адресного переключения б и устройства 9 на выходы 8 в соответствии с сигналами, поступающими на входы 14 дешифратора 1.

При х= О, ц=" О",устройства 2 блокировки информационных входов и устройства 9 закрываются, а устройство

2 блокировки общего входа и блок 10 открываются. Сигналы со входа 4 череФ устройство 2 блокировки общего входа один из блоков б, номер которого соответствует сигналам на входах 14 дешифратора 1, и блок 10 поступают на общий выход 5.

При прохождении информационных сиг« налов через устройство производится их инвертирование, а также стробирование тактовыми импульсами, поступаю-, щими с шины 13.

Коммутатор позволяет подключать общий информационный вход к общему информационному выходу, а также поочаредно к различным информационным выходам, а информационные входы — к соответствующим информационным выхо» дам устройства.

Формула из обретен и я

Коммутатор, содержащий адресный дешифратор, блоки адресного переключения, блок объединения, при этом первые. и вторые входы блоков адресного переключения подключены к выходам адресного дешифратора и к шине стробирующих импульсов соответственно, а вы610300

Составитель В.Трубников

Техред М. Петко Корректор A. Власенко

Редактор О.Филиппова

Заказ 3034/48 Тираж 1086 Подписное т ов СССР

ЦНИИПИ Государственного комитета Совета Министров по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул..Проектная, 4 ходы — ко входам блока объединения, выход которого является выходом коммутатора, отличающийся тем, что,с целью расширения функциональных возможностей, в него введены устройства блокировки общего входа, блокировки информационных входов, два элемента Запрет, при этом первые входы устройств блокировки информационных входов соединены с информа- . 10 ционными входами коммутатора, вторые ; с первым входом управления и входом первого элемента Запрет, а выходы устройств блокировки информационных входов и первого элемента Запрет подключены к тРетьим входам блоков адресного переключения и второму входу устройства блокировки общего входа соответственно, причем первый вход устройства блокировки

20 общего входа соединен с общим входом коммутатора, а выход устройства блокировки общего входа подключен к четвертым входам блоков адресного переключения, выходы которых соединены с.первыми входами устройства блокировки информационных выходов и соответствующими входами блока объединения, при этом выходы устройств блокировки информационных выходов являются информационными выходами коммутатора, вторые входы устройств блокироа= ки информационных выходов и вход вто» рого элемента Запрет объединены со вторым входом управления, кроме того, выход второго элемента Запрет соединен с соответствующим входом блока объединения.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

М 447836, кл. Н 03 К 17/00, 03.06.74.

2. Патент С11А 9 3832690, кл. 340-147 1,Р, 10.07.74.