Двоичный счетчик импульсов с контролем ошибок

Иллюстрации

Показать всеРеферат

б. ФИВ

ММ4ааатйоте х «ичвоатпзт

ОПИС.

Союз Советскик

Социалистических

Рвснубпик (и) 61030б

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) дополнительное к авт. свид-ву (22) Заявлено 2903.76 (21) 2338887/21 с присоединением заявки Ха (Я) N. Кл.

Н 03 К 21/34

Гаардаратааааык аеаатат

Вааата Маакатреа аааР аа даеаа азеаратакаа а аткрмткй (23) Приоритет— (43) Опубликовано 050678.Бюллетень ph 21 (Щ УДК621.374.45 (088.8) (45) Дата опубликования описания 160578

P2) вторы изобретения

В.И.Корнейчук, В.М.Кузнецов, В.A.Ïîíîìàðåíêî, Я.A.Ðàõëèí, В.П.Тарасенок и Я.И.Торошанко (71) Заявитель киевский ордена ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (54) ДВОИЧНЫИ СЧЕТЧИК ИМПУЛЬСОВ С КОНТРОЛЕМ ОШИБОК

Изобретение относится к импульсной технике.

Известен двоичный счетчик с контролем ошибок, содержащий N счетных разрядов, состоящих из триггерных 5 ячеек и логическйх элементов И, ИЛИ, несколько компараторов, осуществляющих сравнение сигналов счетных разрядов, блок селекции, каждый иэ которых соединяется с выходами компараторов, т0 и управляющее устройство (lj.

Данный счетчик обладает сложной схемой и не обеспечивает надлежащего быстродействия.

Наиболее близким по технической сущности к предлагаемому является двоичный счетчик, содержащий 21т входовых логических элемента ИЛИ и Я разрядов, каждый из которых содержит сновной и дополнительный триГгеры и QQ четыре двухвходовых логических элемента И, причем прямой и инверсный выхсды основного триггера разряда через первые два двухвходовых логических. элемента И, вторые входы которых со- 25 единены с прямым выходом основного триггера предыдущего разряда, подклю чены соответственно к нулевому и еди-" ничному входам дополнительного триггера, прямой и инвероный выходы которо- 30 го через два других двухвходовых логических элемента И, вторые входы ко-. торых соединены с инверсным выходом основного триггера предыдущего разря да, подключены соответственно к единичному и нулевому входам основного триггера данного разряда (21.

Недостатком данного счетчика является недостаточная точность и быс"родействие. т1елью изобретения является улучше ние точности контроля и повышение быстродействия.

Поставленная цель достигается тем, что в двоичный счетчик, состоящий из

2N входового логического элемента.

ИЛИ и К разрядов, каждый иэ которых содержит основной и дополнительный триггеры и четыре двухвходовых логических элемента И, причем прямой и инверсный выходы основного триггера разряда через первые два двухвходовых логических элемента И, вторые входы которых соединены с прямым выходом основного триггера предыдущего разряда. подключены соответственно к нулевому и единичному входам дополнительного триггера, прямой и инверсный выходы которого через два других двухвходовых логических элемента И, вторые вхо610306 ды которых соединены с инверсным выходом основного триггера предыдущего разряда, подключены соответственно к единичному и нулевому входам основного триггера данного разряда, в каждый разряд введены по два семивходовых элемеНта с порогами срабатывания, равными четырем и пяти, и весами входов, равными единице, и шесть инверторов, причем входы первого порогового элемента подключены к инверсному выходу. основного триггера предыдущего разряда, к нулевому и единичному входам дополнительного триггера, к прямым выходам дополнительного и основного триггеров, к нулевому входу основного триггера и через инвертор — .к единичному входу основного триггера, входы второго порогового элемента подключены к прямому выходу основного триггера предыдущего разряда, к еди- 20 ничному входу основного триггера и через инверторы — к нулевому и единичному входам дополнительного триггера, к прямым выходам основного и дополнительного триггеров и к нулевому вхо-25 ду основного триггера, а выходы всех семивходовых пороговых элементов соединены с соответствующими входами

2 N входового логического элемента

ИЛИ . 30

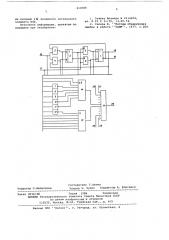

На чертеже приведена структурная электрическая схема счетчика.

Счетчик содержит N разрядов, каждый из которых состоит из основного

1 и дополнительного 2 триггеров, между которыми включены двухвходовые логические элементы И 3-6, инверторы

7 -12, семивходовые пороговые элементы 13 и 14, 2 К входовый элемент

ИЛИ 15.

На входы 16 и 17 поданы сигналы с предыдущего разряда.

Сигнал с выходов 18 и 19 подается на входы следующего разряда счетчика. Входы 20-23 элемента ИЛИ соединены с соответствующими выходами порого-45 вых элементов других разрядов счетчика на чертеже не показаны). Выходной сигнал снимается с выхода 24 °

Счетчик работает следующим образом.

При появлении ошибочного сигнала б0 на выходах или входах основного и дополнительного триггеров сумма входных сигналов одного из пороговых элементов превышает его порог. В результате на выходе этого порогового элемента появится сигнал ошибки.

Рассмотрим работу счетчика, находящегося в состоянии Х =О, 1 = 1, при входном сигнале .,» = 1, если неисправен элемент И б, йодключенный 60 к нулевому входу основного триггера

1. При правильной работе элемента И б на его выходе будет сигнал, соответствующий 0 . При появлении на выходе элемента И б сигнала, соответст 5 вующего 1, входные наборы кодов, подаваемых на входы пороговых элементов 13 и 14, соответственно будут иметь вид 1010011 и 0101100. Суммы входных кодов равны соответственно 4 и 3 . Следовательно на выходе элемента 13 с порогом срабатывания, равным 4, появится сигнал ошибки.

В счетчике обнаруживаются все ошибки, вызванные одиночными неисправностями. Кроме того, анализируя состояние выходов пороговых элементов каждого разряда, можно обнаружить неисправный разряд, т.е. локализовать ошибку.

Формула изобретения

Двоичный счетчик импульсов с контролем ошибок, состоящий из 2 N входового логического элемента ИЛИ и 34 разрядов, каждый из которых содержит основной и дополнительный триггеры и четыре двухвходовых логических элемента И, причем прямой и инверсный выходы основного триггера разряда через первые два двухвходовых логических элемента И, вторые входы которых соединены с прямым выходом основного триггера предыдущего разряда, подключенЫ соответственно к нулевому и единичному входам дополнительного триггера, прямой и инверсный выходы которого через два - других двухвходовых логических элемента И, вторые входы которых соединены с инверсным выходом основного тригге« ра предыдущего разряда, подключены соответственно к единичному и нулевому входам основного триггера данного разряда, отличающийся тем„ что, с целью улучшения точности контроля и повышения быстродействия, в каждый разряд счетчика введены по два семивходовых пороговых элемента с порогами срабатывания, равными четырем и пяти, и весами входов, равными единице, и шесть инверторов, причем входы первого порогового элемента подключены к инверсному выходу основного триггера предыдущего разряда, к нулевому и единичному входам дополнительного триггера, к прямым выходам дополнительного и основного триггеров, к нулевому входу основного триггера, и через инвертор — к единичному входу основного триггера, входы второго порогового элемента подключены к прямому выходу основного триггера предыдущего разряда, к единичному входу основного триггера и через инверторы к нулевому и единичному входам дополнительного триггера, к прямым выходам основного и дополнительного триггеров и к нулевому входу основного триггера. а выходы всех семивходовых пороговых элементов соединены с соответствующи.

610306

Составитель Т.Артюх

Техред Э. Чух<ик Корректор А. Власенко

Редактор О.Филиппова

Заказ 3034/48 Тираж 1086 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент ., r. ужгород. ул. Проектная, 4 ми входами 2 N входового логического элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе:

1. Заявка Франции 9 2214204, кл. Н 03 К 31/30, 13.09.74.

2. Селера Ф. Методы обнаружения ошибок в работе ЭЦВМ, 1972. с.200.