Двоичный счетчик импульсов с коррекцией

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВНДИТВЛЬСТВУ (11) 610308 (61) Дополнительное к авт. свид-ву (22) Заавлено05.04.76 (21) 2343787/21 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.06.78Зтоллетень ¹ 21 (45) Дата опубликования описания 2 .О.М. (Я) М. Кл.

Н 03 К 23/.02

Госуда рственнмй комитет

Совета Министров СССР во делам нэобретений н открытий (53) УДК 681.326 (088. 8) (72) Автор изобретения

С. В. Тимошок (71) 3aявитель (54) ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ С KOPPEKOHEH

Изобретение относится к импульсной технике.

Известен счетчик с исправлением ложных срабатываний, содержащий счетные ячейки, в котором с помощью схем совпадения на входе ячейки анализируют состояние всех предыдущих ячеек счетчика, задерживают сигнал с выхода триггера при его ложном срабатывании, происшедшем до установки всех предыдущих ячеек в единичные состояния и подают сигнал по цепи обратной связи на вход триггера для возвращения его в исходное состояние. Для предотвращения повторного срабатывания цепь обратной связи временно размыкают 11).

В данном счетчике не могут быть исправлены сбои, происходящие в такте, когда сигналы со схем совпадения запирают цепи обратной связи.

Наиболее близким по технической сущности к предлагаемому является счетчик, содержащий формирователь импульсов, два выхода которого соединены с входами двух регистров на Nтриггерах,,а третий выход — с одним иэ входов входного логического элемента И, второй вход которого связан с выходом логического элемента ИЛИ, причем установочные входы,триггеров, кроме первого, первого регистра

2 соединены с нулевыми выходами триггеров второго регистра, установочный вход первого триггера второго регистра соединен с прямым выходом первого триггера первого регистра, и логические элементы И (2, 5

Недостатком данного счетчика является отсутствие коррекции кода, искаженного в результате сбоя.

Целью изобретения является введение коррекции кода, искаженного в результате сбоеа.

Поставленная цель достигается тем, что в двоичный счетчик, содержащий формирователь импульсов, два выхода которого соединены с входами двух регистров на N триггерах, а гретий выход — с одним из входов входного ло гического элемента И, второй вход которого связан с выходом логического элемента ИЛИ, причем установочные входы триггеров, кроме первого, первого регистра соединены с нулевыми выходами триггеров второго регистра, установочный вход первого триггера второго-регист О ра соединен с прямым выходом первого триггера первого регистра и логические элементы И, введены N — 1 блоков коммутации и N полусумматоров, причем блоки коммутации включены между выходами логических элементов И и соответствующими выходами триггеров, кро6!0308

4 ме первого, первого регистра и входами соответствующих триггеров второго регистра, входы полусумматоров соединены с выходами соответствующих триггеров первого и второго регистров, а выходы полусумматоров соединены со входами упомянутого логического элемента ИЛИ.

Причем блок коммутации содержит два логических элемента И, логический элемент ИЛИ и инвертор.

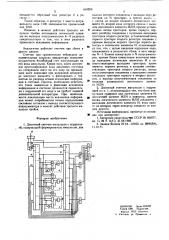

На чертеже приведена схема счетчика.

Счетчик содержит первый регистр 1, выполненный на триггерах, второй регистр 2, аналогичный первому, формирователь 3 импульсов, логический элемент И 4, логический элемент

ИЛИ 5, полусумматоры 6 — 9, блоки коммутации 10 — 12, в состав каждого из которых входят инвертор 13, логические элементы И 14 и

15, логический элемент ИЛИ 16. В состав счетчика также входят логические элементы

И 17и18.

Установочные входы 19 — 22 регистра 1 сое10

20 динены с соответствующими выходами регистра 2, а установочные входы 23 — 26 регистра 2 соединены с выходом регистра 1 и выходами блоков коммутации 10 — 12. На входы 27 и 28 регистров подаются сигналы синхронизации, а на вход 29 регистра подан сигнал с соот- 2S ветствующего выхода формирователя 3.

Входные импульсы подаются на вход 30 счетчика, а выходные сигналы снимаются с выходов 31 — 34.

Счетчик работает следующим образом.

Рассмотрим произвольный цикл работы двоичного счетчика при отсутствии сбоев.

В результате работы после прибавления оче-. редной единицы к содержимому регистра 1 на триггерах образуется очередной код, например 1010. Тогда на установочном входе 23 регистра 2 .присутствует потенциал логического нуля с прямого выхода первого разряда регистра 1. Этот же потенциал логического нуля присутствует на первом входе элемента И 17 и на первом входе блока 10.

Наличие потенциала логического нуля на 46 входе элемента 17 обусловливает наличие потенциала логического нуля на выходах элемента И 18, а следовательно, и на первых входах соответствующих блоков 11 н 12, Потенциал на выходе соответствующего бло. 4> ка 10 — 12 соответствует потенциалу на ее втором входе, если на его первом входе присутствует потенциал логической единицы, и потенциалу на его третьем входе, если на его первом входе присутствует потенциал логического нуля. 50

Потенциал логической единицы с первого входа соответствующего блока 10 — 12 разрешает срабатывание элемента 14 под воздействием сигнала со второго входа данного блока 10 — 12 и через инвертор 13 закрывает эле- р мент 15. Потенциал логического нуля с первого входа соответствующего блока 10 — !2 закрывает элемент 14 и через инвертор 13 разрешает срабатывание элемента 15 под воздействием сигнала с третьего входа данного блока 10 — 12. Выходные сигналы элементов 14 я

15 через элемент 16 поступают на выход данного блока из блоков 10--12.

Таким образом, наличие потенциала «нуля» на первых входах данного блока 10 — 12 вызывает появление на их выходах потенциалов с нулевых выходов соответствующих разрядов регистра 1.

Следовательно, на установочном входе 24 регистра 2 появится потенциал логического нуля, на установочном 25 входе .— потенциал логической единицы, на установрчном входе 26— потенциал логического нуля, т. е. на установочных входах регистра 2 сформируется код 0100.

Этот код является обратным кодом числа

1011, т. е. числа, большего, чем число, хранящееся в регистре 1, на единицу.

Таким образом, по коду в регистре 1 на установочных входах регистра 2 формируется код, который должен быть в регистре 1 после следующего шага сложения с единицей.

Входной сигнал двоичного счетчика поступает на вход формирователя 3. По этому сиг- . налу на выходах формирователя 3 формируется тройка прямоугольных импульсов, сдвинутых один относительно другого на время переходных процессов в регистрах при установке соответствующих кодов.

Первый импульс тройки поступает на вход синхронизации регистра 2. По заднему фронту этого импульса происходит запись кода 0100 в регистр 2, Второй импульс тройки поступает на счетный вход регистра 1 на триггерах, по

:окончании переходных процессов в регистре 1 установится следующий код на единицу больше предыдущего (т. е. код 1011).

Потенциал с инверсных н прямых выходов одноименных разрядов регистров 1 и 2 поступают на выходы соответствующих полусумматоров. Поскольку эти потенциалы в каждом разряде одинаковы, то на выходах полусумматоров присутствуют потенциалы логического нуля, Нулевые потенциалы с выходов полусумматоров поступают на соответствующие входы элемента 5, на выходе которого, а значит и на втором входе элемента 4, появляется также нулевой потенциал.

Третий импульс тройки поступает на первый вход элемента 4. Однако он закрыт нулевым потенциалом на его втором входе и код иэ регистра 2 в регистр 1 не переписывается. В последующих циклах устройство функциониру-. ет так же.

Каждый цикл работы счетчика при наличии сбоев аналогичен соответствующему циклу работы устройства при их отсутствии с той разницей; что, если. произошел сбой и в регистре 1. после прибавления очередной единицы вместо правильного кода, например 1010, ошибочно зафиксируется код, например, 1100, то на выходах полусумматоров 6 — 8 появляются потенциалы.логической единицы, которые поступают на входы элемента 5 и вызывают на его выходе, а следовательно, и на втором входе элемента 4 появление потенциала логической единицы. Вследствие этого третий импульс тройки поступает через элемент 4 на вход синхрониза.ции регистра 1 и по его заднему фронту пере10308

Формула изобретения фей

5 б писывается обратный код регистра 2 в регистр !.

Таким образом, в регистре 1 вместо неправильного кода 1100 записывается правильный код 10!О.

Иаличие в момент действия третьего импульса тройки потенциала логической единицы на выходах полусумматоров б — 8 разрядов свидетельствует о том, что в этих разрядах произошло искажение информации.

Аналогично работает счетчик при сбоях в других циклах, Счетчик при сравнительно небольших дополнительных затратах аппаратуры позволяет осуществить бессбойный счет поступающих на

его вход импульсов. Кроме того, чисто логическое прогнозирование кода двоичного счетчика иа следующем шаге по его коду на предыдущем шаге позволяет при исправной аппаратуре контроля выявлять и фиксировать с точностью до разряда всякое искажение информации в счетчике. Причем, необходимо отщетить, что такое выявление и фиксация искажения информации в счетчике проводится параллельно с коррекцией его кода и не требует никакой дополнительной аппаратуры. При необходимости локализации места искажения информации может потребоваться только определенное состояние сигналов с выхода соответствующего полусумматора в момент действия третьего импульса тройки, 1. Двоичный счетчик импульсов с коррекцией, содержащий формирователь импульсов, два

Ф б выхода которого соединены с входами двух регистров на N триггерах, а третий выход с одним из входов входного логического элемента И, второй вход которого связан с выходом логического элемента ИЛИ, причем устано5 вочные входы триггеров, кроме первого, первого реп6 тра соединены с нулевыми выходами триггеров второго регистра, установочный вход первого триггера второго регистра соединен с прямым выходом первого триггера первого регистра и логические элементы И, отличающийся тем, что, с целью введения коррекции кода, искаженного в результате сбоев, в него введены N — 1 блоков коммутации и N полусумматоров, причем блоки коммутации включень(между выходами логических элементов И и со$$ ответствующими выходами триггеров, кроме первого, первого регистра и входами соответствующих триггеров второго регистра, входы полусумматоров соединены с выходами соответствующих триггеров первого и второго регистров, а выходы полусумматоров соединены со входами упомянутого логического элемента ИЛИ.

2. Двоичный счетчик импульсов с коррекцией по п. 1, отличающийся тем, что блок коммутации содержит два логических элемента И, логический элемент ИЛИ и инвертор,.причем входы логического элемента ИЛИ соединены с выходами логического элемента И, вход одного из которых через инвертор соединен со входом другого.

Источники информации, принятые во внима30 ние при экспертизе:

l. Авторское свидетельство СССР № 181877, кл..G 06 F 11/СЭ, 21.08.1966.

2. Заявка Японии № 44 — 45422, кл. 98/9/Д91, 1 !.0!.71.

БНИИПИ Заказ 3035 49

Тираж l086 Подписное

Филиал ППП Патент>, г. Ужгород, Уя. Проектная.