Стохастический преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналнстнческнк

Республнк

OnИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

{61) Дополнительное к авт. свид-ву

{51) М. Кл.

G 06 J 3/00 (22) Заявлено 22.04.76 (21) 2351839)18 — 24 с присоединением заявки № (23) Г!риоритет (43) Опубликовано 1S.06.78. Бюллетень № 22 (45) Дата опубликования описания 17.05.78

Государственный намитет

Совета Министров СССР по делам нэооретеннй н открытий (53) УДК

681.3 (088.8) (T2) Авторы изобретения

А. Н. Морозевич, В. М, Кирпичников, В. Н. Мухаметов и В. Н. Ярмолнк (71) Заявитель

Минский радиотехнический институт (54) СТОХАСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычислительной и электроизмерительной технике и предназначено для преобразования аналоговых сигналов (напряжения) в стохастический (вероятностный) код.

Устройство может быть использовано в качестве входного (внешнего) устройства стохастических вычислительных машин.

Известны аналого-стохастические преобразователи, содержащие генератор шума, квангователь, блок сравнения, сумматор, интегратор аналогового типа и элемент И, подключенные соответствую щим образом (1}. Эти известные преобразователи характеризуются значительной погрешностью преобразования, которая не может быть понижена до вели втны менее 1 — 2%. Наиболее близким к изобретению является преобразователь, содержащий генератор случайных чисел, вход которого подключен к тактовому входу преобразователя, преобразователь код-напряжение, входы которого соединены с выходами разрядов генератора случайных чисел, первый блок сравнения, первый вход кото. рого соединен с выходом преобразователя коднапряжение, а второй вход подключен к информационному входу преобразователя, первый элемент И, первый вход которого соединен с выходом первого

2 блока сравнения, а второй вход подключен к так. товому входу преобразователя, первый счетчик, вход которого подключен к тактовому входу уст. ройства, второй счетчик, элемент задержки, блок элементов И, выход которого подключен к выходу преобразователя, входь1 соединены с выходами разрядов второго счетчика, а управляющий вход соединен с выходами разрядов второго счетчика, а управляющий вход соединен с выходом первого счетчика и со входом элемента задержки, выход которого соединен с установочным входом второго счетчика (2). Однако в нем погрешность преобразования ограничивается снизу точностными характеристиками входящих в него элементов. Оо15 новное BJIHBHHc H8 cTRTHcTNwcK погРешность IIPO раэователя оказывает блок сравнения (пороговьй элемент) .

Целью изобретения является повышение точ ности стохастического преобразователя эа счет уменьшения влияния характеристики блока сравнения на результат преобразования. В описываемом преобразователе это достигается тем, что он содержит триггер, инвертор, второй блок сравнения, первый вход которого соединен с выходом преобразователя код-напряжения, а второй вход под

611221 ключен к информационному входу преобразовате. ля, второй элемент И, первый вход которого соединен с выходом второго блока сравнения, а второй вход подключен к тактовому входу преобразователя, элемент ИЛИ, первый и второй входы которого подключены к выходам, соответственно, первого и второго элементов И, а выход соединен с входом второго счетчика, нулевой и единичный выходы триггера соединены с третьими входами, соответственно, первого и второго элементов И, выход инвертора соединен с единичным входом триггера, первый вход инвертора соединен с нулевым входом триггера и с выходом элемента ИЛИ, а второй вход — с выходом элемента задержки и с установочным входом генератора случайных чисел.

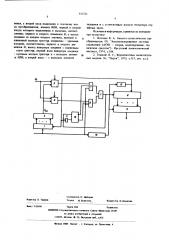

На чертеже представлена блок-схема описываемого преобразователя.

Он содержит последовательно соединенные генератор 1 случайных чисел, преобразователь 2 код напряжение, первый 3 и второй 4 блоки сравнения, первый 5 и второй 6 элементы И, элемент

ИЛИ 7, счетчик 8 и блок 9 элементов И, а также триггер 10, выходы которого соединены с третьи-, - ми входами элементов И 5 и 6, а входы (нулевой-прямо, а единичный-через инвертор 11) соединены с выходом элемента ИЛИ 7, и счегщк 12, вход которого соединен с тактовым выходом устройства и со вторыми входами элементов И 5 и 6, а выход — с управляющим входом блока 9 элементов И и через элемент задежки 13-с установочным входом счетчика 8, с установочным входом генератора 1 и со вторым входом инвертора 11.

В исходном положении триггер 10 и счетчики 8 и 12 находятся в нулевом состоянии. На выходе преобразователя код-напряжение U =U gq

При включении устройства входной сигнал Uх поступает на первые входы блоков 3 и 4. В течь нни первого такта происходит сравнение U . макс и U на обоих блоках сравнения, причем, от выхо ных сигналов блоков 3 и 4 в первом такте по тактовому импульсу, через открытьre инверсным выходом триггера 10 (триггер 10 "в нуле") элемент И 6 и элемент ИЛИ 7 в счетчик 8 заносится информация с выхода блока 4. Одновременно с этим с выхода элемента ИЛИ 7 информация с выхода блока 4 в парафазном коде, который формируется с помощью инвертора 11, поступает на единичный в прямом коде и на нулевой в обратном (через инвертор 11) входы триггера 10. Кроме того, по этому же тактовому сигналу изменяется состояние генератора 1, и на входе преобразователя 2 формируется новое случайное напряжение.

Стохастический преобразователь, содержащий

З генератор случайных чисел, вход которого подклю. чен к тактовому входу преобразователя, преобразователь код-напряжение, входы которого соединены с выходами разрядов генератора случайных чи сел, первый блок сравнена, первый вход которого соединен с выходом преобразователя код-напряджение, а второй вход подключен к информационному входу преобразователя, первый элемент И, первый вход которого соединен с выходом первого блока сравнения, а второй вход подключен к

45 тактовому входу преобразователя, первый счетчик, вход которого подключен к тактовому входу устройства, второй счетчик, элемент задержки, блок элементов И, выход которого подключен к выходу преобразователя, входы соединены с выходами раэ50 рядов второго счетчика, а управляющий вход сое. динен с выходом первого счетчика и со входом элемента задержки, выход которого соединен с yctaновочным входом второго счетчика, о т л иИ ч а ю шийся тем, что, с целью повышения точности, он содержит триггер, инвертор, второй блок сравнения, первый вход которого соединен с выходом преобразователя код- напряжение, а второй вход подключен к информационному входу преобразователя, второй элемент И, первый вход которого соединен с выходом второго блока сравТаким образом, перед началом следующего (i-го) такта на выходе преобразователя 2 сформировано U 1 а в триггере 10 — информация, записанная в счетчик 8 в (i — 1)-м такте. В i-м такте считывается информация с блока 3 или 4, выбранного состоянием триггера 1О, и заносится в счетчик 8 и триггер 10.

Следовательно, триггер 10 обеспечивает запоминание состояния выбранного блока сравнения (с которого считывалась информация) в одном такте.

Это позволяет определять блок сравнения, состояние которого более точно (без влияния гестерезиса) отражает знак разности Ох1 — 0 1 в следующем такте.

10 Счетчик 12 служит для подсчета тактов преоб раэования, При достижении числом тактов величины, необходимой для получения заданной статисти. ческои погрешности, на выходе счетчика 12 появляется сигнал, который, поступая на управляющий вход блока 9 элементов И, опрашивает состояние счетчика 8, а спустя время задержки элемента 13 устанавливает счетчик 8, триггер 10 и генератор 1 в исходное положение.

Таким образом производится преобразование

Ох в позиционный код методом статистических ис. пьпаний.

Такая схема устройства обес .ечивает уменьшьние статистической погрешности преобразования за счет сокращения влияния неидеальности характе ристик блоков сравнения lii результат преобразования, вследствие чего может быть достигнуто относительное уменьшение ширины эоны нечувствие тельности аналого- стохастического преобразователя до восьми раз.

Формула изобретения