Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДИТЫЬСТВУ (11 611283 (61) Дополнительное к авт. свил-ву (22) Заявлено 25.10.76 (21)2414292/18-2 с присоединением заявки № (23) Приоритет

Я (51) М, Кл. (- 1 1 С 1 7/00

Государственный номнтет

Совета Инннотров СССР оо делам нзобретеннй и открытнй (53) УДК 681.327.66 (088.8) (43} Опубликовано 15.06,78.Бюллетень №2 (45) Дата опубликования описания 15»05.78 (72) Авторы изобретения К. Г, Волков, В, И. Корнейчук, А. В. Городний и H. Il. )Чиргородская

Киевский ордена Ленина политехнический институт имени 50-летия

Великой Октябрьской социалистической революции (71) Заявитель (54) ПОСТОЯННОЕ ЗА ПОИИНАЮШЕЕ УСТРОЙСТВО. большая разрядность числового блока, низкая надежность устройства.

Известно и другое постоянное запоминающее устройство 12, которое содержит дешифратор адреса, выходы которого соедийены со входами числового блока, шифратор и сумматоры по модулю два по числу выходов числового блока.

Недостатками известного устройства являются большое число элементов связи, используемых при реализации устройства, Изобретение относится к области вычислительной техники, в частности к постоянным запоминающим устройствам (ПЗУ), Известны постоянные запоминающие устройства 11, 2) . Одно нэ известных ПЗУ 5

11) содержит числовой блок с большим числом элементов связи, либо с большим числом прошитых сердечников, вход которого соединен с дешифратором, а выход- с усилителем считывания, формирователи адрес- !О ных токов, Недостатком известного устройства является большое потребление мощности, а также неравномерность нагрузки на адрес. ные шины. 15

С целью повышения надежности устроФства путем сокращения числа элементов связи предлагаемое постоянное запоминающее . устройство содержит первую и вторую групп ы элементов И, сдвиговый регистр и дополнительный сумматор по модулю два, при этом выходы числового блока подключены к первым входам соответствующих сумматоров по модулю два, ко вторым входам которых подсоединены выходы соответствующих элементов И ервой группы, первые входы которых соединены с соответствующими входами шифратора, а вторые — подключены к выходу goполнительного сумматора по модулю два, входы которого соединены с выходами ввлэментов И второй группы, первые входы которых подключены к соответствуккдим входам дешифратора адреса, а вторые - к соответствующим выходам шифратора, входы которого соединены с выходами регистра сдвига.

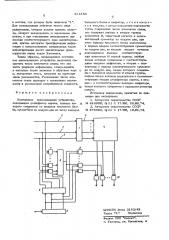

1->а чертеже изобра;кена блок-:-с;.-, . э и;:-:: лагаемого постоянного за>уо>»>1>на«оу>>его ройства.

Постоянное запоминающее усФРойс:>"ву) одержит дешифратор адреса 1, кодовые 1!:.;:>н,;

2, адресные шины 3, числовой блок 4, регистр сдвига 6, шифратор 6, втору>о гру.>пу элементов И 7, дополнительный сум:. .-* тор по модулю два 8, нерву>о -,pynt!Ey элементов И 9, сумматоры по модулю;Ba } О, /

>дешифратор адреса 1 через Ggpec;I>.re шины 3 подключен ко входам числового блока 4, выходы которого соединены с пер-выми входами соответствующих сумматоров по модулю два 1О, вторые входы которь-.:. подключены к выходам соотватстuy3ot>Hих элементов И первой группы 9, пару)ые входы которых подсоединены к соот>)етстиу>ощим входам шифратора 6, а вторые — к выходу дополнительного: сумматора по модулю два 8, входы которого Hîäcoåä>I>!eít,> к выходам соответствующих элементDB И второй группы 7, первые входы которых подсоединены к соответствующим входам 2 дешифратора 1, а вторые входы к соответст= вующим выходам шифратора 6, входы которого подсоединены к выходам регистра 5, Предлагаемое ПЗУ работает сл ед ууещпм образом. Пусть, например„в числовом 6>о-ке 4 хранится двоичпал H!II)opмацил, закодированная такйм образом„что в ка)кдом разряде машинного c» o > >G цифра записанn прямом или в обратном коде с цель>о со>:pG;H". ния кОличества заппсапнь>х едуупн > до мну;>1«. мума„СледОВательно, при считывании !Iеобходимо произвести поразрядную опа}3а>111>о инвертирования там, где это требуетсл при помощи, так называемого, кода п>1.3ертнроВания. Код инвертировапу>л выбуг)-. -;-. л c;:1-ду>ощ>г.f образом, Часть pnзрлдов j -"у о столбца, а Qp -го разряда слов, которо требуется записать в числовой блок) Об>}еднняются В Группу и есл>1 число e,>t:11>ц . этой группе больше числа "пулей", гр»:пууа

В числовой блок "аписывается в обратном коде, а в определенном разряде кода ип-.

Вертироваууия записывается " едп>11>> а „(;у>у>соб объединения разрядов кода столбца н гр>ппы и число групп выбирается аналогичным образом, как и в коде Хэмм}инга, где число групп К определяетсл из ВЬ>}3аже>уи>1: к> 0о,(р () где Р - разрядность кодов столбцо>3„ ,Количество кодов инвертирования равно, соответственно, количеству столбцов числВого блока КОДЫ инверт>урованил -СОГ)1асно схеме поступают с выхода ши(> >зато>)а 6, В режиме выдачи информация, хранящаяся в числовом блоке, корректируется следу>с щим образом.

} «1- - 1 -11>-";tgt;f 1.-.11лс г уогтут>э,.ую, ;). .:,, и С;11 :> -3 > Га 3»tP 1 ет.-л„фРат}3Ра

rt! ОС 3, У- а ПЕРВ>,>Е ВХОД >.-.1 ЭЛЕМ BНТОМ Я второ" группы 7, На вторые входы эле»I 1>1тг,>- И I>Tr3potI гоупт>у 7 с в|у Ода }щуфва» тора 6 поступает код инВертирования ) ГО столбпа9 т,G„, ) -го разряда счит>=}Баемого

ЛОВа В 3аЗУЛЬ.->..ат,«ПОЛВЛЕ>1ИЛ Снгга *а "ЕДИнниа на (-Ом Входе >у>ифратора 6 с Вы»

- - -! =1 t3 > >AC.rPQ - 1>- 1-" 3 ГЕЗУ.1- 8 Te ВЬ>пг.:лу" Ht>ß эл-.:.=1"=II"., GìH И втор 3N Групны 7

Оп .. >)а>3яи поразрлдноГО лоГического умноже п>ул Над кодом адреса и кодом инвертирова>пхя>

Гд, ):1>д дополпител>«ного суммато}3а по мо»

„1 :;ут ; — >Bn 8 пост у>аoT Определенное коли"г> " и ".3, „ .= с:цу количество "едит птт 1тче 11Р, г ttn }«" г опе, до> олнитель>1ОГО .",..; „::-тора >Эо >«."oi) два 8 появляется код кот р-,у>1 поступает на вторые входы эууемантов И цер>3ойу гo -п>u> 9 н на вь>ходе одного из Gлемепт в И первой группы 9 а имеппо того, первый вход которого соеди4; неп с > -ым Вьгсодом Регистра сдвига Б

IIOEID rHOTCH >rOg "1" и ПОСТУ>>аэт На ВТОРОЙ

B>t О, ()Д П 1)ГО ИЗ C V»II 1G I OPOB ПО МОДУЛЮ It BG

> Q >1 rr;*13РУЛ В;.Р Кr>Tat>OT O ПОСТУПИВТ КОД

Л;-; o аз>3лда 1 -го =лове,храплщег->ся в чис)у-;.Г,;:;.,„- у;ло>г) 4.," >IH.".. . О613азо>.1 2 данном раь)ряде

1-}у >1 .хоr! HT >11}ве>3Т>>рованпе.,ЦН>1 1 +3. столб." та «". tttGCT>3»rат P" Ð3й КОД ун>ВЕРТИРОВаппя, ;-„ ;;т>око;цм тл-,.-ой. -Нто в результате Выпол:, >t 1: : : j t, )Рой> У !3 GII!o >1 э Гуе». с>1 1 Ов И

-п«л.;.-.:.-Нп> 11>313л;.—;;-..-. >>кого у>огк:; -ского умноже-, ;<1 ??,-;3 t)>!i3n «уолр у" цу, е)}1.,>уогo су}»уматора Но м;3ду>Г о дBQ 8 -;iocòy>1àа Р четное количество

"е н»11111". in выходе его — код "С>», на вто=

",1, ",1-Е РЛ>,ОГО ИЗ C т ММВТОРОВ П,3 МОДУ, i.;,G.-. 3лда т:; >с код нулл и, >, .". °, 11111)ра этого 1)азрлда 1 -I"o !

-;;:n3! ÿ -;-;1>T;.;..:,! Tcë без изменения. Итак.

:,: ..:.:::„::;;3а>ул>ууегу)сл 1-:t>3. 1 -м» адресу

1.:; : -" . о >:->уо):орь.»1 н>>тервалом времени) разряд за разрядом с коррекцией тех разрядов, r . Чраб3уетс". ;., 1 lp t .-1 f :е чи )>ОВ1)1 0 блока а4 или НрН

t1;;.„е>>анни информации в нем, в шифраторе

6 ".- Н!tc!!-=-.toòcH новые значения кодов инBåp-:. 3c 1tGI1IIH Числовой блок известного .- >I-3. усто::;. тва имеет z запоминаклдих элау... . ."1тов а числовой блок предлагаемого

ycTpo IcTBn — только g запоминающих элема> тов, что облегчает его интегральное и-у>,т>уа>уууа, у» лучаа применения числового блока:— . Интегральном исполнении в вице ма Tp!Iz« ".озможно использование дефектных матриц,.т,е, таких, где присутствуют дефекты вида "отсутствие элементов связи

61 1253

Заказ 3163/42

7 Подписное в местах, где должны быть записаны "1".

Для максирования дефектов такого вида информацию, которая должна хранить матрца, следует закодировать ог эеделенным об разом, а при считывании декодировать при помощи соответствующего кода инвертирова,ния, причем алгоритм трансформации информации с использованием специальных кодов инвертирования имеет значительные преимущества перед кодом Хэмминга. 1О

Таким Образом, предложенное постоянное запоминающее устройство позволяет сократить число элементов связи; так как часть разрядов информации, содерх,ащаяся. в числовом блоке записана в обратном копь и, вследствие этого, нагрузка на адресные шины уменьшается. Уменьшение числа элементов связи приводит к повышению надежности и уменьшению потребляемой мощности, 20

Формула изобретения

Постоянное запоминающее устройство, coAepKBmee дешифратор аареоа, выходы ко- 25 торого соединены со входамн числового бло.г ка1 сумматоры по модулю gBB по числу выходов числового блока и шифратор, о т л и ч а ю щ е «« е с я тем,что, с целью повышения надежности путем сокрашения числа элементов связи, оно содержит первую и вторую группы элементов И, сдвиговый регистр и дополнительный сумматор по модулю два, при этом выходы числового блока подключены к первым входам соответствующих сумматоров

-по модулю два, ко вторым входам которых подсоединены выход ы соответствующих элементов И первой группы, первые входы которых соединены. с соответствующими входами шифратора, а вторые — подключены к выходу дополнительного сумматора по модулю два, входы которого соединены с выходами элементов И второй группы, первые входы которых подключены к соответстствуюшим BxogBM дешифратора адреса, а вторые — к соответствующим выходам шифратора, входы которого соединены с выходами регистра сдвига, Йсточники информации, принятые во внимание при экспертизе; 1. Авторское свидетельство СССР

М 418800е Q 1 1 С 17/00, 26.06,74, 2„ Авторское свидетельство СССР

% 376808, (j-11 С 17/00, 10.01,73.

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4