Устройство для контроля оперативной памяти

Иллюстрации

Показать всеРеферат

Соноз Советских

Социалистических

Республик (ii I 611257

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 10.08,76 (21)2396263/18-2 с присоединением заявки № (23) Приоритет

2 (51) М. Кл. ф 11 С 29/00

Государственный комитет

Совета Министров СССР ио делам изобретений и открытий (43) Опубликовано15.06.78. Бюллетень №22 (53) УДК 681.327.6 (088,8) (45) Дата опубликования описания 10.05.78. (72) Авторы изобретении

В. С. Штолик, Н. А, Давыдов и И, В. Матышев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАТИВНОЙ

ПАМЯТИ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для тестового контроля совместной работы оперативной памяти (ОП) и запоминаюшего устройства ключей памяти (ЗУКП) ЭВМ, а также для контроля данных типов памяти в отдельности.

Известно устройство для контроля оперативной памяти, содержащее регистр данных памяти, схему свертки по модулю 2, триг- 10 геры контрольных разрядов, блок сравнения, свертку по модулю q $1) . Данное устройство не обеспечивает контроля информации с определением места и характера групповых сбоев. 15

Известно также устройство для проверки запоминающих устройств, содержащее блок формирования данных, блок формирования адресов, блок управления 21 . Данное устройство не позволяет проверять совмест- 20 ную работу двух разных типов запоминаюших устройств (ЗУ), имеюшик обшие кодовые шины записи и чтения, Иэ известных устройств для контроля запоминаюших устройств ЗВМ наиболее близ- о ким по технической сущности является уст ройство, содержащее блок управления, связанный с регистром адреса, формирователем и блоком обработки информации, приемный регистр 3 .

Недостатком этого устройства является отсутствие возможности производить контроль запоминаюших устройств (ЗУ), включающих в себя собственно оперативную память (ОП) и запоминаюшее устройство ключей памяти (ЗУКП ) имеюших обшие кодовые шины записи (КШЗ1 и обшие шины чтения (КШЧ) информации, Цель изобретения — расширение области применения данного устройства путем одновременного контроля эапоминаюших устройств разных типов.

Предлагаемое устройство отличается тем, что оно содержит коммутатор, регистр записи, дополнительный приемный регистр и распределитель, вход которого соединен с блоком управления, а выход — с приемными регистрами и с управляющим входом коммутатора, информационные входы которого подключены к выходам приемных регистров, 611257 к выходу регистра записи и к соответствую шум вьйодам блока обработки информации.

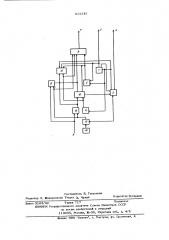

На чертеже представлена структурная схема устройства для тестового контроля оперативных запоминающих устройств, Описываемое устройство содержит регистр адреса 1, кодовые шины 2 : адреса, блок 3, управления, информационные шины 4 блока управления, формирователь S для ОП, коммутатор. 6, кодовые шины 7 записи, приемный регистр 8, кодовые шины 9 чтения, блок 10 обработки информации, регистр 11 записи кодов ключей памяти, дополнительный приемный регистр 12, распределитель

13, генератор импульсов 14, блок 15 индикации.

Проверка ОЗУ заключается в записи с последующим контрольно считыванием определенных видов информации в соответствии с испытательными тестами, ю

При проверке совместной работы ОП и

ЗУКП в каждом цикле обращения к ОЗУ происходит обращение к обоим гипам памяти, цикл обращения состоит из такта чтения и такта записи. В такте записи производится запись информации по одним и тем же кодовым шинам

7 записи в ОП и ЗУКП. Коды информации для ОП и ЗУКП различные, Под управлением синхра-, сигналов из распределителя 13 моменты записи для ЗУКП и ОП разнесены во времени внутри зО такта. Вначале производится запись кода ключа памяти, а затем осуществляется запись информации в Off-"

Регистр адреса 1, управляемый блоком .3, определяет адрес ячейки памяти, к которой производится обращение,.Информация с выходов регистра адреса 1 передается в запоминающее устройство. по кодовым шинам 2 адреса, Информация на запись в ЗУКП посту 4р пает с выхода регистра 11 записи кодов ключей памяти в коммутатор 6 .оттуда при наличии синхросигнала из распределителя поступает по кодовым шинам 7 записи в

ЗУКП. Информация в регистре 11 записи 4s кодов ключей памяти может меняться по переполнении регистра адреса 1 при работе в счетном режиме или может быгь установлена с помощью органов управления на пуль-, те при работе в регистровом режиме. Управ-50 ление занесением информации в регистр 11 записи кодов ключей памяти осуществляется через блок 3 управления. Информация с выходов регистров ll записи кодов ключей памяти поступает также в блок 10 обработки информации и в блок 15 индикации.

Информация. на запись в 0П поступает иэ формирователя 5 для ОП в коммутатор 6. и отч уда нри наличии синхросигнала иэ 60 распределителя 13 по кодовым шинам 7 запаса в ОП.- Информация формирователя 5 меняется под воздействием сигналов блока

3 управления или информации регистра адpecs 1 ° Блок 3 управления генерирует последовательность проверочных тестов и выдает сигналы управления в проверяемое

ОЗУ по информационным шинам 4. В такте чтения происходит считывание ранее записанной информации из ОЗУ, В первой половине такта чтения производится чтение с контролем информации из

ЗУКП, во второй половине — из ОП.

Если произошло наложение на кодовых шинах 9 чтения информации из ОП с информацией из ЗУКП, то в блоке 10 обработки информации вырабатывается сигнал несравнения, поступающий в блок 3 управления,. что является сбойной ситуацией, Введение новых блоков расширяет о6ласть применения устройства и позволяет полностью автономно проверять ОЗУ с различной структурой построения. Искпючение цовторной проверки ОЗУ в составе ЭВМ вдвое сокращает сроки наладки всего вычислительного комплекса.

Формула и э о б р е т е н и я

Устройство для контроля оперативной памяти, содержащее блок управления, связанный с регистром адреса, формирователем и блоком обработки информации, приемный регистр, о т л и ч а ю ш е е с я тем, что, с целью расширения области применения путем одновременного контроля запоминающих устройств разных типов, онб содержит коммутатор, регистр записи, дополнительный приемный регистр и распределитель, âõод которого соединен с блоком управления, а выход - с приемными регистрами и с управляющим входом коммутатора, инфорI мационные входы которого подключены к вь ходам приемных регистров, к выходу регистр ра записи и к соответствующим выходам блэка обработки информации, Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 333559, кл. (06 Р 11/02, 1972, 2. Патент США № 3751649, кл, Я 11 С 29/00, 1973.

3 Авторское свидетельство СССР

Э

¹ 246158, кл. 42,,ttf 1969.

611257

Составитель В. Гордонова

Редактор Л. Жаворонкова Техреп Q мужик

Корректор B,Ñåpäþê

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4

Заказ 3163/42 Тираж 717 Подписное

l1HHHllH Государственного комитета Совета Министров СССР до делам изобретений и открыгий

113035, Москва, Ж-35, Раушская наб., д. 4/5