Устройство динамической памяти

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (11) 611299 (о!) Дополнительное к авт. свил-пу (22) Заявлено 10.01,72(21) 1738287/18 — 21 с прнсоелннением заявки Ле (23) Прнори сет (43) Онублнконано 15.06.78.Бюллетень %:.2 (45) Дата опубликования описания 12,05.78 (51) М. Кл.

Н 03 К 17/О»

Государственный номнтет

Совета Мнннстров СССР во делам нзооретеннй

H отнрьпнй (53) УДК 6 2 1. 31 8 (088. 8) (72) Авторы изобретения

B. М. Голованевский, С. А. Коган, К. H. Новиков и Л. И. Тильман (71) Заявитель

Г1роектно-конструкторский институт конвейеростроения (54) УСТРОЙСТВО ДИНАМИЧЕСКОЙ ПАМЯТИ

Изобретение относится к области вычислительной техники и может быть использовано в автоматике и других .областях техники при построении счетчиков, регистров, рас пределителей и т.. и.

Известно устройство динамической памяти, содержащее феррит- транзисторные ячей-Г13

Однако это устройство имеет раздельные шины включаюших и выключающих сигналов, что затрудняет его применение.

Известно устройство динамической памяти, содержашее три феррит-транзисторные ячейки, выход первой из которых соединен с единичным входом второй, выход второйс первым нулевым входом третьей, выход которой соединен с единичным входом первой феррит-транзисторной ячейки, и четыре шины тактовых импульсов, первая из которых соединена с нулевым входом первой феГ рит-транзисторной ячейки, третья — с единичным входом третьей, а четвертая — с первым нулевым BxoQQM второй феррит-транзисторной ячейки )2 J.

Недостатком атого устройства является невозможность установления состояния памяти без ее разрушения.

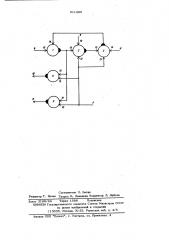

С цельо упро:пения управления и конто роля в предлагаемое устройство введены две дополнительные феррит-транзисторные ячейки, нулевой вход первой из которых обьединеп с единичным входом второй дополнительной феррит-транзисторной ячейки

10 и подключен к выходу первой феррит-транзисторной ячейки, а единичный вход первой дополнительной феррит-транзисторной ячейки подключен к нулевому входу второй дополнительной ячейки, вторым нулевым входом

1 второй и третьей феррит-транзисторных ячеек и шине переключаюшего сигнала.

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит три основные и пве дополнительные статические ячейки 1-5 соответствено, четыре шины 6-9 такToBbix импульсов и сигнальные шины 10 и 11 включения и выключения динамической памяти. Каждая статическая ячейка

611299 имеет входы 12 и 13 подготовки и считывания элементов соответственно.

В исходном состоянии сигналы на шины

6-9 тактовых импульсов не поступают. В выключенном состоянии третий тактовый

5 сигнал, поступаюший на шину 8, подготавливает ячейку 3, остальные ячейки не подготовлены (ячейка 4 может быть также подготов ена). При приходе второго тактового сигнала считываются ячейки 2, 3 и 5, а ячейка 4 подготавпивается> что вызывает срабатывание ячейки 3, которая подготавливает ячейку 1. Qanee третий тактовый сигнал вновьподготавливает ячейку 3, а четверты8 повторно считывает ячейку 2. Первый тактовый сигнал считывает ячейку 1, вызывая ее срабатывание, а ячейка 1 подготавливает ячейки 2 и 5 н считывает ячейку 4, с выхода которой {шина 10) снимается оди ночный сигнап включения динамической па-. 2О мяти. В третьем такте вновь подготавливается ячейка З,а сигнап в четвертой ячей ке 4 считывает ячейку 2, которая, сработав, считывает ячейку 3, последняя подготавпивает ячейку 1. В первом такте снова сра» батывает ячейка 1, которая подготавливает ячейки 2 и 5, считывает ячейку 4 эта ячейка теперь уже не срабатывает, так как не подготовлена. Затем четвертый тактовый сигнал считывает ячейку 2, а та — ячейку 30

3. Dance цикл работы повторяется.

Таким образом, в случае включенной динамической памяти к моменту возможного прихода снгндпа H& шину 7 во втором такте подготавливаются только ячейки 5 и 2. 35

Пришедший сигнап вызовет их срабатывание и подготавпнвает ячейку 4, при этом с выхода ячейки 5. (шина 11) снимается одиноч- ный сигнап выключения динамической памяти. Одновременно ячейка 2 повторно считы- 40 вает ячейку 3, которая не срабатывает, так как подготовлена лишь в третьем. такте, поспе чего схема возвращается. в исходное выключенное состояние.

Таким образом, в предпоженном устройстве относительно просто и надэжно осуществпено управпение и контроль.

Формула изобретения

Устройство динамической памяти, содержашее три феррит транзисторные ячейки, выход первой иэ которых соединен с единичным входом второй, выход второй — с первым нулевым входом третьей, выход которой соединен с единичным входом первой феррит-транзисторной ячейки, и четыре шины тактовых импульсов, первая иэ которых соединена с нулевым входом первой ферриттранэисторной ячейки, третья-с единичным входом третьей, а четвертая — с первым нупевым входом второй феррит-транзисторной ячейки, о т и и ч а ю ш а я с я тем, что, с цепьюупрошенияуправпения и контроля, введены две допопнитепьные феррит-тран.зисторные ячейки, нулевой вход первой из которых объединен с единичным входом второй допопнитепьной феррит-транзисторной ячейки и подключен к выходу первой ферриттранзисторной ячейки, а единичный вход первой допопнитепьной феррит-транзисторной ячейки подключен к нулевому входу второй дополнительной ячейки, вторым нулевым входом второй и третьей феррит-транзистор-. ных ячеек и шине перекпючаюшего сигнала.

Источники информации, принятые во внимание при экспертизе:

1. Гуревич Е. Н. и др. Ферро-транзисторные элементы и их применение в цифровых автоматических устройствах, М., 1963, с. 159.

2. Магнитные цифровые элементы, М., "Наука, 1968, с. 63.

611299

Составитепь Л. Багин

Редактор Т. Янова Техред M. Левицкая Корректор Л. Не6опа

Заказ 3168/44 Тираж 1086 . Подписное

ЦНИИПИ Гасударственного комитета. Совета Министров СССР по депам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5 филиап ППП Патент, г. Ужгород, уп. Проектная, 4