Цифровой интегратор

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналмстмческмх

Ресаубамк

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К, АВТОР СКОМУ СВМДНИЛЬСТВУ (1 )612263 (6!) Дополнительное к авт. свил-ву (22) 3aявлено03.01.77 (2l) 2443743/18-24 с присоединением заявки №(23) Приоритето†(43) Опубликовано 25.06.78фюллетеиь № 23 (45) Дата опубликования описания 26.05.78

2 (51) М. Кл.

Cj 06, ) 1/02

Госудеротееннвй комитет

Совета етннистров СССР но делам изобретений н открытий (53) УДК 68 1. 1 4 (088.8) (72) Авторы изобретения

Б. В. Казаков и А, А. Климович (71) Заявитель (54) БИФРОВОИ ИНТт:ГРАТОР

Изобретение относится к вычислигель ной технике и может быть использовано прв разработке интеграторов для хроматографов.

Известен интегратор без разветвленных

Э арифметических устройств, основанный на переводе цифровой информации с базовой линии в аналоговом вычитающем устройстве на входе преобразователя напряжения в частоту Pl) .

Недостатком его является низкая точность при йитегрировании хроматографичес ких функций.

Наиболее близким по технической сущ ности к предложенному является цифровой интегратор, содержащий аналого-цифровой преобразователь, первый и второй триггеры, дешифратор, выход которого соединен со входом первого триггера, первый и второй элементы И, первый и второй счетчики 2 ° пако для этого интегратора также ха рактерна недостаточная точность интегрирования хроматографических функций.

Бель изобретения - повышение точности цифрового интегратора.

Это достигается тем, что в предложенный интегратор введены дополнительно генератор тактовых импульсов, элементы И, первый и второй счетчики, схема сравнен та, к блок индикации, причем выход генератора тактовых импульсов соединен с первыми входами первого, второго и первого дополнительного элементов И, выход аналого-цифрового преобразователя соединен с первыми

1О. входами второго, третьего и четвертого дополнительных элементов И, выход первого элемента И соединен со входом второго триггера, прямой выход которого соединен со- щорыми входами второго и второго дота полнительного элементов И, а инверсный поход со вторыми входами первого и третьего дополнительных элементов И, выходы которых соединены соответственно с первым и вторым входами первого дополнительного яа счетчика, выход второго элемента И соединен с первым входом первого счетчика, второй вход которого подключен к выходу второго дополнительного элемента И, выходы первого и первого дополнительного

25 счетчиков подключены соответственно к

Всесоюзный научно-исследовательский и проектно-конструкторский институт комплексной автоматизации нефтяной и газовой промъппленности

612263 йервому и второму входам схемы сравнения, выход которой соединен со вторым входом четвертого дополнительного элемента И, выход которого соединен со входом второго дополнительного счетчика, и с первым входом пятого дополнительного элемента И, выход второго дополнительного счетчика соединен со входом дешифратора, прямой вы-, ход первого триггера соединен со вторым входом первого элемента И, а инверсный !О выход - со входом питого дополнительного элемента И и с первым входом блока индикации, выход пятого дополнительного элемента И соединен со входом второго счетчйка, выход которого подключен ко второму входу блока индикации.

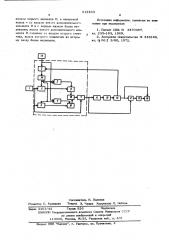

На чертеже показана структурная схема интегратора.

Она состоит из аналого-цифрового преобразователя 1, элементов И 2-8 счетчиков

9-12, триггеров 13, 14, дешифратора 15, блока 16 индикации, генератора 17 тактовых импульсов, схемы сравнения 18, Устройство работает следующим образом. 25

Хроматографический сигнал в виде напряжения поступает на вход аналого-цифрового

1 преобразователя, С выхода преобразователя 1 импульсы поступают на первые входы элементов И 5, 6; 7. зо

Устройство работает в режиме, задаваемом генератором 17. В первый такт количество импульсов суммируется счетчиком

9, в следукиций такт р;риггер 14 переключает прохождение импульсов ца счетчик 10.

Их количество сравнивается схемой 38 с количеством импульсов, подсчитанных счет-, чиком 9. После того, как количества импульсов в счетчиках 9 и 10 станут равными, на выходе схемы сравнения 18 появ4О ляется сигнал, переключающий элемент И

7 на прохождение всех последующих импульсов в анализируемом такте на вход счетчика 11 селектора пиков и элемента И 8. В счетчике 11 эти импульсы подсчитываются, 45 и их количество сравнивается с числом, заложенным в дешифратор 15 и определяющим порог срабатывании селектора пиков. Если превьпнение порога срабатывания не проис50 ходит,с приходом следующего тактового импульса опрокидывается триггер 14, счетчик 9 -переводится в нулевое состояние. Б течение этого такта входные импульсы проходят íà вход счетчика 9 и сравниваются . с числом импульсов в счетчике 10, накопленным за предыдущий такт. При превышении порога срабатывания на выходе дешиф ратора 15 появляется си пал, вызывающий

ОщюхидыВение parrepa 1 3 и изменение pe» @) жиме работы элементов И 2, 8. В этом режиме число, записанное на счетчике 9 (или 10) остается неизменным на все время обсчета пика, а показания счетчика 10 (или 9) сбрасываются в конце каждого такта. B каждом такте на счетчик 11 через элемент И 7 поступают импульсы после вычитания в счетчике 9 (или 10), соответствующие значению базовой линии хроматографического сигнала перед началом пика.

В конце пика хроматографического сигнала прекращается действие сигнала на выходе дешифратора 1 5, срабатывает триггер 13, прекращается действие сигнала, который поступал на элементы И 2, 8 и блок 16. По окончании этого сигнала чис ю импульсов, накопленное в счетчике 12, выдается на блок 16, индикации. Вся схема возвращается в исходное состояния.

Ф .о р м у л .а и з о б р е т е н и я

Цифровой интегратор, содержащий аналого-цифровой преобразователь, первый и второй триггеры, дешифратор, выход которого соединен со входом первого триггера, первый и второй элементы И, первый и второй счетчики, отличающийся тем, что, с целью повышения точности, в него введены дополнительно генератор тактовых импульсов, элементы И, первый и второй счетчики, схема сравнения, блок индикации, причем выход генератора тактовых импульсов соединен с первыми входами первого, второго и первого дополнительного элементов И, выюд аналого-цифрового преобразователя соединен с первыми входами второго, третьего и четвертого дополнительных элементов И, выход первого элемент И соединен со входом второго триг- . гера, прямой вход . которого соединен со вторыми входами второго н второго дополнительного элементов И, а инверсный выход - со вторыми входами первого и треть» его дополнительных элементов И, выходы котооых соединены соответственно с первым . и вторым входами первого дополнительного начетчика, выход второго элемента И соединен с первым входом первого счетчика, второй вход которого подключен к выходу второго дополнительного элемента И, выходы первого и первого дополнительного счетчиков подключены соответственно к первому и второму входам схемы сравнения, выход которой соединен со вторым входом четвертого дополнительного элемента И, выход которого соединен со входом второго дополнительного счетчика и с первым входом пятого дополнительного элемента И, выход второго дополнительного счетчика соединен со входум дешифратора, прямой выход BBDRnrn rnxrr пя rnanwunu rn т палм

612263

Составитель H. Палеева

РедактоР Е. КРавпова ТехРед Э. Чужик Корректор Л. Небола

Заказ 3463/44 Тираж 826

1ЛНИИ!1И Государственного комитета Совета Министров СССР по деаам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. /

4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 входом первэго элемента И, а инверсный выход - со входом пятэго дэпэлнительнэгэ элемента И и с первым входом блока индикации; выход пятого дополнительного элемента И соединен сэ вхэдом второго счет чика, выход кэтэрэгэ подключен ко второму вхэду блока индикации.

Источники информапии, принятые во внн мание при экспертизе:

1 ° Патент США % 3470367, кл. 235-183, 1969, 2. Авторское свидетельство 34 443249, кл. С 06 J 3/00, 1972.