Устройство для контроля блоков постоянной памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()1} 6) 2287

Союз Советсиин

Социалистических

Республик (61} Дополнительное к авт. свид-ву (22) За влево 29 12 75(21} 2305180Л8 24 с присоединением заявки ¹ (23} Приоритет (51) М. Кл.

СР 11 С 29/00

Государотоаннмй ноинтет

Совета Мнннстроо СССР по данам нзобретвннй и открытнй (4З} Опубликовано 25.06,78Âþëë òåíü № 23 (53) УДК 681.327 (088.8) (45) Дата опубликования опнсаяияоу.ое. го о

E. И. Белов, Г. П. Воронин, Р. К. Исламов и Г. А. Попунаев (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКИ)В

ПОСТОЯННОЙ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля блоков постоянной памяти, содержащее регистр со счетным входом, узел установки контрольной суммы и схему сравнения (1). Контроль информации с помощью такого устройства осуществляется путем сравнения суммы всех содержащихся в устройстве чисел по модулю два с заранее подсчитанной константой.

Недостатком этого устройства является низа кая точность контроля и.сложность определения адреса ошибки.

Из известных устройств наиболее близким йо техническому решению к предлагаемому является устройство для контроля блоков пос- Л гоянной памяти, содержащее регистр адреса, подключенный через дешифратор адреса к вы. ходу устройства, вход которого через регистр числа соединен с сумматором, подключенным к блоку управления (2f Это устройство автоматически контролирует блоки постоянной памяти по модулю три и .циклической сумме, образуемой путем суммирования всех содержащихся в блоке памяти чесел с переносом единицы .переполнения из старшего разряда

i младший.

Недостатками этого устройства являются пропуск некоторого вида ошибок (неправильное распределение информации по адресам, перестановка частей информации местами, взанмокомпенсирующиеся ошибки) и снижение точности контроля при отсутствии в числах контрольных кодов по модулю три.

Цель изобретения — повышение точности контроля.

Поставленная цель достигается тем, что устройство для контроля блоков постоянной памяти содержит блок задания циклов суммирования, входы которого подключены соответственно к выходам регистра адреса и блока управления, а выходы — к входам сум.матора н блока управления.

Это позволяет считывать числа из блока постоянной памяти несколько раз, образуя каждый раз новую контрольную сумму, и сравни.вать полученные суммы с контрольными константами и.

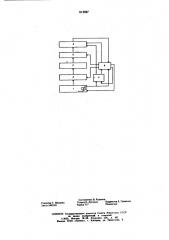

На чертеже изображена структурная схема устройства.

Устройство содержит трнггерный регистр адреса 1, дешифратор адреса 2, подключаемый к проверяемому блоку постоянной памяти 3, числовой регистр 4, сумматор 5, блок управления 6 н блок 7 задания циклов суммирования 7, входы которого подключены соответственно к выходам регистра адреса 1 н блока управления 6, а выходы — к входам сумматора 5 н блока управления 6.

Проверяемый блок постоянной памяти 3, кроме контролируемых чисел,. дополнительно содержит контрольные константы, с помощью которых осуществляется контроль.

Коистанта ми являются либо циклические ммы, либо суммы по модулю два. оличество контрольных констант зависит объема 6J!oKB постоянной HBMHtH

Ог возможного количества и своеобразия

0111800K вызванных Особенностями KoHctpYKцмн н технологии иэГОТОВлеиия блОка. Иапрнмер, первая контрольная константа является циклической суммой всех чисел. Вторая контрольная константа является циклической суммой чисел, полученных путем циклического сдвига в одну сторону каждого последующего числа, считанного с блока постоянной памяти относительно предыдущего на п, разрядов. Третья контрольная константа является циклической суммОй чисел, полученных путем циклического сдвига в одну сторону каждого последующего считанного числа отйоснтельно предыдущего иа п разрядов и т, д, Сумматор 5 предназначен для получения циклических контрольных сумм илн сумм по модулю два.

Для получения второй, третьей и т. д. контрольных сумм сумматор 5 имеет це- зО пи циклического сдвига, которые управляются блоком 7 задЪния циклов суммирования. Сумматор 5 имеет индикацию, что позволяет нроиэ водить контроль блока постоянной памяти Э при отсутствии в последнем контрольных констант. Блок 7 задания циклов 3 суммирования предназначен для организации второго, третьего и последующих циклов суммирования, при которых вырабатываются импульсы циклического сдвига содержимого сумматора 5 на и> разрядов прн втором суммировании, на п разрядов прн третьем суммировании н т. д. Блок управления 6 предназначен для выработки необходимых управляющих сигналов, для Органиэации работы устрой".тва контроля и имеет органы управления для переключения режимами работы. 45

Устройство в автоматическом режиме работает следующим образом.

Под воздействием управляющих чмпульсов блока управления 6 регистр адреса 1 вырабатывает последовательные адреса, У про веряемого блока постоянной памяти 3 последовательно по выработанным адресам считываются на числовой регистр 4 числа, Затем каждое число засылается в сумматор 5. Импульсы циклического сдвига ирн первом суммировании не вырабатываются. После суммирования всех чисел сигнал переполнения с выхода триггера 8 старшего разряда адресного регистра 1 поступает на вход блока 7 задания циклов суммирования н блок управления 6.

Один выход блока 7 дает раэре1пение на прохождение сигналов сдвига сумматора 5, вырабатываемых блоком управления 6 при последующих циклах суммирования, а другой выход блока 7 определяет количество вырабатываемых блоком управления 6 импульсов сдвига в зависимости от номера цикла суммирования. Блок управления по сигналу переполнения вырабатывает сигналы, которые сравнивают результат суммирования с соответствующей контрольной константой. При положительных результатах контроля блок управления 6 вырабатывает сигналы для образования вто рой контрольной суммы, но при этом перед каждой засылкой числа в сумматор 5 содержимое последнего циклически сдвигается в одту и ту же сторону на и, разрядов, определяемых выходом блОка 7 задания циклОв суммирования, в следующем цикле суммирования содержимое сумматора сдвигается на п2 разрядов и т. д. В конце каждого цикла полученные суммы сравниваются с константами.

При отрицательных результатах сравнения вырабатывается сигнал «Останов». После записи оператором отличий полученной неправильной суммы от константы проверка продолжается вплоть до полного завершения всех проверок. После завершения последнего цикла суммирования блок 7 задании циклов суммирования через блок управления 6 вырабатывает сигнал «Останов», при этом, если все полученные суммы совпали с константамн, блок управления 5 вырабатывает сигнал «Исправно».

Так как каждому числу ставится в соответствие определенная константа сдвига, которая зависит от адреса числа, то ошибки, проявляющиеся и неправильном распределении информации по адресам, будут обнаружсны. Обнаруживается так же большинство ошибок, взаимокомпенсируюй;ихся при обычном циклическом суммировании.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее регистр адреса, подключенный через дешифратор адреса к выходу устройства, вход которого через регистр числа соединен с сумматором, подключенным к блоку управления, отличающееся тем, что, с целью повышения точности контроля, оио содержит блок задания циклов суммирования, входы которого подключены соответственно к выходам регистра .адреса и блока управления, а выходы — к входам сумматора и блока управления, Источники информации, принятые во внимание при экспертизе:

Авторское свидетельство № 235108, М.кл. G 11 С 29/00 1967.

2. Информационный листок М JOAN — 73

Ульяновского ЦНТИ.

612287

Сюставнтель 6. Рудаков

Техред Q. Луговая Корректор А. Грнненко

Тнраж 717 Подннсное

Редактор Т. Иванова

Заказ 34б7145

1хНИИПИ Государственного коммтета Совета Мкнмстров СССР ко дедам изобретений н откр ыгнй

113О36. Москва, Ж--3о, Рауыскан наб., д. <5

Фалинем ППП кПатент», г.. Ужгород, уа. Проектная, 4