Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (и1 613401

Cosa Соеетвких

Социалистических

Республик

1 (61) Дополнительное к авт. свид-ву (22) Заявлено 07.07.76 (21) 2379679/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.06.78. Бюллетень № 24 (45) Дата опубликования описания 13.06.78 (51) М. Кл 2 G 11C 11/00

Государственный комите;

Совета АФннистров СССР ло делам изобретений и открытий (53) УДК 681.327(088.8) (72) Авторы изобретения

В. Ф. Гусев, Г. Н. Иванов, В. Я. Контарев, Г. И. Кренгель, В. Я. Кремлев, М. 3. Шагивалеев, Ю. И. Щетинин и А. У. Ярмухаметов (71) Заявитель (54) ЗАПОМИ НАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство, содержащее два блока памяти — для адресной и операционной информации, два регистра адреса, дешифратор адреса, регистр команды, схему задержки, элементы И вЂ” НЕ (1).

Недостатком этого устройства является большое количество оборудования и возможность выбора следующего адреса только по коду команды.

Наиболее близкое техническое решение к изобретению — запоминающее устройство, содержащее блок памяти, выход которого подключен к входу первого регистра, первые и вторые выходы которого соединены соответственно с -входами второго регистра и дешифратора, блок задания команд, подключенный к первому входу устройства (21.

В этом устройстве для формирования адреса следующей команды используются 24 разряда слова микрокоманды из 90 (т. е.

26,7 ), что является существенным недостатком устройства, снижая его эффективную емкость. Кроме того, для устройства характерны невысокое быстродействие и недостаточные функциональные возможности из-за малой гибкости ветвлений, например при переходе по коду операции вставление осу цествляется в два приема.

Цель изобретения — повышение быстродействия и увеличение эффективной емкости устройства.

Поставленная цель достигается тем, что

5 устройство содержит коммутаторы, элементы

И вЂ” HE, шифратор и блок анализа, входы которого подключены соответственно к выходу дешифратора и второму. входу устройства, а выходы — к одним входам элементов И—

10 НЕ, другие входы которых соединены с третьими выходами первого регистра. Входы коммутаторов подключены соответственно к выходам элементов И вЂ” НЕ, четвертым выходам первого регистра, выходом второго ре15 гистра, шифратора и блока задания команд, третьему и четвертому входам устройства.

Выходы коммутаторов соединены с адресными входами блока памяти, пятый и шестой входы устройства подключены к входам шиф20 р атор а.

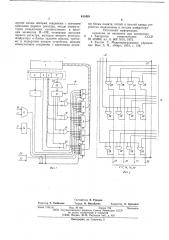

На фиг. 1 показана электрическая схема предложенного устройства; на фиг. 2 — схема блока анализа.

Устройство содержит блок 1 памяти, пер25 вый регистр 2, состоящий из поля 3 констант, поля 4 следующего адреса, поля 5 признаков и поля 6 анализов, второй регистр 7, коммутаторы 8 — 12, шифратор 13, блок 14 задания команд, первый 15, второй 16 входы устройства, элементы И вЂ” НЕ 17 — 20, блок 21 ана6 I 340I

3 лиза, дешифратор 22, имеющий вход 23, третий 24, четвертый 25, пятый 26 и шестой 27 входы устройства.

Входы олока 21 подключены соответственно к выходу дешифратора 22 и входу 16 устройства, а его выходы — к одним из входов элементов Й вЂ” НЕ 17 — 20. Первые, вторые и третьи выходы регистра 2 соединены соответственно с входами регистра 7 и дешифратора 22 и другими входами элементов И—

HE 17 — 20, Входы коммутаторов 8 — 12 подключены соответственно к выходам элементов И вЂ” НЕ 17 — 20, четвертым выходам регистра 2, выходам регистра 7, шифратора 13 и блока 14, входам 24 и 25 устройства. Выходы коммутаторов 8 — 12 соединены с адресными входами блока 1 памяти, входы 26 и 27 устройства подключены к входам шифратора

13.

Блок 21 анализа (фиг. 2) содержит эле- менты И вЂ” НЕ 28, первые входы которых соединены с выходами дешифратора 22, другие . входы подключены к входу 16 устройства, а выходы соединены с шинами анализов

29 — 32. Каждая из шин анализов подключена к одному из входов элементов И вЂ” НЕ

17 — 20 соответственно.

Устройство работает следующим образом.

Информация считывается из блока 1 памяти на регистр 2. Часть разрядов регистра

2 отведена под задание адреса следующей ячейки блока 1 памяти (поле 4 следующего адреса) . Адрес следующей ячейки памяти поступает на коммутаторы 8 — 12 и через них на адресные входы блока памяти. Следующая ячейка блока памяти будет выбрана по адресу, заданному в предыдущей ячейке. Таким образом осуществляется выборка микропрограммы при использовании данного запоминающего устройства для микропрограммного управления.

Задание начального адреса последовательности ячеек может быть осуществлено с нескольких направлений. При нажатии кнопки на пульте (на фиг. 1 и 2 не показан) сигнал через вход 26 поступает на шифратор 13. Последний вырабатывает адрес начала микропрограммы, который через коммутаторы 8—

12 поступает на адресные входы блока памяти. Начинает выбираться последовательность ячеек, выполняющих заданное с пульта действие (пультовую микропрограмму) .

Если устройство выполняет команды системы команд, то начальный адрес последовательности ячеек определяет код команды.

При работе устройства код команды загружается по входу 15 на блок 14. По завершении предыдущей команды по сигналу из блока 14 начальный адрес микропрограммы данной команды, который может быть численно равен коду команды, подается через коммутаторы 8 — 12 на адресные входы блока 1 памяти. Начинает выбираться последовательность ячеек, определяющая действия для выполнения данной команды.

55 б0 б5

Последовательность выборки ячеек может быть изменена для прерывания действий по выполнению команд.

Возникает необходимость срочно прервать нормальное течение микропрограммы при различных программных ошибках, таких, как нарушение защиты памяти, обращение по несуществующему адресу, неверное задание адресов команд и т. д. Сигнал прерывания по входу 27 поступает на шифратор 13. Последний в зависимости от характера прерывания вырабатывает тот или иной адрес, который определяет микропрограмму обработки соответствующей ситуации. Адрес передается на коммутаторы 8 — 12 и по сигналу из шифратора 13, поступающему на входы коммутаторов 8 — 12, он принимается на блок 1 памяти. При этом поступление прочих адресов через коммутаторы блокируется.

При необходимости вызвать какую-либо ячейку блока памяти вручную с пульта управления ее адрес, набранный на клавиатуре пульта, к входу 24 подается одновременно с управляющим сигналом на коммутаторы 8—

l2. Нужная ячейка вызывается из блока памяти.

Другой вход 25 устройства служит для управления работой запоминающего устройства извне, например от другого запоминающего устройства. -Для диагностики неисправностей другое запоминающее устройство подает через вход 25 устройства адреса микрокоманд для активизации тех или иных цепей объекта управления.

Последовательность ячеек блока памяти может представлять собой какую-либо подпрограмму, к которой обращается ряд программ. При этом вход в данную подпрограмму определяется адресом ее начала и может быть указан в программе, а адрес выхода из подпрограммы в каждом конкретном случае разный и определяется видом программы.

Следовательно при входе в подпрограмму необходимо заранее задать адрес выхода.

В устройстве возврат осуществляется следующим образом: перед входом в подпрограмму на регистр 7 с регистра 2, а именно с части его разрядов, называемых полем 3 констант, загружается адрес возврата. Каждая подпрограмма в последней своей ячейке содержит приказ приема адреса с регистра

7. Адрес с регистра 7 через коммутаторы 8—

12 поступает на блок памяти для продолжения программы. Адрес перехода может быть использован вместе с аппаратурой ветвления, которая описана ниже.

При выполнении какой-либо микропрограммы часто возникает необходимость произвести ветвление в зависимости от выполнения или невыполнения ряда условий. При этом может быть ветвление на 2, 4, 8 и т. д. направлений. В каждом конкретном случае проверяется свой набор условий. И хотя число таких проверок достаточно велико и усло613401 (2) 10

20

5 вия разнообразны, набор условий, проверяемых одновременно, ограничен.

При выполнении ветвлений устройство работает следующим образом: так называемый базовый адрес задается из регистра 2 полем

4 следующего адреса и поступает на все коммутаторы 8 — 12, Номер проверяемого набора условий задается частью разрядов регистра 2 (полем 6 анализов) и дешифрируется на дешифраторе 22. Все возможные проверяемые условия по входу 16 подключены к блоку 21. (Работа блока поясняется фиг. 2). По сигналу дешифратора 22 возбуждается одна из линеек элементов И вЂ” НЕ 28, соответствующая номеру анализа. На другие входы указанных элементов подаются проверяемые условия.

На выходах элементов И вЂ” НЕ 28 оказывается логический «О» или «1» в зависимости от выполнения или невыполнения проверяемого условия. На шины 29 — 32 анализа принимается код, соответствующий состоянию проверяемых условий на момент анализа.

Таким образом, на шинах 29 — 32 анализа возможно 2 комбинаций, где и — число шин анализа. В линейку объединяются те условия, проверка которых необходима в один момент времени. Данное условие может быть подключено и к другой линейке, т. е. проверка его может быть объединена с другими условиями. Количество комбинаций, проверяемых блоком анализов, может быть

К=2" и (1) где m — число кодов поля 6 анализов регистра 2.

Код с шин анализов блока 21 через элементы И вЂ” НЕ 17 — 20 поступает на коммутаторы 8 — 12 и подменяет часть разрядов базового адреса, подаваемого по другим входам коммутаторов, например младшие. Через коммутатор 12 проходят на вход блока 1 неизменяемые разряды адреса, например старшие. Таким образом осуществляется ветвление на 2 направлений в пределах

«страницы» блока 1 памяти (группы разрядов, адресуемой неизменной частью адреса).

Однако ветвление каждый раз на 2" направлений неудобно и требует большого количества ячеек памяти, поэтому количество направлений ветвления может быть ограничено с помощью других разрядов регистра 2 (полем 5 признаков), Наличие единицы в разряде поля 5 признаков разрешает через элементы И вЂ” HE 17, 18, 19 или 20 подключение в качестве разряда следующего адреса одного из выходов блока 21. Отсутствие признака в соответствующем разряде блокирует прием адреса с блока 21 и разрешает поступление в этом разряде базового адреса с другого выхода регистра 2. При одной единице в поле 5 признаков разрешается ветвление на два направления, при двух единицах — на четыре и т. д, Таким образом, использование одного сигпала анализа (возбуждение одной линейки элементов И вЂ” HE

28 блока 21) в сочетании с признаками позволяет выполнять 2" — 1 видов проверок (нулевой код признака — отсутствие анализа) .

При количестве анализов, равном m, количество проверок

К= т(2" — 1).

При этом сохраняется удобство задания проверки, экономно используются ячейки блока памяти, а количество связей и элементов И вЂ” HE достаточно мало.

Поскольку выр аботка адреса следующей ячейки осуществляется одновременно с нескольких направлений, то коммутаторы 8 — 12 являются также и приоритетными схемами.

На выходе пх может быть только один адрес, отвечающий коду, подаваемому с самого приоритетного на данный момент направления. Адрес с пульта управления имеет наивысший приоритет-оператор может вмешиваться в любое время. Адрес из диагностики по входу 24 блокирует все прочие направления.

Адрес шифратора 13 запрещает прием адреса с регистра 2, так как передает управлеННс на более приоритетные программы. И, наконец, наличие признака ветвления запрещает прием соответствующего разряда адреса с регистра 2 или с регистра 7.

Предлагаемое устройство повышает функциональные возможности устройства, сокращает оборудование для ветвлений, экономит ячейки блока памяти и сокращает их разрядность по сравнению с известным, где для ветвления используются 24 разряда регистра информации. Для задания 896 видов проверок в предлагаемом устройстве затрагиваются 10 разрядов. Таким образом, достигается сокращение разрядности в 2,4 раза.

Значительно повышается функциональная возможность устройства, появляется возможность выбирать ячейки памяти, используя в качестве источников адреса различные блоки устройства, причем выборка производится с наиболее приоритетного направления. Значительно экономятся ячейки памяти за счет задания оптимального для каждого случая количества ветвлений, т. е. повышается эффективная смкость устройства.

Формула изобретения

Запоминающес устройство, содержащее блок памяти, выход которого подключен к входу первого регистра, первые и вторые выходы которого соединены соответственно с входами второго регистра и дешифратора, блок задания команд, подключенный к первому входу устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и увеличения эффективной емкости устройства, оно содержит коммутаторы, элементы

И вЂ” HE, шифратор и блок анализа, входы которого подключены соответственно к выходу дешифратора и второму входу устройства, а выходы — к одним входам элементов И вЂ” HE, 613401

ff/7, 18 /У рО

Риг, z

Pue. /

Составитель В. Рудаков

Техред И. Михайлова Корректор Л. Брахнина

Редактор T. Рыбалова

Заказ 1131/18 Изд. № 495 Тираж 734

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Я-35, Раушская наб., д. 4/5

Подписное

Типография, пр. Сапунова, 2 другие входы которых соединены с третьими выходами первого регистра, входы коммутаторов подключены соответственно к выходам элементов И вЂ” НЕ, четвертым выходам первого регистра, выходам второго регистра, шифратора и блока задания команд, третьему и четвертому входам устройства, выходы коммутаторов соединены с адресными входа8 ми блока памяти, пятый и шестой входы. устройства подключены к входам шифратора.

Источники информации, принятые во внимание при экспертизе

5 1. Авторское свидетельство СССР № 419893, кл. G 06F 9/16, 1972.

2. Хассон С. Микропрограммное управление. Вып. 2,, М., «Мир», 1974, с. 179.