Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

1

ОПИСКЖЙЕ

Союз Советских

Социалистических

Республик

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к аат. саид-ву(22) Заявлено 1 2.02.74 (21) 1995480/18-09 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано05.07.78Бюллетень №25 (51) М. Ил.

Н 03 5 3/45

Госудерстеенный кеинтет

Соеетв Мхннстроа СССР не делам нзабретеннй н етнрытнй! (53) УДК 621, Э 75,4..087.9.083,6 (O8e. ) (45) Дата опубликования описаиня05.06,78

В.- И. Анисимов, М. В. Капитонов и H. Н. Прокопенко (71) Заявитель Ленинградский ордена Ленина электротехнический инстит; —. им. В. И, Ульянова (Ленина) (54) ПИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ

Изобретение относится к радиотехнике и может использоваться в устройствах автоматики, телемеханики и вычислительной техНИКИ.

Известен дифференциальный усилитель, содержаший последовательно соединенные входной дифференциальный каскад с генератором тока в обшей эмиттерной пепи, каждое плечо которого выполнено в виде последовательно соединенных по постоянному току 1@ входного и выходного транзисторов, и.выход,ной дифференциальный каскад с последовательно включенными делителем постоянного напряжения, отвод которого подключен к ба-зам выходных транзисторов входного диф- 15 ференциального каскада, и генератором тока в обшей эмиттерной цепи 1 (.

Однако в этом усилителе коэффициент подавления синфазных сигналов мал.

Бель изобретения - увеличение коэффи- щ циента подавления синфазных сигналов.

Для этого в дифференциальный усилитель, содержаший последовательно соединензтые входной дифференциальный каскад с генератором тока в обшей эмиттерной цепи, кажДОЕ ПЛЕЧО KOTOPOIÎ ВЫ ПОЛЦBIIO F ППДЕ ПО, Л довательно соединенных по постоя1п.,ому то"ку входного н выходного транзисторов, к выходной диффэретшиальный каскад с пэслэ-довательнО включенными делтп елем постоя ".=: ного напряжения, отвод которого подключен к базам выходных транзисторсв входного дифференциального каскада, н генератором тока в обшей эмиттерной цепи, параллельно делителю постоянного напряжения включен транзистор, база которого подключена к Об-. шей эмиттерной цепи входного дифференциального каскада.

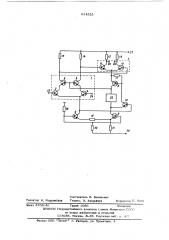

HG чертеже представлена электрическая схеМе дифференциального усилителя (ДУ) .

Усилитель содержит последовательно соединенные входной диф еренциапьньrA каскад

1 с генератором 2 тока в Обшей эмиттерной цепи, каждое плечо которо-о выполнено в виде последовательно соединенньrx по псстоянному току входного и выходного транзисторов 3,4 и 5,6, и выходной дяфЬ.ренциальный каскад 7 с пагледовате;и но включенными делителем 8 постоянного на= пряжения, отвод которого подключен к ба614525 эам выходных транзисторов,5,6 входного дифференциального каскада, и генератором

8 тока в общей эмиттерной цепи, делитель

8 посгоянного напряжения, параллельно которому подключен транзистор 10, база которого подключена к общей эмиттерной це- пи входного дифференциального каскада 1, а выходной дифференциальный каскад 7 выполнен на транзисторах 11,12 кроме того резисторы 13-21, двухполюсник 22, входы

23,24 и выходы 25,26 усилителя, к которым подключается нагрузка НУ, клеммы 27,28 ис точникв питания.

Устройство работает следующим образом.

Положительный синфвзный сигнал с напри — 1g жением Ц,й, поступающий нв входы 23, 24 ДУ, прикладывается не только к коллекторно-базовым. переходам транзисторов 5,6, 1 но и коллекторно-бвэовым переходам транэисторрв 3,4 (что становится возможным щ благодаря введению транзистора 10). Если сопротивлени s й, резисторов 20, 19 равны, то приращения напряжения коллектор-база транзисторов 5,6 Ц, и транэис горов ив„b

3,4 h U равйы половине Я . Из 25 этого следует, что при иденгичных режимах транзисторов 5,6 сравниваемых усилителей (U< + 1 к к ) насыщение данньцс активных элементов не наступит до тех, пор, пока Ц с с. 20,к ги к а введение

30 транзис гора 10 расширяет диапазон синфаэ ных сигналов в два раза.

Введение транзистора 10 в схему ДУ улучшает коэффициент подавления синфазных сигналов К с, если авухполюсник 22— стабилитрон. Коэффициент подавления входных синфаэных напряжений определяется форму лой

1 2 ) 4 ЭР (1) 40 где pl 4 — коэффициент передачи синфаэного напряжения со входа ДУ нв обьединение бт зы транзисторов 3,4..

В иь

И +И

П5 2 щ +д Э 22 4 22 У ! Ve (+g "«««"«1т

Э 4

„- ",+4mb

K3 ° % (Мз«22 Ч4И )1

З 4

- выходная tlpoaol1HMocTb генератора тока в эмиттерной цепи транзисторов 5,6,.

4i j NQ - параметры транзисторов 3-6 в схеме с общей базой.

Ko ÔÔHHHa /i/4 принимает два аНачения jO 4 "- 1, если двухполюсник 22 — ств билитрон, и /Ц = 0,5, если данный двухполюсник-резистор.

Формула (1) позволяет сравнить извест ный и предлагаемый усилители по 1(Анализ формулы показывает, что НрН р 1 иэ суммы (1) исключаются наиболее весовые слагаемые, определякхпие подавление сннфазных сигналов ДУ. Последнее обьяоняется тем что разброс параметров внутренней обратной связи транзисторов 5,6 оказывает доминирующее влияние на К каскадных ДУ н р, «й„;и„,« о но .

Как. следствие при 7 в О введение транзистора 10 и двухполюсника 22 стабилитрона улучшает К ос в Д раэ, причем

КЭ

Д= — a 10-:50 .

К

Для биполярных транзисторов коэффициент лежит в пределах 10-50.

Формула изобретения

Дифференциальный усилитель, содержащий последовательно соединенные входной дифференциальный каскад с генератором тока в. обшей эмиттерной цепи, каждое плечо которого выполнено в виде последовательно соединенных по постоянному току входного и выходного транзисторов, и выходной дифференциальный каскад с последовательно включенными делителем постоянного напряжения, отвод которого подключен к базам выходных транзисторов входного дифференциальног каскада, и генератором тока в общей эмиттерной цепи, отл ичв ющ ий с я тем, что, с целью увеличения коэффициента подавления синфаэных сигналов, параллельно делителю постоянного, напряжения включен транзистор, база которого подключена к обшей эмиттерной цепи входного дифференциального каскада.

Источники информации, принятые во внимание при экспертизе:

1. Патент США Л" 3541465, кл. 33030, 1 970.