Устройство для умножения

Иллюстрации

Показать всеРеферат

Союз Соввтекнх

Соцнапнстнчвоснх

Реяпублнк

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ (i1) 615476

И АВТОРСКОМУ СВИДВТИЛЬСТВУ (61) Дополнительное к авт. свил-ву(22) Заявлено 20.01.76 (21)2317242/18-24 с присоединением заявки ¹ (23) Приоритет (43} Опубликованс 15.07.78.Бюллетень № 26 (45) Дата опубликования описаний16.06.78

2 (51) М. Кл. Я 06 F 7/39

Государственный «он«тот

Сооотв Министров СССР оо делам нзоорвтвний н открытий (53) УДК 681.325 (088,18) (72) Авторы изобретения

Л. Я. Лапкин и И. Т, Абрамсон (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

Изобретение относится к области вычиолитепьной техники, в частности к пифровым множительным устройствам.

Известны устройства для умножения с промежуточным преобразованием кодов сомножителей в последоватепьности импупьсов. Например, множитепьное устройство (1 содержит регистры, операндов > младшие разряды которых через блоки схем

И соединены с первыми входами схемы сравнения, вторые входы которой соединены с датчиком случайных чисел.

Выходы схемы с, авнения соединены с. логическим устройством умножения, вы- . ходы которого соединены с регистром результата.

Недостатками указанного устройства являются наличие в нем сложного функционального узла - датчика случайных чисел и низкое быстродействие.Наиболее близким техническим решением к изобретению является устройство для умножения, содержашее первый и второй и разрядные регистры, блок сравнениями блок умножении, эпементы И, блок элементов ИЛИ, первый и второй счетчики, первый(сумматор. Прячем входная шина устройства соединена с входом первого счетчика, первая группа выходов которого соединена с первыми входамиэпементов H. Вторые входы эпементов И соединены с выходами 5- к(к*йфчладших разрядов первого регистра, а выходы элементов,И - е входами бпока эпементов

ИЛИ. Вторая группа (выходов первого счетчика соединена с первыми входами блока сравнения, вторые входы которого подключены к выходам во-К мпадшйх раа- . рядов второго, регистра. Выход блоха умножения соединен с входом первого суммматора, выход которого соединен с входом второго счетчика, выходы первого сум матора и второго счетчика соединены с . выходными шинами устройства f2).

Недостаток устройства - низкое быотродейств ие.

Белью изобретения явпяется повыщение быстродействия.

615476

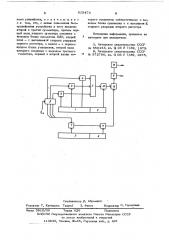

Это достига@тся тем., что в устройство введены второй и третий суммато(; ры, Причем первый вход второго сумматора соединен с выходом блока элементов ИЛИ, второй вход — с выходами к, старших разрядов первого регистра, 5 а выход - с первым входом блока умно жения. Второй вход последнего соединен с выходом третьего сумматора, первый и второй входы которого соединены соответственно с выходом блока сравнения и с вы 10 ходами g старших; разрядов второго регистра.

Блок-схема устройства представлена на чертеже.

Устройство содержит регистр с группой 0- к младших разрядов 1 и группой К старших разрядов 2, блок 3 элементов ИЛИ, элементы И 4, регистр с группой (n- К) младших разрядов 5 и группой К старших разрядов 6, блок сравнения 7, счетчик 8, сумматоры 9, 10 и 11, логический блок умножения

12, счетчик результатов 13.

Устройство работает следующим образом.

Время вычислений определяется пики-н пом,работы счетчика 8 и равно 2

После одного цикла работы счетчик 8 останавливается и в сумматоре 9 и счетчике 13 фиксируется результат умиоже30 ния.

У падшие П-К РазРЯДы сомножителей

p,è pA преобразуютси в число импульсов и временной интервал, соответствую

35 шие преобразуемым младшим разрядам сомножителей N» и М . При поступлении нулевого сигнала с выхода блока 3 элементов ИЛИ с выхода сумматора 10 снимается код М» О старших К разря2 »о дов 2 первого регистра. При поступлении нулевого сигнала с выхода бпока 3 с выхода сумматора 10 снимается код

М +.(. Таким образом, за 2" такта работы устройства число М поступает на и-к - 45 первый вход блока 12 умножения 2 -К раз, а число М-+(-зараз.

С выхода сумматора 11 во время наличия на его первом входе временного интервала длительности М»/f „, что со50 ответствуете»тактам входной частоты, снимается код М +4 N и М коды старших разрядов первого и второго сомножителей, .хранящихся в частях

2 и 6 регистров. Во время отсутствии

55 на входе сумматора 11 этого временно(г-К го интервала, что соответствует 2 - hA тактсм частоты 1 „, с его выхода снимается код М,г»0. Таким образом. за рой вход блока 12 умножении число М поступает 2п "-М раз, а число hh:<+ 3 -ht(< раз.

После перемножения в блоке 12 с его выхода снимается код Мя N> /2" " число раз, равное(Я -К„)(2" " -N„), êîä число раз, рав2 и-к ное(Я" "- й,) М», код М (.N + <)> число раз, равное Й„ 2" "- м, код (рА»..()(+ )2" " — число раз равное l4» М» . Эти коды суммируют

cs накапливающим сумматором 9 и счетчиком 13. Их сумма г- (РггN,(z" -гг,)(г" - )+(+ö . и-й (-N,)h,+Ì,(И,+1)У (2" -р )+

+(ггг г)(м, г)(м,гг,)) „

После упрощения

1И +М 2 )(Т + 1г 2 ) и-k что является результатом перемножения сомножителей

У=И+3r 2 И pj=p1 +pf гй кг н-h

1 2 1 2

Время выполнении операции умноже2 гг-к сия равно . Предложенное устрой» т. и ство целесообразно использовать при

Х << и, так как при атом получают существенное повышение производительности практически без увеличения аппаратурных затрат.

Формула изобретения

Устройство для умножения, содержащее первый и второй tl- разрядные регистры, блок сравнения, блок умножения, эпементы И, бнок апементов ИЛИ, первый и второй счетчики, первый сумматор, причем. входная шина устройства соединена с входом первого счетчика, первая группа выходов которого соединена с первыми входами алементов И, вторые входы которых подключены к Выходам, .и -к (к 1 д, ) младших разрядов первого регистра, а выходы апементов И соединены с входами блока элементов ИЛИ, вторая группа выходов первого, счетчика соединена с первыми входами блоха сравнения, вторые входы которого подключены к выхо дам ггк младших разрядов второго регистра, выход блока умножения соединен с входом первого сумматора, выход кото рого соединен с входом второго счетчика BBJxolIbl первого счмматопа и втово615476

Сост авитепь,И. Абрамсон

Редактор Т. Юрчикова Техред . 3. Фанта Корректор С» Гарасиняк

Заказ 3910/38 Тираж 826 Подписное

Ш ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаи наб., д 4/5 нами уотройства, о т и и ч аю ше ес я тем, что, с целью повышенин быотродействия устройства в него введены второй и третий сумматоры, причем пер вый вход второго суматора соединен с выходом блока элементов ИЛИ, второй вход - с,выходами Мс старших разрядов первого регистра, а выход - с первым входом блока умножения, второй вход которого соединен с выходом третьего тмматора, первый и второй входы которого соединены соответственно с выходом бпока сравнения и .с выходами С старших разрядов второго регистра

Источники информации, принятые во внимание при экспертизе;,1. Авторское свидетельство СССР

p@ 556433, кп. Я 06 Р 7/39, 1972, 2. Авторское свидетельство СССР

¹ 572786, кл. G 06 F 7/39, 1975,