Устройство для реализации быстрого преобразования фурье

Иллюстрации

Показать всеРеферат

)О !

5 !

3 615 ны соответственно с первым и вторым тактовыми входами устройства .

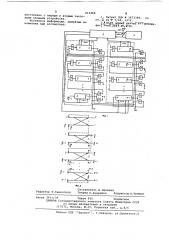

На фиг. 1 представлена блок-схема предлагаемого устройствами на фиг.2алгоритм БПФ, реализуемый устройствам.

Устройство включает блок памяти 1, состоящий из М регистров 2 сдвига, арифметический блок 3, блок 4 памяти коэффициентов, первые элементы

И 5, вторые элементы И 6, элементы

ИЛИ 7 °

Регистры сдвига 2 для общего случая М -точечного преобразования

Фурье делятся на две группы, по Н/2 в каждой группе. Два регистра 2 одной строки соответствуют графу одного двухточечного БПФ алгоритма, изображенного на фиг. 2, и их нумерация соответствует нумерации горизонталей этого алгоритма.

Регистры каждой группы соединены последовательно для передачи информации снизу вверх в арифметический блок 3 через элементы И 5, управляемые серией тактовых импульсов ТИ 1.

Параллельные выходы верхней пары регистров (О и Я/2) подключены к арифметическому блоку 3, а выходы арифметического блока 3 — к параллельным входам регистров с номерами(я/2-1) и (g — 1)..

Элементы И б соединяют регистры обеих групп для переупорядочивания информации в соответствии с алгоритмом фиг. 2. При этом последователь- ный выход регистра с номером через соответствующие логические элементы

И б и ИЛИ 7 соединен с последовательным входом регистра с номером )у двоичный код которого образуется путем циклического сдвига на один разряд влево двоичного кода 4. Элементы И б управляются серией тактовых импульсов ТИ2. Для объединения выходов элементов И 5 и б служат элементы ИЛИ 7.

Для работы устройства следует хранить н блоке 4 и поданать в арифметическое устройство h /2 пар коэффициентов вида

2йк ° 21к / Я сов и о и к=1,2 " ° — °

И и

Перед началом работы выборки исходного сигнала размещаются в регистрах 2 устройства в соответствии со своими номерами..

Функционирование схемы осуществляется под воздействием двух серий упранляющих импульсов. Первая серия (ТИ1) включаетй/2 групп импульсов, по П в каждой группе. Под воздействием перной группы из И импульсов осуществляется сдниг вверх на одну ступень всех выборок сигнала, размещенных н регистрах, и передача в арифметический блок 3 первой пары выборок сигнала. В то же время в арифметический блок З.поступает первая пара коэффициентов, и в нем осуществля: ется первое днухточечное БПФ, результаты которого заносятся в регистры (N/2-1) и (Н -1) цо их параллельном входам.

ЗаN/2 подобных циклов завершается первая итерация БПФ над всеми выборками сигнала, после чего в схему поступает вторая серия из ((импульсов ТИ2 для переупорядочинания информации в регистрах устройства в соответствии с алгоритмом БПФ (пунктирные линии на фиг. 2).

Итерации повторяются2оф и раз.

В результате в регистрах устройства оказываются коэффициенты, Фурье исходной последовательности выборок сигнала.

Таким образом, применение модифицированного алгоритма БПФ, введение в устройство 3ъ коммутирующих элемен.тов, каждый из которых реализован на днух элементах И и одном элементе ИЛИ, и грименение жестких связей между регистрами устройства выгодно отличает предложенное устройство от прототипа, так как число регистров памяти уменьшается вдвое, что сокращает объем используемого оборудования.

Формула изобретения

Устройства для реализации быстрого преобразования Фурье,. содержащее блок памяти, арифметический блок и блок памяти коэффициентов, о т— л и ч а ю щ е е с я тем, что, с целью сокращения оборудования блок памяти состоит из И регистров сдвига, элементов И, ИЛИ, причем параллельные входы (Й/2 -1)-го и (Й -1)-rO регистров сдвига соединены соответ-. ственно с первым и вторым выходом . арифметического блока, а параллелЬные выходы нулевого и К/Z -го ре1.истров сдвига соединены соответствен-. но с первым и вторым входом арифметического блока, третий и четвертый входы которого соединены соотнетстненна с выходами блока памяти коэффициентов, последовательный вход каждого регистра сдвига подключен к выходам соответствующего элемента

ИЛИ, а выход-к первым входам первого и второго соответствующих элементов И, выход первых элементон И каждого регистра сдвига, за исключением нулевого иК/2.-ro регистра сдвига, соединены с первыми входами элементов И предыдущих регистров сдвига, выход второго элемента И

-го регистра сдвига соединен со вторым входом элемента ИЛИ ) -го регистра сдвига, где j -двоичный код, полученный путем циклического сдвига на один разряд влево двоичного

1 кода, вторые входы всех первых и вторых элементов И соединены соот