Устройство для интегрирования частотно-импульсных сигналов

Иллюстрации

Показать всеРеферат

ОПМСАЛЙ

ЙЗОБРЕТЕИЙ

К, АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (63) Дополиительиое к авт. саид-ву— (22) Заявлено 191274 (21) 2086050/24 с присоедииевиеи заявки Ъ

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (23) Йриоритет (43) Опубликовано1М778. Бюллетень ¹ (45) Дата опубликования описания,1906. (72) Автор изобретения

В.B. Чистяков (54) УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ ЧАСТОТНОИИПУЛЬСНЫХ СИГНАЛОВ

Изобретение относится к области автоматики и вычислительной техники., Известны устройства для интегрирования сигналов, содержащие интегрирующий усилитель, сумматор, реверсивные счетчики, цифро-аналоговые преобразователи и инверторы $l.j. В этих устройствах интегрирование входной величины на некотором интервале времени осуществляется с помощью интегрирующего усилителя и сумматора,связанных по входу с реверсивными счетчиками, в которых накапливается результат, через цифро-аналоговые преобразователи. i5

Недостатком указанного интегратора является низкая точность и необходимость введения дополнительного преобразователя для представления выходного сигнала в частотно-импульсной форме.

Прототипом изобретения является частотно-импульсный интегратор, содержащий множительно-делительный блок, соединенный первым входом с входом устройства, счетчик, выходы которого подключены к первым входам элементов И основной группы, и элемент ИЛИ, выход которого соединен с выходом устройства, а также блоки коммутации и формирования производной (21.

Однако это устройство не обеспечивает высокой точности операции интегрирования и имеет низкое быстродействие.

Целью изобретения является устранение указанных недостатков. Поставленная цель достигается тем, что в устройство дополнительно введены счетчик, регистр, триггеры, элементы И и ИЛИ, элементы задержки и частотно-импульсный запоминающий блок, соединенный выходом с вторым входом множительно-делительного блока и подключенный входом к выходу устройства и к первым входам двух элементов И, выход первого из которых подключен через первый элемент задержки к входу первого триггера, соединенного выходом с вторым входом второго элемента И и с входом дополнительного элемента ИЛИ, подключенного вторым входом к выходу второго триггера и к первому входу третьего элемента И, а выход дополнительного элемента ИЛИ соединен с входом четв .ртого элемента И, выход которого подключен к входу основного счетчика, причем выход второго элемента И

615496 соединен с первыми входами третьего, четвертого и пятого триггеров и че. рез второй и третий элементы задерж ки подключен соответственно ко входу обнуления основного счетчика и ко вторым входам элементов И основной группы, выходы которых через регистр соединены с первыми входами элементов И дополнительной группы, вторые входы которых подключены к третьему входу множительно-делительного блока и к выходу дополнительного счетчика, разрядные входы которогО соединены с выходами элементов И дополнительной группы, а счетный вход подключен к выходу пятого элемента И, соединенного первым входом с выходом третьего триггера, а вторым входом— с входом запуска устройства и с первыми входами шестого и .седьмого элементов И, вторые входы которых соединены с входом устройства и со вторым входом третьего элемента И, подключенногб выходом к вторым входам четвертого и пятого триггеров, первые выходы которых соединены соответственно с вторым входом первого и третьим входом шестого элементов И, причем выход шестого элемента И через четвертый элемент задержки подключен к входу второго триггера, а второй выход пятого триггера соединен с третьим входом .пЕрвого эЛемЕнта И, а выход седьмого элемента И, подключенного третьим входом к выходу шестого триггера, соединен с первым входом осноэного элемента ИЛИ, второй вход которого подключен к выходу множительно-делительного блока и эхо» ду шестого триггера.

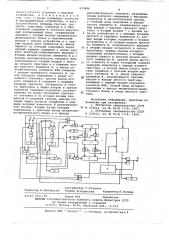

На чертеже представлена функциональная схема устройства для интегрирования частотно-импульсных сигналов. устройство содержит множительноделительный блок l, основной счетчик 2, дополнительный счетчик 3, ре-. гистр 4, частотно-импульсный запоминающий блок 5,. триггеры б-;.11, элементы H 12-,18, группы элементов И:19, 20 элементы ИЛИ 21,22, элементы задержки 23-, 26, клемму 27 подачи вход- ных сйгналов клемму 28 подачи сигна-.:

l ла запуска, клеммы 29,30 подачи сигналов опорных частот, выходную клемму 31.

Устройство работает следующим образом. Входные сигналы с частотойР„ подаются на клемму 27. Сигналы опорных частотРая1 и Роя<подаются соответственно на клеммы 29 и 30. В исходном состоянии счетчики, регистры и триггеры устройства обнулены. В .моментс. на клемму 28 подается сиг1 нал запуска. При этом первый после момента tl иHмMп у л ь с,, подаваемый на клемму 2/, проходит через элемент И12 и через элемент задержки 23 на счетный вход триггера 6, переводя ега иэ нулевого в едмничное состоянив, Очевидно, что ripa этом сигнал не agoходит на выход элемента И 13, так как отпирающий сигнал с триггера б подается на его вход с задержкой за счет элемента задержки 23. С переводом триггера 6 в единичное состояние отпирающий сигнал с его выхода подается на вход элемента И 13 и через элемент ИЛИ 21 — на вход элемента И 16. При этом через элемент И 16 . на вход счетчика 2 начинают цодаэаться сигналы опорной частоты 5 котоояо рые выполняют функцию заполнения пе)3 риода частоты Р®„. При этом заполнение периода входной частоты Р „асущестэля» ется до момента поступлеййя следующего сигнала на клемму 27. При поступлении следующего сигнала на клем20 му 27 этот сигнал проходит на выход элемента И 13, переводя триггер 7 в 1 и через время, определяемое элементом задержки 23, переводит триггер 6 в нулевое состояние. В реэульщ тате прекращения подачи отпирающего напряжения на вход элемента И 16 прекращается подача сигналов опорной частотыР0д1 на вход счетчика 2, и в нем фиксируется информация, соответу стэующая периоду частотыР . ОдновреДМ( менно в результате перевода триггера 7 в. единичное состояние.открывается элемент И 14 для сигналов с выхода интегратора, конкретно с выхода элемента ИЛИ 22, и запирается элемент И 12 для входных сигналов с частотой РВ„.Первые сигналы на выход интегратора проходят с клеммы 27 через элемент И 18 и элемент ИЛИ 22 °

Первый после момента отпирания элемента И 14 сигнал из выходной после-. довательности проходит через элемейт

И 14 и элемент задержки 24 на счетный вход триггера 8, переводя его из нулевого в единичное состояние.

46 В результате отпирающий сигнал с выхода триггера 8 подается на вход элемента И 15 и через элемент ИЛИ 21на вход элемента И 16. При этом через элемент И 16 на вход счетчика 2 й0 начинают подаваться сигналы опорной частотыРряс,которые суммируются с ранее накопленной э счетчике 2 информацией о периоде входного сигнала.

Заполнение периода сигналов выходной

8 последовательности осуществляется до момента поступления следующего сигнала с выхода. Устройства на вход элемента И 14,: При поступлений этого сигнала он проходит .на выход элемента И 15, переводя триггеры 9 и 10

60 н единичное состояние, а триггер 7 э нулевое. Через время, определяемое элементом задержки.24, осуществляется также перевод триггера 8 в нулевое состояние. ы результате, открываются

65 элементы И 12 и 17 и запираются зле-.

615496

Формула изобретения

5 менты И 14 и 16. Таким образом в счетчике 2 фиксируется информация о сумме двух периодов

Т Р + ( эх иь|х t гдето „- период сигналов входной последовательности с часто той Рвх 7

5 1,„- период сигналов выходной последовательности.

Число импульсов, зафиксированное в счетчике 2, определяется как (ъь,к+твх 10 г где) в„- период сигналов опорной частоты Ро

Информация, накопленная в счетчи- 1àý ке 2, переписывается в регистр памяти 4 и в счетчик 3. под действием сигналов с выхода элемента И 15, а счетчик 2 обнуляется. Далее описанный выше процесс получения информации о сумме двух периодов в счетчи20 ке 2 повторяется. Сигналы опорной частотыРов начинают подаваться на вход счетчика 3 после отпирания элемента И 17. При подаче сигналов на вход счетчика 3 они пересчитываются в нем и с его выхода подаются на третий вход множительно-делительного блока и на управляющие входы группы элементов И 20. В результате подачи сигналов с выхода счетчика, 3 на вхо- З0 ды элементов И 28 информация, заПОмненная в регистре памяти .4, периодически передается через элементы И 20 в счетчик 3, образуя его исходную ус-. тавку. Таким образом, в эависимос- 3$ ти от величины исходной уставки на выходе счетчика 3 устанавливается частота

Получение окончательного результата осуществляется с помощью множительно-делительного блока 1. При этом .на .его первый вход (вход умножения) подаются входные сигналы с 45 частотой Рв„ на второй вход (также вход умножения) подаются выходные сигналы устройства, частота которых предварительно запоминается с помощью частотно-импульсного запоминающего 50 блока 5, в котором также реализуется операция умножения на п запомненной частоты.

И, наконец, на третий вход мно-. жительно-делительного. блока (вход деления) подаются сигналы с выхода счетчика 3. В множительно-делителвном. блоке 1 осуществляется множителъноделительная операция — входная частотаР „и частота и Vи ы,х „т еoк перемножа иых тек ются и полученный результат делится на частоту следования импульсов с выхода счетчика 3.

Множительно-делительный блок реализуется аналогично описанному устройству на счетчиках 2,3 и регистре памяти 4. Поэтому на его выходе результирующие сигналы имеют равномерное распределение. Сигналы с выхода множительно-делительного блока 1 подаются на вход триггера 11 и через элемент ИЛИ 22 — на выходную клемму 31, образуя последовательность импульсов, характеризующую окончательный результат.

В результате подачи сигналов на вход триггера 11 первый же из упомянутых сигналов переводит указанный триггер в единичное состояние, что приводит к запиранию элемента И 18, для сигналов входной последовательности, которые проходили на выход устройства до момента появления сигналов на .выходе множительио-делительного блока.

В общем случае период последовательности импульсов на выходе множительно-делительного блока 1 определяется выражением

Т ( ак1 ) ъх (иых. ек алых.ояр

1 опт (ъх и ц<.тек1 где )зы» рп — определяемый пеРиод выходной частоты (на выходе блока 1), Г „хт „ — текущее значение пе: риода выходной частоты в данный момент или в частотном представлении

" оЯ1, Иых.ояр Их ИЫхЛЕК) 7 оя гдето „„— определяемая выходная

ЬЫХ ОЩ7 частота; текущее значение вы- ходной частоты в данный момент времени..

Таким образом, в.предложенном устройстве осуществляется операция интегрирования входной величины, представленной в виде частоты следования импульсов, так как:имеет местО непрерывное суммирование текущего значения выходной частоты следования импульсов с входной частотой.

Повышение точности в устройстве обусловлено тем, что обеспечивается равномерность выходной последовательности, а повышение быстродействия— существенным сокращением числа преобразований входных сигналов..устройство для интегрирования частотно-импульсных сигналов, содержа ее множительно-делительйый блок, соединенный первым входом с входом устройства, счетчик, выходы которого подключены к первым входам элементов И основной группы, и элемент ИЛИ, 615496

Составитель С.Казинов

Редактор Н.Белявская Техред м.Борисова Корректор Н.Тупица

Заказ 3911/39 Тираж 826 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5 филиал ППП Патент „ г.ужгород, ул.Проектная,4 выхсд которого соединен с выходом устройства, о т л и ч а ю ш е е с я

-тем, что., с целью повьпаения точности и быстродействия устройства, в него дополнительно введены счетчик, регистр,, триггеры, элементы И и ИЛИ, элементы задержки и частотно-импульсный запоминающий блок, соединенный выходом с.вторым входом множительноделительного блока и подключенный входом к выходу устройства и к первым входам двух элементов И, выход первого из которых подключен через iO первый эламент задержки к входу пер,вого триггера, соединенного выходом с вторым входом второго элемента И и с входом дополнительного элемента ИЛИ, подключенного вторым входом к выходу второго триггера и к первому входу третьего элемента И, а выход дополнительного элемента ИЛИ соединен с входом четвертого элемента И, выход которого подключен к входу осконного счетчика, причем выход второго элемента И соединен с первыми входами третьего, четвертого и пятого триггеров и через второй и третий элементы задержки подключен соответственно ко входу обнуления основного счетчика и ко вторым входам элементов И основной группы, выходы которых через регистр соединены с первыми.входами элементов И дополнительной группы, вторые входы которых подключены к третьему входу множительно-делительного блока и к выходу дополнительного счетчика, разрядные входы которого соединены с выходами элементов И дополнительной группы, а счетный вход подключен к выходу пятого элемента И, соединенного первым входом с выходом третьего триггера, а вторым входом — с входом запуска устройства и с первыми входами шестого и седьмого элементов И, вторые входы которых соединены с входом . устройства и со вторым входом третьего элемента И, подключенного выходом к вторым входам четвертого и пятого триггеров, первые выходы которого соединены соответственно с вторым входом первого и третьим входом шестого элементов И, причем выход шестого элемента И через четвертый элемент задержки подключей к выходу второго триггера, а второй выход пятого триггера соединен с третьим входом первого элемента.. И, а выход седьмого элемента И, подключенного третьим входом к выходу шестого триггера, соединен с первым входом основного элемента ИЛИ, второй вход которого подключен к выходу множительно-делительного блока и входу шестого триггера.

Источники информации, принятые во внимание при экспертизе:

1, Авторское свидетельство СССР

9 370614 кл. Q 06 Cj 7/18, 1967.

2, Авторское свидетельство СССР

9 350013, кл. Q 06 Cj 7/18, 1966.