Устройство запоминания и многократного воспроизведения электрических импульсов

Иллюстрации

Показать всеРеферат

1ц 617776

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Сопиалистических

Республик (61) Дополнительное к авт. свид-ву (51) М. Кл.2 б 06J

1/00 (22) Заявлено 12.10,76 (21) 2412198/18-10 с присоединением заявки Ме (43) Опубликовано 30.07.78. Бюллетень Ме 28 (45) Дата опубликования описания 10.07.78 (53) УДК 621.3.087 (088.8) по делам изобретений и открытий (54) УСТРОЙСТВО ЗАПОМИНАНИЯ И МНОГОКРАТНОГО

ВОСПРОИЗВЕДЕНИЯ ЭЛЕКТРИЧЕСКИХ ИМПУЛЬСОВ тес)тдвРственный комитет (23) Приоритег

Совета Министров СССР

Устройство относится к области измерительной техники, а именно к устройствам записи и воспроизведения однократных электрических импульсов.

Известно устройство регистрации электрических импульсов.

Оно не позволяет осуществлять запись и воспроизведение самого импульса и его предысторию.

Известно устройство записи и воспроизведения электрических импульсов с помощью запоминающего осциллографа.

Это устройство не обеспечивает записи и воспроизведения предыстории импульса.

Наиболее близкое к изобретению решение — устройство, содержащее аттенюатор аналого-цифровой преобразователь, блок основной памяти, индикатор и синхронизатор.

Такое устройство позволяет осуществлять запись электрического импульса и его многократное воспроизведение в течение длительного времени, однако оно не обеспечивает записи и воспроизведения предыстории исследуемого импульса.

Цель изобретения — возможность запоминания и воспроизведения предыстории электрического импульса.

Поставленная цель достигается тем, что в предлагаемое устройство введены блок памяти предыстории, мультиплексор, два регистра, вычитатель, цифровой компаратор, два триггера, схема И, счетчики адресов памяти предыстории и основной памяти. Выход аналого-цифрового преобразователя подключен к входу первого регистра, к входу блока памяти предыстории и к первому входу мультиплексора, выход которого подключен к входу блока основной памяти, а второй вход мультиплексора соединен с выходом блока памяти предыстории. Выход первого регистра подключен к первому входу вычитателя и к входу второго регистра, выход которого подключен к второму входу вычитателя, а выход вычитателя подключен к одному из входов цифрового компаратора, выход которого соединен с входами установки «1» обоих триггеров и с входом сброса в состояние «и - 1»

20 счетчика адреса основной памяти. Выход и счетчика адреса основной памяти связан с входом сброса в «О» первого триггера, а последний выход т счетчика адреса основной памяти связан с входом сброса в «О»

25 второго триггера, выход которого подключен к управляющему входу мультиплексора и к первому входу схемы И. К второму входу схемы И подключены выход синхронизатора и тактовые входы обоих регистров, 30 а выход схемы И вЂ” к счетному входу счетG17776 чика адреса памяти предыстории. Выход первого триггера подключен к входу запись — считывание блока памяти предыстории, а инверсный его выход — к входу запись — считывание блока основной памяти.

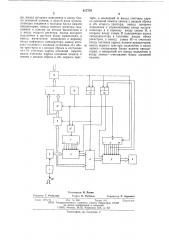

На чертеже показана структурная схема предлагаемого устройства.

Устройство состоит из аттенюатора 1, аналого-цифрового преобразователя (АЦП)

2, блока 3 памяти предыстории, мультиплексора 4, блока 5 основной памяти, индикатора 6, счетчика 7 адреса памяти предыстории, счетчика 8 адреса основной памяти, первого регистра 9, второго регистра 10, вычитателя 11, цифрового компаратора 12, триггеров 13, 14, схемы И 15 и синхронизатора 16.

Устройство работает следующим образом.

Счетчик 8 своими выходными сигналами устанавливает триггеры 13 и 14 в положение «0». В этом случае блок 3 работает в режиме записи, а блок 5 в режиме считывания записанной информации на индикатор 6. При этом напряжение с выхода аттенюатора 1 поступает на вход АЦП 2, превращается в цифровой код, который периодически записывается в ячейки блока 3 памяти, номер ячейки определяется положением счетчика 7. Очередной импульс синхронизатора 16, пройдя схему И 15, изменяет состояние счетчика 7, что определяет запись нового цифрового кода в следующую ячейку блока 1 памяти.

Таким образом, в ячейках блока 3 памяти в каждый момент времени находится информация о величине входного сигнала, какой она была и тактов синхронизатора 16 назад до текущего момента. При появлении на входе устройства электрического импульса на выходе АЦП 2 появляется цифровой код, резко отличающийся по величине от цифрового кода предыдущих моментов времени. Очередной тактовый импульс синхронизатора 16 записывает этот новый код в регистр 9, а в регистр 10 — цифровой код предыдущего состояния, который находился до этого времени в регистре 9.

С выходов регистров 9 и 10 цифровые коды поступают на входы вычитателя 11, на выходе которого появляется разница цифровых кодов настоящего и прошедшего тактов времени. Если крутизна переднего фронта электрического импульса достаточно высокая, то цифровой код на выходе вычитателя 11 должен иметь значительную величину, превышающую величину кода, набранного на одном из входов цифрового компаратора 12. В этом случае цифровой компаратор 12, произведя сравнение двух кодов, генерирует на своем выходе логическую «1», которая устанавливает триггеры

13 и 14 в положение «1», и сбрасывает счетчик 8 в состояние «п+1». При этом

65 олок 5 псреходит в режим записи, начиная с ячейки и+1, а блок 3 — и рсжим считывания информации из нес, но считывания не происходит, так как триггер 13 закрывает схему И 15, и такто=ые импульсы не пост, пают на счетчик 7 памяти предыстории, Одновременно триггср 13 переключает мультиплексор 4 и выход АЦП 2 оказывается подкл оченным к ьходу бло а 5. При последующих тактах синхронизатора 16 происходит запись входной информации в ячейки блока 5 памяти, начиная с n+1 ячейки и кончая т. Далее сигнал с выхода и счетчика 8 сбрасывал триггер 13 в положе«ие «О». При этом открывается схема

И 15 и мультиплексор 4 подключает выход блока 3 к входу блока 5. Последующие такты синхронизатора 16 идут на счетчик 7, в результате чего все содержимое в и ячейках блока 3 записывается в ячейки блока

5, начиная с 1-й ячейки и кончая и-й ячейкой.

После этого сигнал с и выхода счетчика

8 сбрасывает триггер 14 в состояние «О» и устройство переходит в первоначальное состояние, причем в блоке 5 оказывается записанной предыстория импульса в ячейках

1 — и и сам импульс в ячейках (и+1) — т.

В таком порядке информация об импульсе

Itllдикатор G, 11

Таким образом, устройство осуществляет автоматическую запись и воспроизведение электрического импульса с его предысторией. При этом устройство определяет момент начала электрического импульса, осуществляя дифференцирование формы входного сигнала и сравнивая полученную производную с заданной уставкой.

Изобретение позволяет автоматизировать процесс регистрации результатов испытаний, повысить их точность и достоверность, значительно сократить затраты времени на обработку результатов испытаний, что способствует получению значительного экономического эффекта.

Формула изобретения

Устройство запоминания и многократного воспроизведения электрических импульсов, содержащее аттснюатор, аналого-цифровой преобразователь, блок основной памяти, индикатор и синхронизатор, о т л и ч а ющ е е с я тем, что, с целью обеспечения возможности запоминания и воспроизведения предыстории импульса, в устройство введены блок памяти предыстории, мультиплексор, два регистра, вычитатель, цифровой компаратор, два триггера, схема И, счетчики адресов памяти предыстории и основной памяти, причем выход аналого-цифрового преобразователя подключен к входу первого регистра, к входу блока памяти предыстории и к одному из входов мультиплексо617776

Составитель И. Панин

Техред Н. Рыбкина

Редактор Т. Рыоалова

Корректор P. Беркович

Заказ 1275/14 Изд. ¹ 546 Тираж 841

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 5К-35, Раушская наб., д. 4/5

Подписное

Типография, пр. Сапунова, 2 ра, выход которого подключен к входу блока основной памяти, а другой вход мультиплексора соединен с выходом блока памяти предыстории, выход первого регистра подключен к одному из входов вычитателя и к входу второго регистра, выход которого подключен к другому входу вычитателя, а выход вычитателя подключен к первому входу цифрового компаратора, выход которого соединен с входами установки «1» обоих триггеров и с входом сброса в состояние

«и+-1» счетчика адреса основной памяти, выход счетчика адреса основной памяти и связан с входом сброса в «0» первого триггера, а последний т выход счетчика адреса основной памяти связан с входом сброса в «0» второго триггера, выход которого подключен к управляющему входу мульти5 плексора и к первому входу схемы И, к второму входу схемы И подключены выход синхронизатора и тактовые входы обоих регистров, а выход схемы И вЂ” к счетному входу счетчика адреса памяти предыстории, 10 выход первого триггера подключен к входу запись — считывание блока памяти предыстории, а инверсный его выход подключен к входу запись — считывание блока основной памяти.