Запоминающее устройство

Иллюстрации

Показать всеРеферат

О Il И С А Н И Е (ii) 60788

И3ОБРЕТ ЕНИЯ

Сова Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 03.05.76 (21) 2354652/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.07.78. Бюллетень № 28 (45) Дата опубликования описания 27.07.78 (51) М. Кл. G 11С

11/00

Государственный комитет

Совета министров СССР по делам изобретений и открытий (53) УДК 681 327 6 (088.8) (72) Автор изобретения

И. М. Соколов (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике, в частности к технике микропрограммных запоминающих устройств.

Извесгны микропрограммные запоминающие устройства (1, 2), Одно из них содержит матрицу, дешифратор и счетчик, выходы которого подсоединены через дешифратор к горизонтальным шинам матрицы (1).

Это устройство может быть использовано 10 при принудительном порядке следования микрокоманд, что ограничивает область его применения.

Наиболее близким техническим решением к изобретению является запоминающее уст- 15 ройство, содержащее накопитель, входы которого через дешифратор адреса соединены с регистром адреса, а выходы подключены к регистру микрокоманд, соединенному с генератором (2). 20

Такое устройство позволяет изменять порядок следования микрокомапд в зависимости от внешних условий, но обладает малой гибкостью из-за отсутствия возможности раздельного управления зонами микрокоманды, адреса, переходов и задержки, что приводит к нерациональному использованию объема памяти накопителя и ограничивает область применения устройства.

Цель изобретения — расширение области применения запоминающего устройства путем обеспечения возможности раздельного управления зонами накопителя.

Для этого в устройство введены дополнительные дешифраторы, счетчики и шины коммутации, причем выходы накопителя через последовательно соединенные первый счетчик и первый дополнительный дешифратор соединены с первыми шинами коммутации, информационные выходы накопителя через второй дополнительный дешифратор подключены к соответствующим входам накопителя, а выходы второго счетчика через третий дополнительный дешифратор связаны с вторыми шинами коммутации.

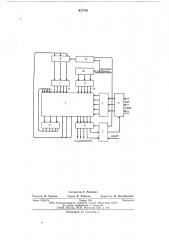

На чертеже представлена структурная схема запоминающего устройства.

Устройство содержит накопитель 1 с зонами микрокомгнд перехода и адреса, входы которого через дешифратор 2 адреса соединены с регистром 3 адреса. Одни выходы накопителя 1 подключены к регистру 4 мцкрокоманд, связанному с генератором

5. Вторые выходы накопителя через последоватсльно соединенные первый счетчик 6 и первый дополнительный дешифратор 7 связаны с первыми шинами 8 коммутации накопителя. Информационн,ic выходы на копп617788

3 теля соединены через второй дополнительный дешифратор 9 с соответствующими входами накопителя, а выходы второго счетчика 10 через третий дополнительный дешифратор 11 — с вторыми шинами, 12 коммутации накопителя. При этом выходы генератора 5 связаны непосредственно с цепями управления регистров микрокоманд 4 и адреса 3 и через схему И 13 с,входом счетчика 6, а второй вход схемы И 13 соединен с входом счетчика 10 и подключен к внешнему формирователю признаков переадресации, например к арифметическому устройству. Зоны задержки, адреса и переходов в накопителе 1 разбиты на поля, имеющие аналогичное назначение, что позволяет по одному коду операции выбирать из накопителя сразу все задержки, адреса микрокоманд и адреса переходов, необходимые для выполнения данной операции.

Работает устройство следующим образом.

После подачи импульса «Запуск» генератор 5 обеспечивает запись кода операции в регистр 3 адреса, по которому из накопителя 1 выбярается слово со всеми полями адреса микрокоманд, переходов и задержек, необходимых для выполнения дан ной операции. Но подключается только то поле адреса микрокоманды с полем задержки, которое подсоединено в данный момент времени к возбужденному выходу дешиф ратора 7. И под1ключается только то поле перехода., которое подсоединено,в данный момент времени к возбужденному выходу дешифратора 11. При, этом информация из возбужденных полей адреса микрокоманд и задержки, пройдя через дешифратор 9, обеспечивает выборку соответствующей микрокоманды из зоны микрокоманд и соответствующей задержки из зоны задержки накопителя 1, которые переписываются в регистр 4 микрокоманд,и используются для управления временным режимом работы генератора 5 и для упра|вления внешними устройствами, например арифметическим устройством, устройством управления и запоминающими устройствами LIBM.

Введенная задержка в генератор 5 определяет время существования данной микрокоманды, после чего на выходе его вырабатывается импульс, который, пройдя схему

И 13 (при отсутствии признака переадресации), поступает на. вход счетчика 6, формируя следующий по порядку адрес для данной операции. П ри этом возбуждается следующая шина дешифратора 7, после чего

З0

55 цикл работы повторяется. При наличии условий для переадресации, например из-за переполнения, изменения знака, наличие цикла, регистровый вход счетчика 6 подключается к выходам зоны перехода накопителя 1, содержащей несколько полей переходов. В зависимости от количества импульсов, поступающих на вход счетчика 10, подключается то или иное поле перехода, в котором находится адрес перехода, переписываемый в счетчик 6, что изменяет:естественный по рядок выборки микрокоманд для данной операции, запрограммированной заранее. По исчезновении при знака переадресации вход счетчика 6 вновь подсоединяется к выходу генератора 5, далее цикл работы повторяется. После выборки всех микрокоманд для выполняемой операции в генераторе 5 формируется .импульс, обеспечивающий запись в региспр 3 адреса кода следующей операции, затем цикл работы повторяется.

Введение в запоминающее устройство дешифраторов, счетчиков и шин коммутации позволяет осуществить раздельное управление полями всех зон накопителя. Это приводит к экономичному использованию дорогостоящей памяти и к расширению области применения устройства.

Формула изобретения

Запоминающее устройство, содержащее накопитель, входы которого через д|ешифратор адреса соединены с регистром адреса, а выходы подключены к регистру микрокоманд, соединен ному с генератором, отличающееся тем, что, с целью расширения области применения устройства, оно содержит дополнительные дешифр аторы, счетчики и шины коммутации, причем выходы накопителя через последователь но соединенные первый счетчик и пер вый дополнительный дешифратор соединены с первыми шинами коммутации, информационные выходы накопителя через второй дополнительный дешифратор подключены к соответствующим входам накопителя, а выходы второго счетчика через третий дополнительный дешифратор связаны с вторыми шинами коммутации.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 215613, кл. G 06F, 1966.

2. Булей Г. Микропрограммирование. М., Изд. «Мир», 1973.

617788

Подписное

Заказ 1354/19 Тираж 734

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Я-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Составитель Г. Мамджян

Редактор И. Грузова Техред Н. Рыбкина Корректор И. Позняковская