Устройство для сравнения чисел в системе остаточных классов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е

ИЗОБРЕТЕНИЯ

Сеее Севетепиа

Фецраааиетинкииа

Реапубпии (11) 618739, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (63) Дополнительное к авт. свид-ву (22) Заявлено ORD276 (21) 231883/18-24 с присоединением заявки J4 (51) М. Кл.

G06 F 7/04

Государственный комитет

Совета Министров СССР но делам изобретений и отнрытнй. (23) Приоритет (43) Опубликовано 050878.6þëëåòåíü ph 29 (45) Дата опубликования описания 280678 (5З) УДК 681 ° 325, 066(088.8) (72) Авторы изобретения

l0.Д.Полисский и М.Г.Факторович (71) Заявитель

Научно-HcgaeposaTeascKHN и опытно-конструкторский институт автоматизации черной металлургии (54) УСТРОЙСТВО ДЛЯ CPABHEHHH ЧИСЕЛ

В СИСТЕМЕ ОСТАТОЧНЬИ КЛАССОВ

Изобретение. относится к автоматике и вычислительной„ технике и может быть использовано для обработки данных в схемах автоматики и цифровых вычислительных машинах, работаю- а щих s системе остаточных классов,, Известно устройство для сравнения чисел, выраженных в системе остаточных классов, содержащее регистры, сумматоры, элементы И, ИЛИ, 10

03: Ц

Недостатком этого устройства является то, что оно позволяет устанавливать лишь совпадение или несовпадение двух чисел по величине, N но не дает представления об их качественном соотношении (больше, меньше) .

Наиболее близким по технической сущности к изобретению является устройство для сравнения чисел в системе остаточных классов, содержащее сумматоры, элементы И, элемент НЕ, регистры, схему сравнения и Ь узлов анализа, каждый из которых состоит из сумматора, регистра, схемы сравнения, элементов И, ИЛИ, причем выходы регистра соединены со входами схемы сравнения, сумматора и первого элемента ИЛИ, выход которогО подключен к первому входу элемента И, выход которого соединен с управляющим входом сумматора, информационные выходы которого подключены ко входам регистра, а управляющий выход — к первому входу второго элемента ИЛИ, выход которого соединен с управляющим входом схемы сравнения, узла анализа.

Недостатком этого устройства является невысокое, быстродействие,обусловленное тем, что для получения результата сравнения необходимо затратить количество тактов, равное абсолютному значению наибольшего числа.

Целью изобретения является повышение быстродействия устройства.

Для этого в устройстве выходы первых элементов ИЛИ всех узлов анар àçà соединены со входами первого элемента И, выход которого соединен с первым входом второго элемента

И и через элемент НŠ— с первым входом третьего элемента И, выход которого подключен к управляющему входу первого суьматора, а второй вход— к выходу схемы сравнения, входы которой соединены с выходами схем сравнения всех узлов анализа, выход вто618739 рого элемента И подключен к управляющему входу второго сумматара, выходы которого соединены со входами первого регистра, выходы которого подключены ко входам второго сумматора, управляющий вход третьего сумматора соединен с выходом схемы сравнения, а его информационные выходы подключены ко входам второго регистра, выЙбды койорого соединены со входами третьего сумматора, вьпсоды первого суыаатора подключены ко входам тре- i0 тьего регистра, выходы которого соединены со входами первого сумматора, .5 выход схейы сравнения подключен ко вторым входам элементов И всех узлов анализа, а.вторые входы элементов .ИЛИ всех узлов анализа подключены к управляющей шине устройства.

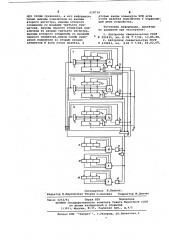

На чертеже изображена функционалвная схема устройства.

Устройство содержит,П узлов ана- Ю дюза 1, 32, ...,, состоящие из сумматоров 2, 2 . ..2 „, схем сравнения 3, 3, . .. 3» регистров 4

4>, ... 4>, элементов И 5,, 5>, 5 „элементов ИЛИ 6,,6, ... 6и, 25 .элементов ИЛИ 7, 7, ... 7п, сумматоры 8-10,.регистры: 11-13, элементы

И 14-16, схему сравнения 17, элемент

НЕ 18, управляющую шину 19.

Устройство работает следующим образом.

К моменту начала сравнения в регистрах 4, 4, ... 4 записаны сравниваемые числа. После включения сигналом по шине 19 через элементы ИЛИ

6, 6>, ... 6> осуществляется определение чисел А ц,, ф„,,„,, Х„„,„„ и перезапись их в схему сравненйя 17.

Схема сравнения 17 определяет мини- 40 мальное из этих чисел (k ) и пода- ет его значение иа вычитающие входы сумматоров 2, 2, ...,2,п через открытые элементы И. 5, 5, 5 в. Величинами „вычитается из всех сравниваемых чисел.

Одновременно величина я с выхода схемы сравнения .17 подается непосредственно на вход сумматора 8 и через открытйй элемент И 15 поступает иа вход суйматора 10. После вычитания величины из всех сравниваемых чисел и добавления этой величийы в Регистры 11 и 12 сумматоры 2, 2, устанавливаются в нулевое состояние и управляющий сигнал с выХсщов сумматоров 2, 2, ..., 2п . через соответствующие элементы ИЛИ

6g i 6„я ° . ° . 6п поступает на входы

Регистров 34 у. 3р ° ° ъ 3 и р разРЯЯая 60 осуществление следующего такта.

В следующем такте также происхо- д"т определение k „, Jh +„- Каях для сравниваемых чисел, уменьшенных

Na величину 3 щ, выбор величин & ° 65

Фю А „,p o„„,,......k ф вычитание величины из чисел и его добавление в регистры 11 и 12.

Процесс вычитания продолжается до тех пор, пока одно из чисел не станет равным нулю. При этом исчез .нет единичный сигнал на выходе одного из элементов ИЛИ 7 ., 7«

7„, вследствие чего закроется один из элементов И 51, 5« ... 5> а также элементы И 14 и 10,и откроется элемент И 16. В регистре окажется записанным наименьшее из сравниваемых чисел.

В процессе последующего вычитания щ из сравниваемых чисел эта величина добавляется в регистр 13 через открыткой теперь сигналом с выхода элемента НЕ 18 .элеменТ И 16 и попрежнему добавляется в регистр 12.

Процесс продолжается до тех пор, пока наибольшее из чисел не станет равньм нулю. При этом цикл работы устройства заканчивается. В результате в регистр 12 записано наибольшее число, в регистре 13 — максимальная разность.

Формула изобретения

Устройство для сравнения чисел в системе остаточных классов, содержащее сумматоры, элементы И, элемент

НЕ, регистры, схему сравнения н и узлов анализа, каждый из которых состоит из сумматора, регистра, схемы сравнения, элементов И, ИЛИ, причем выходы регистра соединены со входами схемы сравнения, сумматора и первого элемента ИЛИ, выход которого подключен к первому входу элемента И, выход которого соединен с управляющим входом сумматора, информационные выходы которого подключены. ко входам регистра, а управляющий выход — к первому входу второго элемента ИЛИ, выход которого соединен с управляющим входом схемы сравнения узла анализа, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в нем выходы первых элементов ИЛИ всех узлов анализа соединены со входами первого элемента И, выход которого соединен с первым входом второго элемента И и через элемент

НŠ†. с первым входом третьего элемента И, выход которого подключен к управляющему входу первого сумматора, а второй вход - к выходу схемы сравнения, входы которой соединены с . выходами схем сравнения всех узлов анализа, выход второго элемента И подключен к управляющему входу второго сумматора, выходы которого соединены со входами первого регистра, выходы которого подключены ко входам второго сумматора, управляющий вход ,третЬегo сумматора соединен с выхо1. Авторское свидетельство СССР

2424 35, кл, Я ° 06 W 7/04, 13.05. 69.

2. Авторское свидетельство СССР, Р 234003, кл. 506 F 7/04, 04.02.69 °

Составитель: Б.Белкин 1 Редактор И.Марховская Техред О.Попович Корректор М.Демчик

Заказ 4262/41 Тираж В26 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

11 303, Москва,- Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.ужгород, ул.Проектная,4

5 618739 6 дом схемы сравнения, а его информаци- вторые входы элементов ИЛ1 всех онные выходы подключены ко входам .Узлов анализа подключены к управляювторого регистра, выходы которого щей шине устройства. соединены со входами третьего сумматора, выходы первого сумматора подИсточники информации, принятые ключены ко входам третьего регистра, во внимание при экспер™ge выходы которого соединены со входами первого сумматора, выход схемы сравнения подключен ко вторым входам элементов И всех узлов анализа, а