Устройство для защиты памяти

Иллюстрации

Показать всеРеферат

ОП СА ИЕ

ИЗОБРЕТЕНИЯ (И) б18741

Союз Советских

СО4иэпнстичееких

Рес убяи

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (51) М. Кл.

Q 06 F 9/20

Q 11 С 29/.00 (22) Заявлено 010277 (21),244854 З/18-24 с присоединением заявки .№вЂ” (23) Приоритет(43) Опубликовано.050878. Бюллетень № 29 (45) Дата опубликования описания 280678

Государственный комитет .

Совета Министров СССР,, но делам изобретений н открытий (53) УДК 68 1. 325 (088 ° 8) (72) Авторы .изобретения

A A Обухович и М ° Н е БОбОВ (71) Заявитель (54) УСТРОИСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ

Изобретение относится к области вычислительной техники и может быть использовано в ЦВМ.

Известно устройство для защиты памяти (11, содержащее регистры, 8 дешифраторы, схемы сравнения адресов и логические элементы И, ИЛИ и НЕ.

Однако функциональные возможности такого устройства ограниченные, так как оно не позволяет защищать отдель- 10 ные ячейки памяти.

Наиболее близким к изобретению по техническоч сущности и достигаемому результату является устройство для защиты памяти j2) содержащее первый .<оммутатор, выход которого является вйходом устройства, дешифратора, группа выходов которого соединена со входами второго коммутатора, первая группа выходов которого соединена с единичными входами триггеров группы триггеров, группу элементов

И, первые входы которых соединены с выходами соответствующих триггеров группы триггеров,, элемент И, первый и

25 второй входы которого соединены соот. ветственно с выходами элемента ИЛИ и датчика времени. Адресйый вход устройства соединен со входом дешиф.ратора и с кодовым входом первого коммутатора, управляющий вход которого соединен с выходом элемента И.

Недостаток устройства состоит в том, что оно не учитывает количество обращений к защищаемой ячейке, а возможность обращения к ячейке неограниченное число раз снижает надежность работы.

Цель изобретения - повышение надежности.

Поставленная цель достигается тем, что устройство содержит группу регистров сдвига, причем информационные входы регистров сдвига соедине- ны с выходами соответствующих элементов И группы элементов И. Управляющие входы регистров сдвига соединены с соответствующими выходами второй группы выходов второго коммутатора. Выход дешифратора соединен с нулевыми входами триггеров группы триггеров. Выходы регистров сдвига соединены с соответствующими входами „элемента ИЛИ и датчика времени, а вторые входы элементов И группы . элементов И соединены с настроечным входом устройства.

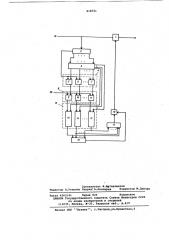

Структурная схема устройства представлена на чертеже.

Э 6

Устройство для защиты памяти содержит первый коммутатор 1," дешифратор 2, второй коммутатор 3 группу

4 триггеров 5-7, группу 8 элементов И

9-11, группу 12 регистров сдвига

13-15, датчик времени 16, элемент

ИЛИ 17, элемент И 18.

Устройство работает следу1ощим образом„

В начальном состоянии устройство подготавливается к работе. При этом на адресный вход 19 устройства подаются коды адресов:ячеек, которые необходимо-аащищать, а на настроечный вход 20- число ймпульсов, равное числу допустимых обращений к данной ячейке. Код ячейки адреса через дешифратор 2 и коммутатор 3 поступает на единичный вход соответствующего триггера, группы 4, при этом соответствующий триггер (5 7) выдает сигнал на вход группы .8 элементов И, а на второй вход соответствующего элемента И поступают импульсы со входа 20 устройства, которые проходят через открытый элемент И и записываются в соответствующем регистре сдвига груп1 пй 12 регистров сдвига. При поступлении следующего кода адреса ячейки дешифратор 2 подает на нулевые входы триггеров 5-7 группы 4 сигнал, по которому все триггеры устанавливаются в нулевое состояние.

Эатем цикл работы повторяется.

Адрес запрашиваемой ячейки поступает со входа 19 устройства на первый вход коммутатора 1 и на вход дешифратора 2. На соответствующем выходе дешифратора 2 появляется сиг-. нал, который поступает через коммутатор 3 на управляющий вход соответствующего реристра сдвига группы 12..

Если в этом регистре записано некоторое число разрешенных .обращений, то на его .выходе появляется сигнал, а число разрешенных обращений к ячейке уменьшается на единицу. Сигналы с выходов группы 12 регистров сдвига поступают через элемент ИЛИ 17 "на вход элемента И 18 и на вход датчика

16 времени, который вырабатывает временной интервал,в течение которого разрешается допуск к запрашиваемой ячейке,памяти. Этот сигнал через открытый-элемент ИЛИ 17 поступает на управляющий вход коммутатора 1 и раз

Решает обращение к ячейке в течение сформированного интервала времени.

Если в регистре не: записано число разрешенных обращеиий, т ° å. äîâóñêà ê+ ячейке памяти нет, то сигнал на вы18741 ф ходе регистра не формируется, и допуск к ячейке запрещается.

Таким образом предложенное устройство позволяет повысить по сравнению с известник устройством надежность защиты ячеек памяти, так как оно позволяет ограничивать число допустимых обращений к ячейке.

Если по ходу программы произошло непредусмотренное обращение к закрытой ячейке, то это обращение учитывается в дальнейшем при выполнении програьиы и.при последнем предусмотренном обращении к этой ячейке разрешения на допуск к ней не будет дано.

10

Формула изобретения устройство для защиты памяти, содержащее первый коммутатор, выход которого является выходом устройства, дешифратор, группа выходов, которого соединена со входами второго комму- татора, первая группа, выходов кото» рого соединена с единичными входами триггеров группы триггеров, группу элементов И, первые входы которых 5 соединены с выходами соответствующих триггеров группы триггеров, элемент

И, первый и второй входы которого соецинены соответственно с выходами элемента ИЛИ и датчика времени, при30 чем адресный вход устройства соединен со входом дешифратора и кодовым входом первого коммутатора, управляющий вход которого соединей с выходом элемента И, о т л и ч а ю щ е е35 с я тем, что, с целью повышения надежности,оно .содержит группу регистров сдвигау причем информационные входы регистров сдвига соединены с выходами соответствующих эле40 ментов И группы элементов И, управляющие входы регистров сдвига соединены.с соответствующими выходами второй группы выходов второго коммутатора; выход дешифратора соединен с-нулевычи входами триггеров группы триггерову выходы регистров сдвига. соединены с соответствующими входами элемента ИЛИ и датчика времени, .а вторые входы элементов И груПпы элементов.И соединены с настроечным входом устройства.

Источники информации, принятые . во внимание при экспертизе:

1,Авторское-свидетельство СССР

Р 306463, кл. 906 F 11/00, 1973.

66 2. Заявка 9 236 129 7/24, кл.

;411 С 29/00»23.11.76» по которой принято решение о выдаче авторского свидетельства.

618741

Составитель Ф.Шагиахметов

Редактор Л.утехина Техред А.Алатырев Корректор М.Демчик

3 4262/41 акаэ Тираж 826 Подписное ов СССР

ЦНИИПИ Государственного комитета Совета Министров по делам изрбретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.укгород,ул.Проектная,4