Элемент цифровой сетки

Иллюстрации

Показать всеРеферат

О П N!

Сеюз Севетскик

Сои,,нанистичеснн а

Респубпик (11) б18745

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву (22) Заявлено 140277 (21) 2451378/18-24 с присоединением заявки,%в (23) Приоритет(43) Опубликовано 050878, Бюллетень И (29 (51) М. Кл.

906 f 15 20

Государствеииый комитет

Совета Министров СССР по делам изобретений и открытий (53) Уlllt 681.325 (088. 8) (45) Дата опубликования описания 2806,78 (72) Авторы изобр тения

В.II.Áîþö и Ю.Я.Ледянкин

P1) Заявитель

Ордена Ленина институт кибернетики AH Украинской ССР (54) ЭЛЕМЕНТ ЦИФРОВОИ СЕТКИ

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств для решения многомерных задач теории поля, описываемых эллиптическими уравнениями (Лапласа, Пуассона, Поккельса) и парабо."ическими уравнениями (типа Фурье, теплопроводности...).

Известно устройство (1), содержащее сдвигающие регистры, сумматор и коммутатор.

Недостатком такого устройства является низкая производительность.

Наиболее близким по технической сущности к изобретению является элемент цифровой сетки (2, содержащий сумматор, первый выход которого соединен со счетньм входом счетчика, регистр сдвига и два триггера. Выход первогс триггера соединен с первьм входом сумматора.

Недостатком устройства является недостаточная гибкость при построении решающих цифровых сеток.

Целью изобретения является повышение гибкости.

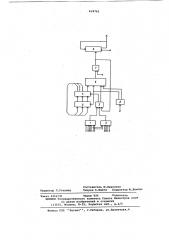

Поставленная цель достигается тем, что в предложенный элемент цифровой сетки введенй буферный регистр, два мультиплексора и коююутатор. Группы входов элемента через мультиплексоры соединены со входами сумматора, второй выход которого соединен с первым входом коммутатора, выход:-которого и первый вход элемента соединены с входами первого триггера, выход которого соединен с первьм входом регистра сдвига, другие входы которого соединены со вторым входом элемента, со своим выходом и выходом элемента. Группа выходов счетчика соединена через буферный регистр со своими входами. Третий вход элемента соединен с входом второго триггера, первый выход которого соединен с входом буферного, регистра и вторым входом коммутатора, третий и четвертый входы которого соединены с выходом счетчика и .вторым выходом второго триггера соответственно.

Структурная схема элемента цифровой сетки приведена на чертеже.

Элемент содержит мультиплексоры

1,2, сумматор 3, счетчик 4, буферный регистр 5, коммутатор 6, триггеры 7,8 и регистр 9 сдвига.

Элемент цифровой сетки работает следующим образом.

618745

Составитель Ю.Ледянкин

Техред З.Фанта Корректор М.Демчик

Редактор Л.утехина

Филиал ППП Патент, r.Óæãîðîä, ул.Проектная,4

Заказ 4262/41 Тираж 826 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, E-35, Рауыская наб., д.4/5