Устройство для распознавания образов

Иллюстрации

Показать всеРеферат

О П И (:--- А-- Н И E.

ИЗОБРЕТЕНИЯ

Ссноз Советски к

Социалистических

Республик (1i) 618759

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 250277 (21) 2457808/18-24 (51) M. Кл. с присоединением заявки №

06 К 9/00 (23) Приоритет— (43) Опубликовано 050878. Бюллетень № 29 о (45) Дата опубликования описания 220678

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.327.12 (088. 8) (72) Авторы изобретения

В.К.Шишков и О.С.Романов (7l) Заявитель

Казанский ордена Трудового Красного Знамени авиационный институт им. A.Í.Tónoëåâà (54) УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ

Изобретение относится к области технической кибернетики и может быть использовано в системах цифровой обработки информации, например в системах управлени я воздушного движени я. S

Известно устройство для распоэнавани я образов, содержащее блоки формирования и преобразования признаков, соединенные с блоками управления, синхронизации и памяти, блок формирова- 10 ния эталонных признаков, подключенный к блоку сравнения и к блоку памяти, вычислит ел ьный блок, соединенный с выходным и пороговым блоками, и элементы И, ИЛИ 11). IS

Недостаток известного устройства состоит в его конструктивной сложности.

Наиболее близким по технической сущности к изобретению является уст- 20 ройство, содержащее блок синхронизации, соединенный с блоками формирования признаков, памяти, управления и сравнения, сумматор, входы которого подключены к блокам памяти и синхро- 25 ниэации, а выход через последовательно соединенные блоки сравнения и управления подключен к блоку памяти, соединенному с блоком сравнения, выходной блок, подключенный к блокам 30 памяти и синхронизации, и пороговый блок (21 .

Его недостаток заключается в низкой надежности распознавания сигналов при наличии помех.

Цель изобретения состоит в повышении надежности распознавания.

Поставленная цель достигается тем, что предложенное устройство содержит блок индексации признаков, входы которого соединены с блоками формирования признаков, синхронизации и памяти, а выход пЬдключен к одному из входов блока памяти, другие входы которого соединены с пороговым блоком, подключенным к блоку синхронизации, и логический блок, соединенный с сумматором и блоками сравнения, синхронизации и памяти.

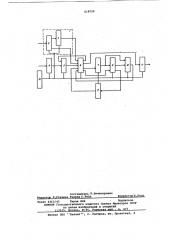

На чертеже представлена стРуктуРная схема устройства.

Устройство включает пороговый блок 1, содержащий узел преобразования априорных данных 2 и узел упорядочивания признаков 3, блок формирования признаков 4, блок индексации признаков 5, блок памяти 6, сумматор 7, блок сравнения 8, блок уптзавления 9, логический блок 10, вы618759 ходной блок 11 и блок синхронизации

12.

Устройство работает следующим образом.

Перед началом распознавания в узле 2 преобраеования априорных данных блока 1 определяются средние значения каждого признака или математические ожидания, если известен закон распределения какого-либо признака..

На основании полученных средних значений определяются начальные значения порогов. В этом же блоке определяются текущие значения порогов для каждого признака или цля каждого шага обработки, которые затем записываются 15 в блок памяти 6.

В узле 3 полученные средние значе -. ния отношений правдоподобия по каждому признаку упорядочиваются по величине и подаются в блок памяти 6 в ви- 20 де весов этих признаков.

Подлежащие распознаванию сигналы . подаются на вход блока 4, где признаки каждого сигнала преобРазуются в соответствующие отношения правдоподобия, которые поступают на первый вход блока 5, осуществляющего присвоение весов, на другой вход которого из блока 6 поступают априорно определенные веса каждого, признака.

В блоке 5 каждому отношению правдоподобия присваивается соответствующий вес. Все отношения правдоподобия, характеризующие отдельный сигнал, заносятся в блок памяти 6 в порядке убывания их весов.

Распознавание каждого сигнала из заданного множества сигналов производится по шагам. На первом шаге из блока памяти 6 извлекается отношение правдоподобия с максимальным весом, которое сравнивается в блоке 8 сравнения с соответствующими верхним и нижним порогами, поступающими иэ блока 6 . При непревышении порогов блок

8 сравнения вырабатывает управляющий 45 сигнал в блок 9 управления, по сигналам которого из блока памяти выбирается следующее по весу отношение правдоподобия которое в блоке 7 суммируется с предыдущим отношением, и 80 полученное суммарное отношение правдоподобия сравнивается в блоке 8 с порогами второго шага.

При превышении порога на какомлибо шаге в блоке 10 производится анализ на то, какой из порогов превышается: верхний или нижний. В случае превышения нижнего порога, сигнад описываемый суммарным отношением правдоподобия, не относится к истинному, и через блок 12 происходит об- 60 ращение к последующему сигналу из множества возможных. В случае превышения верхнего порога суммаРное отношение правдоподобия рассматриваемого сигнала из блока 7 через блок 10+ заносится в блок памяти 6. На этом процедура распознавания очередного сигнала заканчивается, и устройство переходит к распознаванию следующего сигнала.

После аналогичной обработки всех сигналов из множества сигналов, поступивших на вход устройства, последнее приступает к выбору одного истинного сигнала среди множества сигналов, суммарные отношения правдоподобия которых превысили верхние пороги . Действительно истинным сигналом выбирается сигнал, имеющий максимальный суммарный вес., для выделения которого запомненные суммарные отношения правдоподобия подают на вход выходного блока 11, осуществляющего выделение суммарного максимального веса, с выхода которого снимается истинный сигнал.

Работа устройства синхронизируется блоком .12, который подключен ко всем блокам устройства.

Устройство предназначено для распознавания сигналов, описываемых небольшим количеством признаков (порядка несколько единиц), Введение новых блоков и новых конструктивных связей позволило существенно повысить надежность распознавани я сигналов .

Формула изобретения

Устройство для распознавания образов, содержащее блок синхронизации, соединенный с блоками формирования признаков, памяти, управления и сравнения, сумматор, входы которого подключены к блокам памяти H синхронизации, а выход через последовательно соединенные блоки сравнения и управления подключен к блоку памяти, соединенному с блоком сравнения, выходной блок, подключенный к блокам памяти и синхронизации и пороговый блок, о тл и ч а ю щ е е с я тем, что, с целью повышения надежности распознавания, оно содержит блок индексации признаков, входы которого соединены с блоками Формирования признаков, синхронизации и памяти, а выход подключен к одном, из входов блока па- мяти, другие входы, которого соединены с пороговым блоком, подключенным к блоку синхронизации, и логическйй блок, соединенный с сумматором и с блоками сравнения, синхронизации- и памяти.

Нсточники инФормации, принятые во внимание при экспертизе:

1. Патент СИИ 9 384976,кл.340-146,3

1974.

2. Патент США 93810162,кл,,340-1725, 1974 б 18759

Сост авктрлыТ. Ни ипорович

Р акто Л.Утехина Те С.Seva Ко екто Е.Папп

Эанаэ 4263/42 Тираж 826 Подписное

ЦПИИПИ Государственного комитета Совета Министров СССР по делам иэобретвний и открытий

113035 Иосква K- 5 Ра окая наб. . 4 5

Филиал ппп патент ., г, Ужгород, ул, проектная, 4