Ячейка памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советснна

Соцнайистичесниа

Ресйубпнн

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) дополнительное к авт. свнд-ву (22) ЗайвленооЯ1176 (21) 2419436/18-24 (51) М. Кл. с присоединением заявки М—

11 С 19/28

Государственный коннтет

Совета Министров СССР ао аелаи изобретений и открытий (23) Приоритет (43) Опубликовано 050878. Бюллетень pfo 29 (45) Лата опублнковання описания 2006.78 (53) УДК 681.327.,67 (088.8) (72) Авторы н3обретення э.и.Востриков, с .д.гуля, А.н.дьа лов и В.A. Яковенко (7!) Заавнтель (54) ЯЧЕЙКА ПАМЯТИ

Изобретение относится к вычислительной технике и может быть применено в устройствах ввода и буферных устройствах памяти.

Известна ячейка памяти, например триггер на двух элементах НЕ, элементы И и ИЛИ (1).

Наиболее близким техническим решением к изобретению является ячейка памяти, содержащая два последователь- 10 но включенных элемента ИЛИ вЂ” НЕ, три ключа и транзистор. Первый вход первого элемента ИЛИ-ЙЕ подключен через первый ключ к входу ячейки, второй вход первого элемента ИЛИ-HE подключен15 через второй ключ к .выходу второго элемента ИЛИ-НЕ, а транзйстор, включен между источником питания и выходной шиной разряда регистра (2) .

Недостатком этого устройства яв- ф) ляется наличие непосредственной связи между ключами, т.е. жесткие требования к соотношению длительностей управляющего и информационного сигналов, отсутствие возможности коррекции 25 выходной информации без разрушения информации в памяти.

Целью изобретения является расширение области применения ячейки за счет увеличения диапазона управляю-, Э3 щнх сигналов.

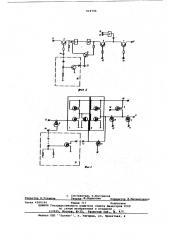

Поставленная цель достигается тем, что предложенная ячейка содержит два дополнительных ключа, выход второго элемента ИЛИ-НЕ через первый и второй дополнительные ключи подключен к выходу ячейки, а точка соединения дополнительных ключей через третий ключ подключена к шине питания.

На фиг..1 приведена финкционаиьная схема ячейки памяти; на фиг. 2 - вариант схема ячейки памяти на полевых транзисторах.

Ячейка памяти содержит перый 1 и второй 2 элементы ИЛИ-НЕ, превый 3, второй 4 и третий 5 ключи, а также первый 6 и второй 7 дополнительные ключи °

Ключ 3 подключен ко входу 8 ячейки, ключ 7 — к ее выходу 9, а ключ 5 — к шине питания 10. Дополнительные входы

11-15 ячейки служат для задания различных режимов ее. работы.

При выполнении ячейки памяти на полевых транзисторах (фиг.2) первый элемент ИЛИ-НЕ 1 содержит три полевых транзистора, а второй элемент ИЛИ-НЕ

2 — два полевых транзистора. К ячейке памяти может быть подключен вспомогательный ключ 16, обеспечивающий вспомогательные режимы работы.

618796

Элементы ИЛИ-НЕ 1 и 2 к ключ 4 образуют триггер, в котором длительность входного сигнала зависит только от постоянной времени цели обратной связи. . Вспомогательный ключ 16 обеспечивает установку триггера в нулевоесостоя- ние, так как-сигнал записи ка уиравляющем входе ключа 3 прерывает цепь обратной связи, что способствует сокраценив времени записи"куля", т.е. сок- . ращению.- времени разряда эквивалентной Ю емкости цепи нагрузки.

Информационный сигнал, например, с пульта оператора (на чертеже. ие показан) поступает на вход ключа 5. Елюч

6 определяет, какую информацию выда- 15 вать на .выход.ячейки, если кеоч 6 закрыт, ка выход поступает информация по цепи коррекции (ключ 5), если кйвч 6 открыт, иа. выход ячейки поступает информация с триггера вне зависимости 20 от наличия корректирующей информации ..

Ключ 7 разрешает выдачу информации иэ ячейки. . Ячейка памяти работает следующим образом.

Управляющий сигнал поступает на вход 14 ключа 3 и кратковременно на вход ключа 16. Вход триггера открывается, а цепь обратной связи кратковременно прерывается, и на выходе триггера устанавливается или сохраняет« ся логический нуль (Вход 8) Цепь обратной связи триггера замкнута при наличии логической"единицы на входе ключа 4. Ири поступлении логической единицы на вход первого элемента

ИЛИ-НЕ 1 триггер устанавливается в единичное состояние, которое запоминается, так как ключ 4 открыт.

Если ключ 6 открыт (Единица на входе) информация с триггера посту- 40 пает в выходную цепь ячейки (ключ 7), если ключ 6 закрыт, s выходную цепь ячейки поступает нуль или еди" ница из цепи коррекции через ключ

5. Информация в триггере может быть 46 изменена только при новом поступлении управляющего сигнала по входу 14 (разрывом цели обратной связи).

Если ключ 4 закрыт (нуль на его входе), при наличии управляющего сигнала на входе 14 единица на выходе триггера сохраняется до окончания сигнала единицы . на входе 8 ключа

3 илн до окончания управляющего сигнала на входе 14. С помощью ключа 7 осуществляется выбор,ячейки приемником информации.

Предлагаемая структура ячейки позволяет создавать устройства различного назначения с низкими требованиями к синхронизации, длительности, форме и амплитуде поступающих на него сигналов, имеющие различные способы управления низкие требования к кабелЬным линиям связи.

Формула изобретении

Ячейка памяти, содержащая два пос-ледовательно включенных элемента ИЛИНЕ к три ключа, первый вход первого элемента ИЛИ-NE подключен через первый клноч к входу ячейки, второй вход первого элемента ИЛИ-НЕ подключен через второй ключ к выходу второго элементаИЛИНЕ, отличающаяся тем, что, с целью расширения области. применения за счет увеличении диапазона управлякнцих сигналов, она содержит два дополнительных ключа, выход второго элемента ИЛИ-ЯЕ через первый и второй дополнительные ключи нодклю" чен к выходу ячейки, а точка соедине« ния дополнительных ключей через третий кюиоч подкюиочена к шине пнтанйя.

Источники информации, принятые во внимание прк экспертизе:

1. Авторское свидетельство СССР

9 367555 кл. Я 03 К 21/00 12.03.73.

2 Авторское свидетельство СССР

У 395904,> кл С 11 С 19/28, 08.01.74.

618796

Составитель Э.Востриков тек е "М.Борисова о кто Д.Мельниченко

Редакто Л.Утехина

Эакаэ 4269/44 Тираа 717 Подпи с ное

ЦЯИИПИ Государственного коиитета СовЕта Министров СССР пс делам изобретений и открытий

113035 Моски " X-35 Р ск наб . 4 5

Филиал ППП Патент, г, Умгщ ц, ул. Проектная, 4