Время-импульсное устройство для умножения

Иллюстрации

Показать всеРеферат

т . 1

ОП ИКАНИЕ:

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реотублмк

"Cn)619927 (6L) Дополнительное к авт. свид-ву

2 (51) М. Кл. (22) Заявлено 08.02. 77 (21) 2449770/18-24

Д 06 Q 7/161 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.08.78.Бюллетень № 30 (45) Дата опубликования описания 04.07.78

Государственный комитет

Совета Министров CGCP оо делам изобретений и открытий (53) УДК 681,335

l (088.8) (72) Авторы изобретения

А. Е.. Волынский, С, А. Рачи и А. А. Смирнов (71) Заявитель. (54) ВРЕМЯ-ИМПУЛЬСНОЕ УСТРОЙСТВО

ДЛЯ УМНОЖЕНИЯ

Изобретение относится к измерительной и вычислительной технике и может быть .применено в аналоговых и аналого-цифро1 вых системах.

Известно множительное устройство вре,мя-импульсного типа, представляющее собой фильтр низких частот, ко входу «оторого в течение заданного временного ин-; тервала периодически подключается одна вз переменньае- входное напряжение, а длительность интервала является другой пе.ременной (Х) . В установившемся режиме работы етого устройства величина пульсаций íà его выходе зависит от постоянной времени фильтра. Наиболее близким к изобретению техническим решением явля» ется время-импульсное устройство дпа умножения, содержащее блок управления, вход которого соединен с первым входом устройства, интегратор, вход которого сое динен через первый ключ со вторым входом устройства и через второй ключ - с выходом блока запоминания, управляющие входы блока запоминания, первого и вто рого ключей соединены с выходом блока управления (2). Цикл работы устройства состоит из следующих операций. В течение временного интервала, длительность которого является первой переменной, происходит интегрирование второй переменной - входного напряжения,К» результат интегрирования суммируется с накопленной устройством ошибкой, запоминается в аналоговой форме и вторично интегрируется в течение постоянного временного интервала, длительность которого равна номинальной постоянной времени интегратора; можно показать, что выходное напряжение устройства поо ле тт -го цикла тт- +.(-Ю" 1 где С ЯС -фактическая постоянная времени интегратора. Очевидно, что вьзходное напряжение устройства тем быстрее прибзтижается к установившемуся значению х и

Оэст. -Г Е у чем менее фактическая постоянная времени Г отличается от Т.

619927

,Илительность по"тоянного временного интервала Т выбирают в соответствии с требуемым масштабом выходного напряжения устройства. При увеличении диапазона изменений переменной х в сторону большего времени величины Т и f также приходится увеличивать. Однако постоянная времени 1 . ограничена сверху, так как с ростом сопротивления масштаб:ного резистора интегратора возрастает влияние входного тока его усилителя на точность интегрирования, а выбор конден« сатора большей емкости с малой абсорЬцией осложняется требованиями габаритов

Целью изобретения является расширение диапазона входных сигналов, В описй- 5 ваемом устройстве это достигается тем, что оно содержит дополнительный интегра« тор, вход которого через дополнительный ключ соединен с выходом основного интегратора, управляющие входы допопнитель 20 ного интегратора и дополнительного кпюча соединены с выходом блока управления, а выход дополнительного интегратора соединен с входом блока запоминания.

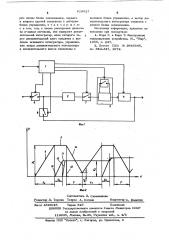

На фиг. 1 представлена структурная 25 схема описываемого устройства; на фиг. 2 « поясняющие его работу временные диаграммы.

Устройство содержит блок 1 управле ния, интегратор 2 и дополнительный ин- зо тегратор 3 блок 4 запоминания, ключи

5 и 6 и дополнительный ключ 7.

В течение интервала Ф у сигнал E, :поступающий на вход интегратора 2 через замкнутый ключ 5, вызывает изменения 35 выходного напряжения данного интегратора (см. фиг. 2, часть 8 кривой), при этом ключи 6 и 7 разомкнуты, а в ин теграторе 3 осуществляется режим сбро-. са, По окончании данного интервала ключ 40

5 размыкается и заканчивается режим сброса интегратора 3, а ключ 7 - замыкается, вследствие чего интегратор 2 вы.полняет функции запоминающего устройся ва, выходной сигнал ц «p " которого 45

Я ф ° преобразуется интегратором 3 в линейно изменяющееся напряжение (см. фиг. 2, части 9 и 10 кривой), Эта часть цикпа длится в течение задаваемого хронизатором интервала t c, по окончании

50 которого ключ 7 размыкается, а на вход синхронизации устройства 4,подается команда на запоминание выходного напряжения интегда3 1„

55 о тора 3, где - Го - постоянная времени данного интегратора. В течение времени, необходимого для запоминания этого напряжения блоком 4, интегратор 3, по- "

60 добно интегратору 2 в предшествующей части цикпа, выпопняет функции промежуточного запоминающего устройства (см. фиг. 2, части 11 и 12 кривой), однако в отличие от интегратора 2, интегратор

3 по окончании соответствующего интервала возвращается в режим сброса (см. фиг. 2, часть 13 кривой); одновременно с этим ключом 6 замыкается до конца цикла на задаваемое блоком управления время Т, в течение которого сигнал отрицательной, обратной связи устройства подается на вход интегратора

2 и интегрируется (см. фиг. 2, часть

14 кривой), Значение выходного напря- жения интегратора 2 по окончании данного интервала равно ошибке, накоплен ной устройством в течение цикла явлется поправ4 °

Сх Г» 1оТ 1 » кой K результатам интегрирования в последующих циклах.

Таким образом, периодическое повторение данного цикла, как и в,известном устройстве, обеспечивает на выходе бло» ка 4

Но в отличие,от известного устройства, для обеспечения сходимости итерационног)о процесса на выходе описываемого устрой. ства требуется обеспечить аппаратурно легко реализуемое условие аЬя .

Пусть, например, t х " Т 100 м/с

1 если при этом в известном требуется обеспечить С 100 м/с, то в описываемом устройстве приемлемы следующие значения: C= 10 м/с, < 10 мlс, t = 1 м/е.

Таким образом, введение новых элемент тов - второго интегратора и допопнитель ного ключа выгодно отличает описываемое устройство от.известного, так как увеличивается его рабочий диапазон. в область большего времени, и следовательно, расширяется сфера его применения.

Формула изобретения

Время-импульсное устройство дпя умножения, содержащее блок управления, вход которого соединен с первым входом устройства, интегратор, вход котррого соединен через первый ипоч со вторыф входом устройства и через второй ключ с выходом блока запоминания, управляю619927

Составитель Л Снимшикова

Редактор Л. Тюрина Техред А. Богдан Корректор С. Ямалова

Заказ 4509/45 Тираж 826 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж34, Раушская наб., д. 4/5 филиал ППП Патент, г. Ужгород, ул. Проектная, 4 шие входы блока запоминания, первого

1 и второго ключей соединены с выходом блока управления, о т л и ч а ю щ е ес я тем, что, с целью расширения диапазона в".одных сигналов, оно содержит дополнительный интегратор, вход которого через дополнительный ключ соединен с выходом основного интегратора, управляюшие входы дополнительного интегратора и дополнительного ключа соединены с

1 выходом блока управления, а выход допопнительного интегратора соединен с входом блока запоминания.

Источники информации, принятые во внимание при экспертизе:

1. Кори Г. и Кори Т. Эпектронные моделируюшие устройства. М., «Мир«, 1955, с. 247.

2. Патент США № 3646545, кл. 340-347, 1972.