Преобразователь угла поворота вала в код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (М) 619842 (61) Дополнительное к авт. саид-ву

2 (51) М. Кл. (22) Заявлено 24,10,75 (21) 2184437/18-24. С1 08 С 9/04 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.08.78Бюллетень Ph 30 (46) Дата опубликования описания 03.07.78

1 есударстееиный иеметет

Совета Миииетреа СССР ае делам изебретеиий и еткрытий

681.325 (088,8) Г. A. Калинин, С. В. Бабаев и А, Н. Храбров (72) Авторы изобретения

Харьковский институт радиоэлектроники и Всесоюзный научно-исследовательский институт по охране soll (71) Заявители (54) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД

Изобретение относится к области автоматики и вычислительной техники и может быть использовано дли связи аналоговых источников информации с цифровым вычислительным устройством. 5

Известен преобразователь угла поворота вала в код, содержаший синусно-косинусный датчик угла, подключенный через блок фазосдвигаюших цепочек к компара1О торам, выходы которых соединены с блоком преобразования временных интервалов B код $1), Недостатком такого преобразователя является большая погрешность, вызванная нестабильностью блока фазосдвигаюших цепочек..

Известен также преобразователь, содержаший синусно-косинусный датчик угла, подключенный к селектору октанов, 20 тангенсный цифроаналоговый преобразователь, компаратор, соединенный с блоком управления, регистры старших и младших разрядов кода $2). Недостатком этого преобразователя является большая ме- 25 тодическая погрешность и сложность построения преобразователя.

Наиболее близким техническим решением к данному изобретению является преобразователь yrna поворота. sana в код, содержаший синусно-косинусный дат чик угла, каждый из выходов которого через два последовательно соединенных кшоча подключен к переключателю, соединенному через компаратор с блоком управления, выходы которого подключень1 к регистру старших разрядов, формирователю кодов младших разрядов и к уп» равпяюшим входам ключей, выходы регистра старших разрядов подключены к другим входам блока управления, а выходы формирователя кодов младших разрядов подключены к управляющим входаМ двух масштабных блоков, другие входы которых соединены с выходами пятого и шестого ключей соответственно, седьмойи восьмой ключ, два сумматора, инвертот. Я

Недостатком такогр преобразоватедя является выполнение его масштабных блоков из последовательно вкпюченных кон6199

42 4 а ВтОрой яВлиется ВыхОдным и служит для записи и хранения младших разрядов кода угла

Перед началом цикла преобразования ключи 15-22 разомкнуты, все регистры обнулены. В моментto сигналом с блока

12 управления ключи 15, 16, 17, 18 эа мыкаются и выходные напряжения анало говйх запоминающих элементов 2-5. повторяют соответствующие выходные напряжения датчика 1. В. момент1 выходные напряжения датчика 1 достигают своих, пиковых значений, ключи 15-18 размыкаются, и на выходах. запоминающих элементов 2-5 и сумматоров 7, 8 сохраняются напряжения постоянного тока, пропорц««ональные синусу и косинусу угла поворота. Путем последовательного под-. ключения входа компаратс ра 11 через . ключ 23 к выходам сумь аторов 7 и 8 по полярности напряжений оп теделяются два старших Р «И Р я разряд& ВыхОднОГО кО да угла, Код старших разрядов записывается в регистр 13.

В следующих тактах производится фор мирование младших двоичных разрядов

P> - @.„Выходного кода, представляющих

«« угол д. = — «чт.-— я 7 где ит - номер квадранта, Или Угла Ос. «.т спРаведливо соотношеиие денсаторов, что приводит к нетехнологич ности всего преобразователя и сложнос тиэ

Цельто изобретения являетси упрощеwe преобразователя.

Это достигается тем, что в предлагаемый преобразователь введены четыре запомин аощих элемента, а масштабные олоки выполнены из последовательно включейных резисторов, общая точка первых двух ключей через последовательно сое- «О диненные первый запоминающий элемент, седьмой ключ и второй запоминающий элемент. подключена к одному входу пер«; вого сумматора, а через инвертер — к входу шестого ключа, общая точка втоptIx двух ключей через последовательно соединенные третий запоминающий элемент, Восьмой ктпоч и четвертый запоминающий элемент подключена к одному Входу второго сумматора и к входу пятого ключа, выходы масштабных блоков подключены к другим входам сумматоров, вы- ходьт которых соединены с входами переключателя.

Т акое устройство позволяет исктпочить блоки прецизионных конденсаторов с нестандартными номиналами, что повышает . его технологичность.

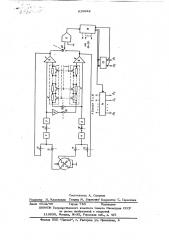

Счруктурная схема преобразователя представлена на чертеже.

Преобразователь содержит синусно-косинусный датчик 1 угла, аналоговые за= поминающие элементы 2, 3, 4 и 5, инВертор 6, суммат ры 7 и 8, масштабные блоки 9 и 10 резисторов, компаратор 11, M бпОк 1 2 уттравленияр регистр 1 3 старших разрядов, форм««рователь 14 кодов младших разрядов„ключи 15-22, переключатель 23.

Каждый блок 9 и 10 резисторов пред-,«л стаВпяет сОбой IIeEIoчку последОВательнО еоединенттых резисторов определенных намина Ioa с ларалпепычо соединенными кщочам«. И разомкнутом состоянии находится только Один топоч, а Остальные замкну- i5 тые и шунтируют соответствутощие резисторы, номиналы которых, пропорпиональIIIItg (Й/2 «), ГДе 4 3, 4, 5

««(«« -КОЛИЧЕСТВО РаЗРЯДОВ ВЫХОДНОГО кода). Компаратор 11 является индикатором напряжения, действующим на его Входе. Блок 12 управления обеспечивает необходимое взаимоденствие

Всех блоков преобразователя. Формирователь 14 кодов младших разрядов ттредстав- 55 ляет собой комбинапито двух Взаимодействующих регистров, один из которых является сдвигающим и служит для управления ключами блоков 9 и 10 резисторов, (с«я pQ + Р> + ° + «g (1)

g2 I $ i)3 т" /fan-««, !.

СЬределение младших разрядов кода угла производится путем д««скретного по ворота против часовой стрелки вектора Ч, представленнОГО своими проекциями В < Н Uy, до совпадения с выбранной координатной осью. При этом, если после пробного поворота вектора Й на угол 9/ 2 выбранная проекция не изменила свой знак, то /. ««1, В противном случае /5 < " О.

Йт«я нахождения разряда /Ь, соот-. ветствующего весу ««/2« необходимо осуществить первый пробный поворот вектора 17 на угол Я/2 в соответ -Х ствии с уравнениями

Я

xj х«- ICOS 4, Ц14-4sjn — i

Я

=Ц "« (;Qg . -U ° а «ц )р

24 Р которые после математических преобразований можно записать

Я

Ц « = «-1 У g

Я . Замыкаются ключи 21 и 22, затем кшочи 19 и 20 размыкаются, а ключи

16 и 18 замыкаются. В результате выходные напряжения сумматоров 7 и 8 переписываются в запоминающие эпементы

3 и 5 для использования в следующем такте работы нреобразоватепя.

Если после поворота вектора на угоп

C/4 проекция изменила свой знак, то

/Ь = О, и старые значения напряжений на запоминающих элементах 3 и 5 сохраняются в следующем такте работы йреобраэователя при нахождении значении paaf ряда P .

Аналогичным путе м определяются и все остальные Р разряды выходного, кода»

Такой преобразователь угла поворота вала в код, осуществляющий формирование мпадших разрядов кода угла путем поразрядного взвешивания выходных сигналов синусно-косинусного датчика угла с помощью управляемых блоков резисторов, двух сумматоров и одного компаратора, досгаточно прост и обладает высокой точностью.

Формула изобретения

Преобразователь угла поворота вала в код, -содержащий синусно-косинусный датчик угла, каждый из выходов которо5

ro через два последовательно соединенных ключа подключен к переключателю, соединенному через комларатор с блоком управления, выходы которого подключены

K регистру старших разрядов, формирователю кодов младших разрядов и к управляющим входам ключей, выходы регистра старших разрядов подключены к другим входам бйока управления, а выходы формирователя кодов младших разрядов подключены к управглюшим входам двух мас-, штабных блоков, другие входы которых соединены с выходами пятого и шестого ключей соответственно, седьмой и восьмой ключ, два сумматора, инвертор, о т и и ч а ю ш и и с я тем, что, с целью упрощения преобразователя, в него вве дены четыре запоминающих элемента, а масштабные блоки выполнены иэ последователыю включенных резисторов, общая 5 точка первых asyx ключей через ггосггеаовательно соединенные первый запоминающий элемент, седьмой ключ и второй запоминающий элемент подключена к одному входу первого сумматора, а через зо инвертор — к входу шестого ключа, общая точка вторых двух ключей через последовательно соединенные третий запоминающий элемент, восьмой кпюч и четвертый заломинаюший элемент подключена з» к одному входу второго сумматора и к входу пятого ключа, выходы масштабных блоков подключены к другим входам сумматора, выходы которых соединены. с входами переключателя.

Источники информации, принятые во внимание при экспертизе:

1, Патент СШЯ No 3505669, кп 340-347, от 07.04.70.

2. Г. Шмид, Устройство и принцип действия преобразователей аналоткод, перевод ГОНТИ No. 4211(71), с. 227228. рис, 1У.18, 3. Г. Шмид. Устройство и принцип

5п действия преобразователей аналог-код, перевод ГОНТИ N 4211(71), с. 258265, рис. 1У.37.

619942

Составитель А. Смирнов

Редактор H. Каменская Техред М. Борисова Корректор С. Гарасиник

Заказ 4512/46 Тираж 7 63 Подписное

UHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаа наб., p. 4/5

Филиал ППП Патент ° r. Ужгород. ул Проектная, 4