Импульсный частотный дискриминатор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Сеюэ Соаетсиик

Социанистичесиик

Республик (и) 621066

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительнбе к авт. свид-ву(Sl) N. Кл. (22) Заявлено 130575 (21) 2133461/18-21 с присоединением заявки,ВВ 03 2) 13/00

Государственный комитет

Совета й1ннистров СССР ао кедам изобретеиий . и открытий (23) Приоритет (43) Опубликовано 250878.Бюллетень 36 31 (45) дата опубликования описания 110778 (53) УДК 621,374.3 (088.8) P2) Авторы изобретения

Е.В.Стриженов и Е.Г»яковлева (71) Заявитель (54 ) ИИИУЛЬСНЫЙ ЧАСТОТНЫЯ ДИСКРИМИНАТОР

Изобретение относится к импульсной технике.

Известен импульсный частотный дискриминатор, содержащий RS -триггеры, на входы которых поданы входные сигналы, два логических элемента И, входы которых подключены соответственно к выходам и входам Ъз -триггеров

Однако такой дискриминатор не обладает достаточной надежностью.

Наиболее близким по технической сущности к предлагаемым является частотный дискриминатор, содержащий два входных логических элемента И, первые входы которых соединены с входными шинами и первыми входами вы« кодных трехвходовых логических элементов И, а выходы входных логических элементов И соединены с первыми входами двух 3К-триггеров, вторые входы которых подключены к шине синхросигналов, третьи входы 3К-триггеров перекрестно соединены с входными шинами, а их прямые выходы соединены с вторыми входами выходных трехвходовых логических элементов И (2).

Однако этот дискриминатор также не обеспечивает достаточной надежности»

Целью изобретения является повышение надежности работы.

Это достигается тем, что в дискриминаторе, содержащем два входных логических элемента И, первый вход каждого из которых соединен с одной из входных шин и первым выходом соответствующего выходного трехвхсдового логического элемента И, а выход - с первым входом соответствующего 3К-триггера, вторые входы которых подключены к шине синхросигналов, третьи входы перекрестно соединены с входными шинами, а их пряаые выходы соединены с вторыми входами выходных трехвходовых логических элементов И, третий вход первого трехвходового логического элемента И соединен с вторым входом первого входного логического элемента И н инверсным выходом второго 3К -триггера, а третий выход второго выходного трехвходового логического элемента И со,единен с втщиаи входом второго вход- ного логического элемента И и инверсным выходом первого JK-триггера.

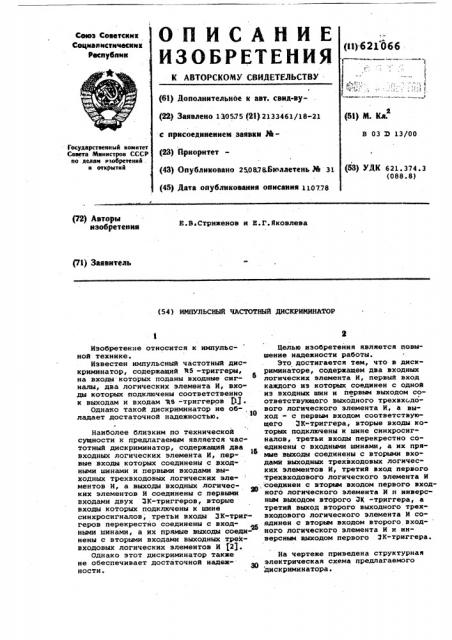

На чертеже приведена структурная электрическая схема предлагаемого дискриминатора.

621066

) л

ЦНИИПИ - Заказ 4673/50 Тираж 1086 Подписное

Филиал ППП Патент, г.ужгород, ул.Проектная,4

Дискриминатор содержит первый и второй входные логические элементы И

1 и 2; первый и второй 3К-триггеры

3, 4 и первый и второй выходные трехвходовые логические элементы И

5 и 6."

На входные шины 7 и 8 поданы дисхриминируемые сигналы У» и Fg, на мину 9 подан сигнал синхронизации.

Выходные сигналы снимаются с выходов

10 s 11 °

Рассмотрим работу устройства для I0 первого случая.

Предположим, что 3К-триггеры находятся в состоянии 0, 1 .

Импульс частоты F», который поступает иа входную шину 7 после при- 35 хода синхронизирующей частоты переведет 3К-триггер 1 в состояние 1

Второй 3К-триггер своего состояния не меняет. Все последукзцие импульсы частоты F будут проходить на выход рО

10 устройства.

С приходом импульса частоты F по импульсу синхронизирующей частоты, первый 3К-триггер 3 прейдет в состояние 0, но на выход 11

25 импульс F4 не пройдет.

Следующий импульс F» опять переведет дискриминатор в состояние 1, э ° 1ВФ

Во втором случае, когда частоты и > "» дискриминатор из состояния О ., 1 . переходит в состояние 0, 0 . Первый 3Ê-триггер 3 своего состояния не меняет.

Все последующие импульсы часто35 ты Гц будут проходить на выход 11.

С приходом импульса частоты 5» дискриминатор из состояния 0, О ,перейдет в состояние О, 1, ио следующий импульс частоты Г опять переведет дискриминатор в состояние О, 0 . В случае равенства частот F»"- дискриминатор переХодит из состояния 1, 0 и 0, 1 в состояние 1 °, 1 и 0, 0 и обратно.

Если частоты F» и Fg следует пачками, на выходах 10 и 11 импульсы отсутствуют. Это указывает на стабильность работы схемы при девиации частот.

Формула изобретения

Импульсный частотный дискриминатор, содержащий два входных логических элемента И, первый вход каждого из которых соединен с одной из входных шин и первым входом соответствующего выходного трехвходового логического элемента И, а выход - с первым входом соответствующего 3К-триггера, вторые входы которых подключены к шине синхросигналов, третьи входы перекрестно соединены с входными шинами, а их прямые выходы сое-. динены с вторыми входами соответствующих выходных трехвходовых логических элементов И, о т л и ч а юшийся тем, что, с целью повышения надежности работы, третий вход первого трехвходового логического эле-. мента И соединен с вторым входом первого входного логического элемента

И и инверсным. выходом второго

ЗК-триггера, а третий вход второго выходного трехвходового логического элемента И соединен с вторым входом второго входного логического элемента И и инверсным выходом первого

3К-триггера.

Источники информации, принятые во внимание при экспертизе:

1. Патент США я 3735324, кл. 328-15, 07.06.72.

2 ° Заявка Японии Ф 49-27058, кл. 110 33 5, 15.07.74.